1.为什么要initialization ?

本节介绍device的initialization

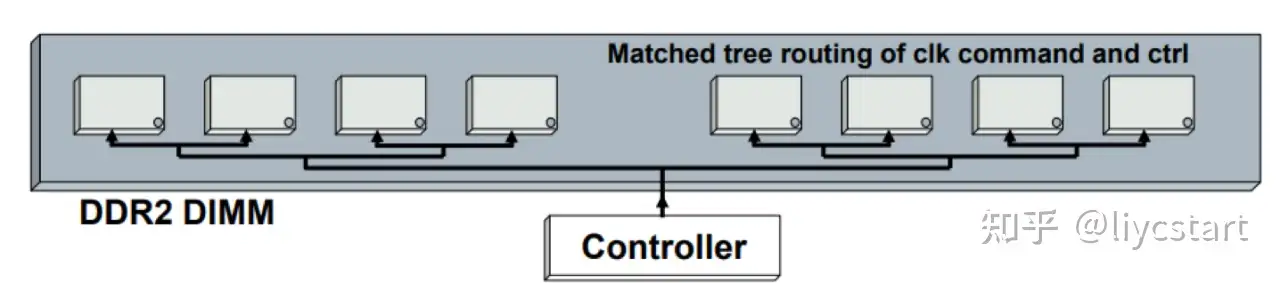

从上节的device的结构可看出DIMM的两面有16个颗粒,颗粒的组织结构有T型(CA/CLK)。

T型 拓扑

T型 拓扑

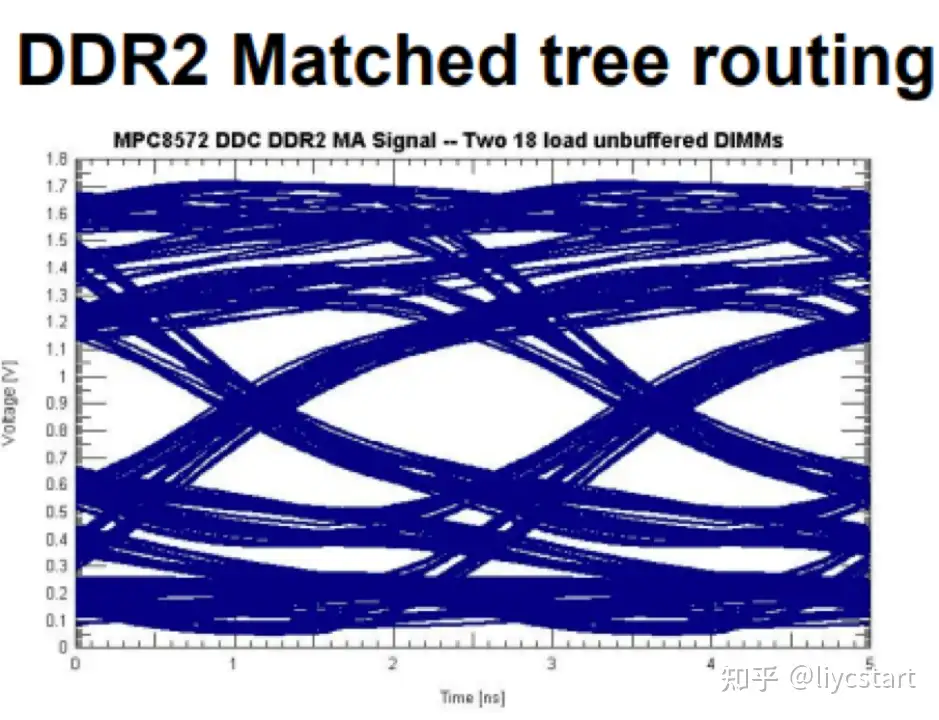

T型拓扑的眼图

T型拓扑的眼图

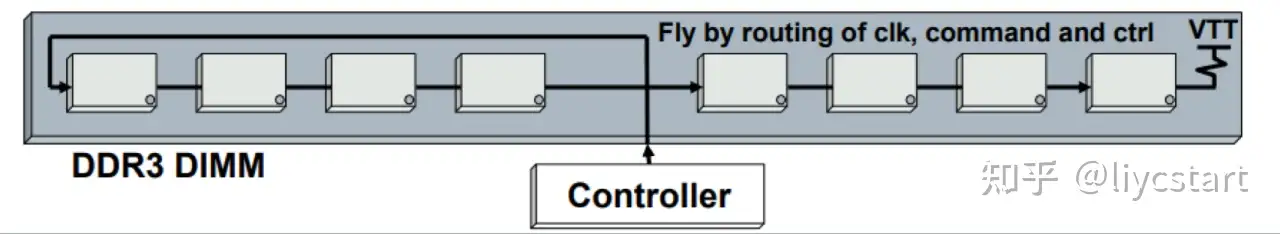

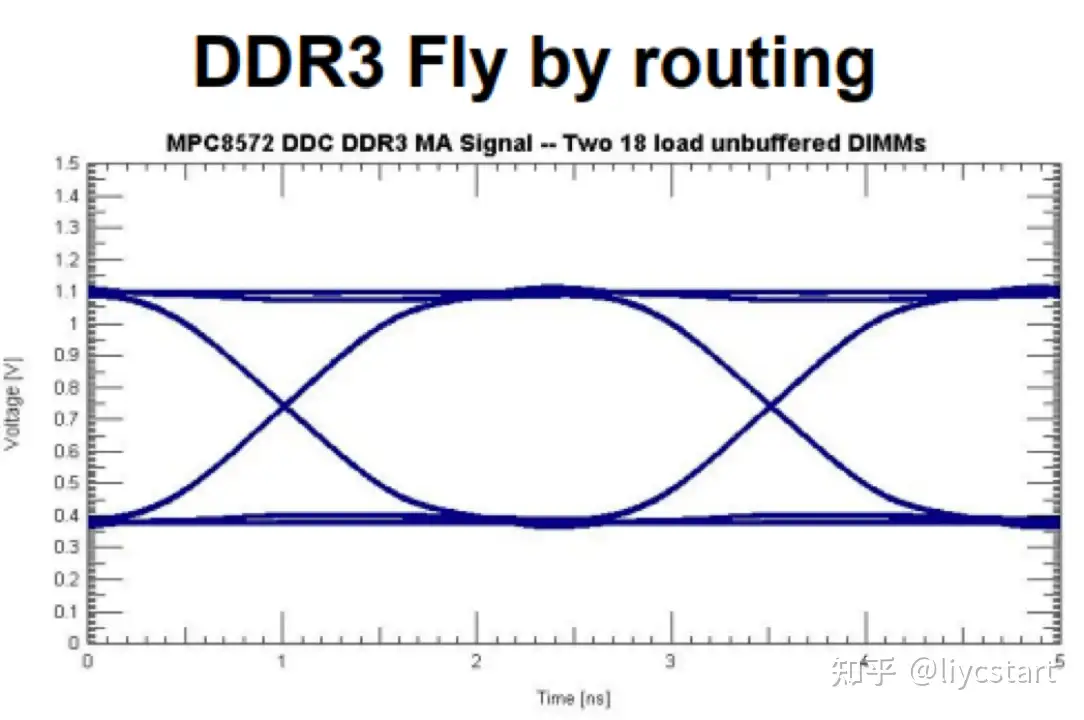

因为信号完整性问题,把T型结构调整为fly-by的结构。CA和clk在PCB布线时穿透1个个DRAM,对于每个DRAM,data skew是不同的,因此,需要做write leveling,来de-skew每个DRAM的skew。

fly-by型拓扑

fly-by型拓扑

fly-by型拓扑的眼图

fly-by型拓扑的眼图

2.initialization 的流程

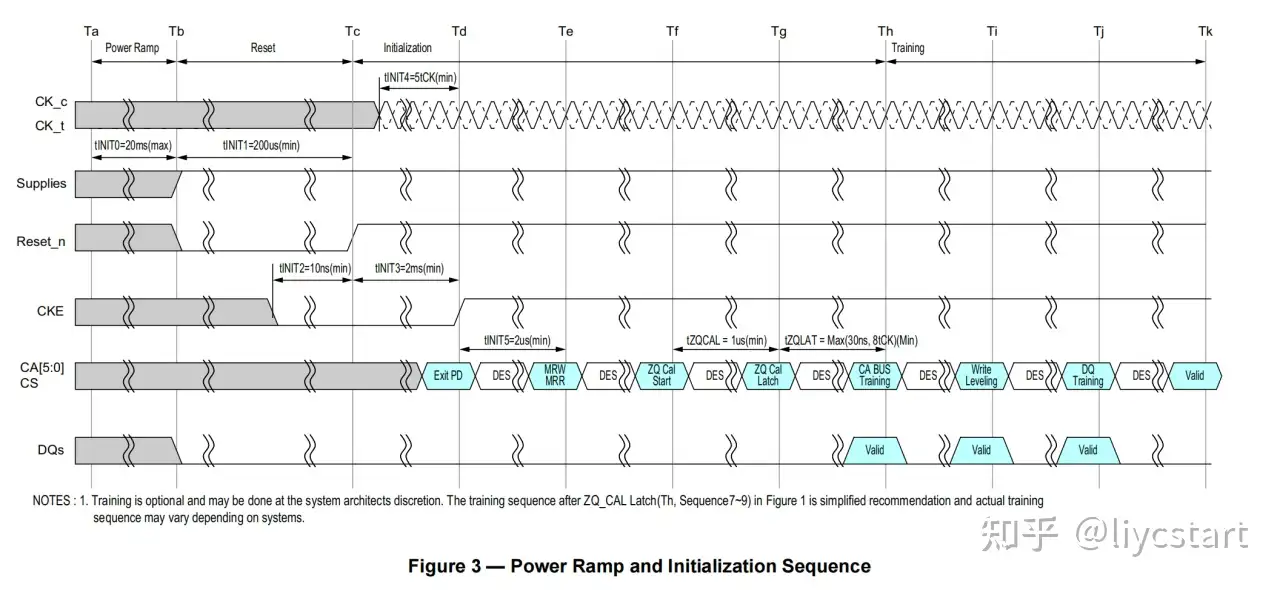

可以从JESD209-4的LPDDR4的协议规范可以详细看到initialization的流程:

initialization

initialization

从上电到 对DRAM读写前,需要进行以下的配置和相位调整过程:

1. 上电

2. MRW(mode register write)

------------initial------------

3. ZQ cal:CA 、DQ 各线的ODT调整阻值,为了更好的信号质量

4. CA bus training:CA 、CLK相位 (CA bus training)

------------training----------

5. Write leveling:DQS 、CLK相位

6. DQ training:DQ training(controller读,写DRAM的眼图中心)

无论是initial 还是 training的过程,都是为了找出在controller和DRAM间进行数据的读写时最优信号的位置,而进行的探索性调整相位的过程。以下详细介绍各步骤。

2.1上电

注意上电电压是否符合颗粒要求,reset的时序是否满足颗粒要求(如上图复位的保持时间tINIT1>=200us)。

2.2 MRW(可以通过controller 或者phy 对颗粒的模式寄存器配置)

2.3 ZQ calibration:

2.3.1 ZQ 校准的目的

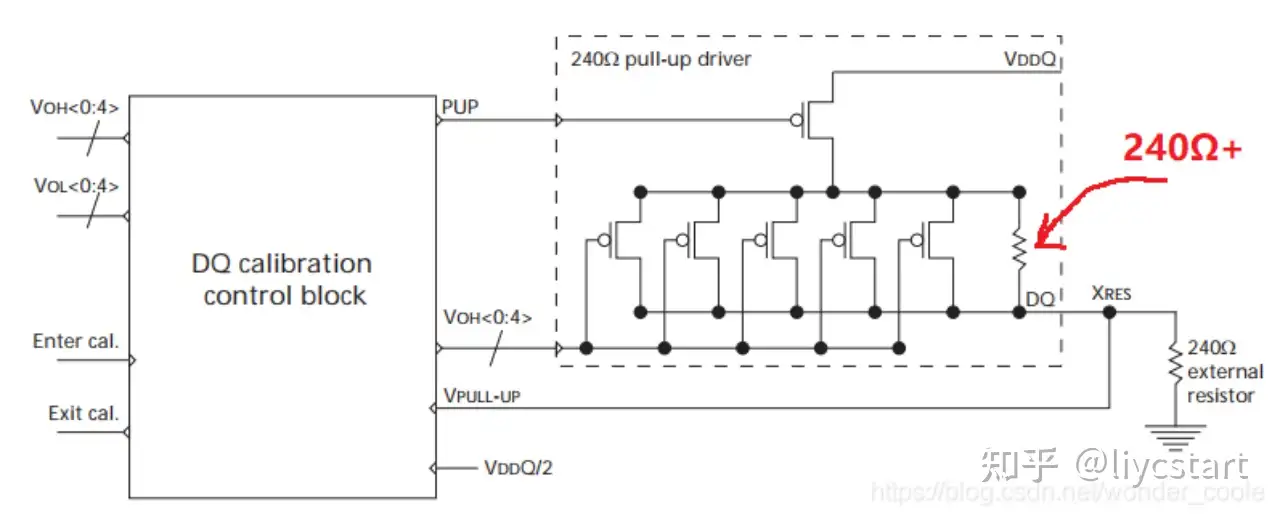

LPDDR4的ZQ pin, 用来外接一240Ω±1%上拉电阻。LPDDR4将其作为参考电阻,用来校准DRAM内部的240Ω电阻。因为芯片内部的240欧电阻是由CMOS构成,由于CMOS的天然特性,造成该电阻会随着PTV(制程,温度和电压)变化,因此必须对其进行校准。

ZQCAL的4个作用:

1) 输出上拉校准,即校准输出电压VOH PU-Cal (Pull-up Calibration VOH Point)

2) 输入下拉驱动强度及接收终止电阻的校准 PDDS (Pull Down Drive Strength and Rx Termination)

3) DQ-ODT (DQ ODT Value)

4) CA-ODT (CA ODT Value)

2.3.2 ZQ 校准的效果:

用外部的参考电阻对内部CMOS电阻阻值进行校准。

只有对DQ Pad内部的上下拉电阻网络中的每个电阻进行校准,才能满足高频下信号完整性需求,这就用到了连接在ZQ Pad 外部的240Ω±1%参考电阻。校准的前提是,我们认为该外部参考电阻不会随着环境变化,在任何条件下都是标准的240Ω。DRAM内部对每个240Ω电阻进行校准时都会共用该外部参考电阻,因此每个电阻是分开进行校准,在时间上不能重叠。

ZQ calibration

ZQ calibration

图2.3.2 ZQ校准电路

其中左侧方框为校准控制模块,内部包含ADC, 比较器,择多滤波器(majority filter)。图中VDDQ/2作为参考电压,有DRAM内部产生。图中最右侧为一个近似电阻(approximation register,是polyresistor), 比240Ω稍大。和该240Ω+电阻并联的有5个P Channel device(如原文所述),通过控制其导通个数,来使其最终等效电阻最终等于240Ω。

2.3.3校准过程

如下:

收到ZQ校准命令后,PUP会被驱动为低电平,使和VDDQ连接的PMOS开关打开

校准控制模块通过调整VOH[0:4], 来使不同的P Channel device导通

比较VPULL-UP和VDDQ/2的电压,当二者相等时,DQ上下两侧的电阻相等,均为240Ω,校准完成

记录下该电阻的VOH[0:4]的值

对每个上拉电阻(各个DQ引脚,共用1个ZQ 引脚的240欧电阻,时间上逐个)进行校准,记录下每个电阻对应的VOH[0:4]值。

下拉电阻校准过程类似,不多赘述。不同的是和240Ω+电阻并联的是N Channel device。

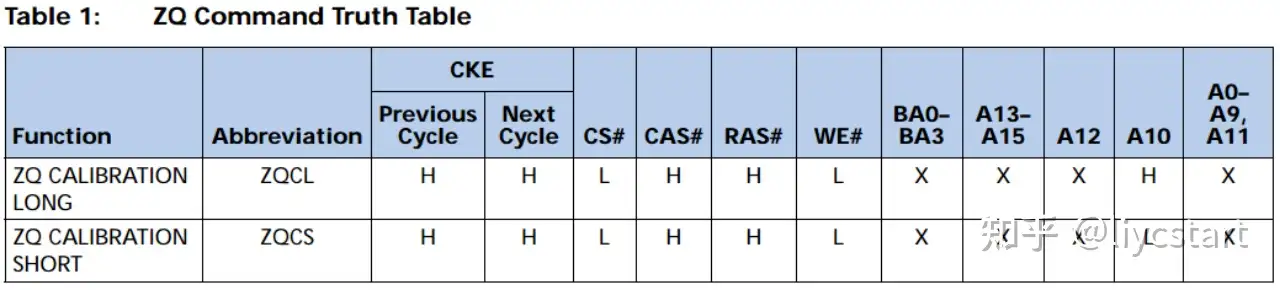

关于ZQ校正有两个命令ZQCL (ZQ CALIBRATION LONG )和ZQ CALIBRATION SHORT (ZQCS)

ZQCL主要用于系统上电初始化和器件复位,一次完整的ZQCL需要512个时钟周期,在随后(初始化和复位之后),校准一次的时间要减少到256周期。

ZQCS在正常操作时跟踪连续的电压和温度变化,ZQCS需要64个时钟周期。

2.4 CA bus training

在fly-by拓扑结构中,发送MRW命令(training模式)

CA bus training的2个作用 :

1) 校准设备内部的VREF

2) 调整CS/CA 与CK的相位关系

直到命令总线CA training结束,设备时钟速率才可以高于tCKb ,否则可能无法正常校准和调整。

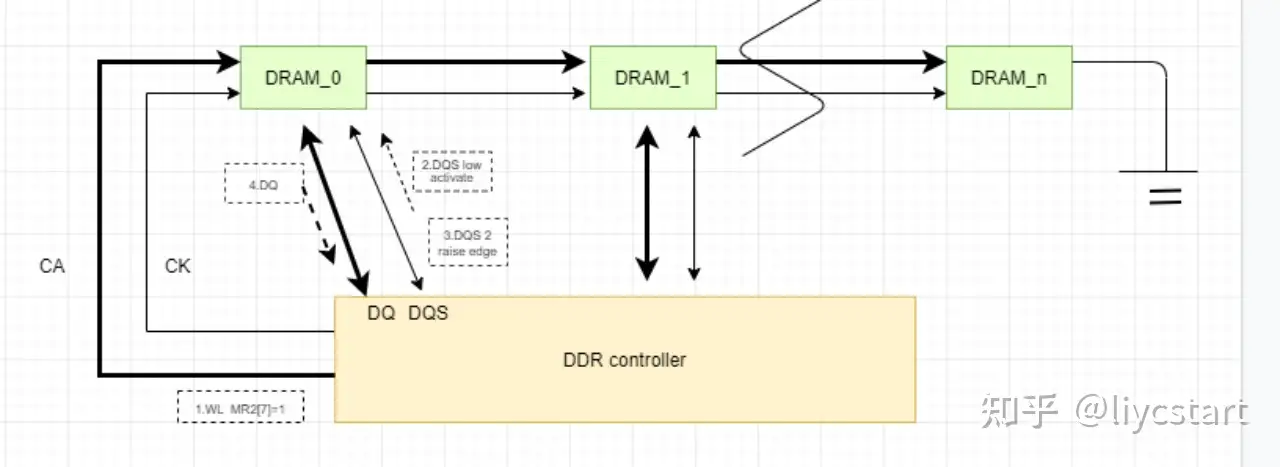

2.5 write leveling (写平衡)

1)背景原因: 从DDR3开始采用了fly-by的结构(为什么采用fly-by结构,查看Fly by Rooting Topology)(多个DRAM放置在PCB上时(或多个die),地址线,控制线,时钟线采用fly-by方式进行布线,DQ,DQS和DMI还是采用点对点的布线方式),CLK到达菊花链的各个DRAM die的时间是不一样的。

2)解决方法:为了解决DQS和CLK的edge alignment的问题,Write leveling作为业界标准解决方案,来解决PCB布线造成的时序问题

MC(Memory Controller)通过调节发出DQS的时间,来让各个DIE的DQS和CLK对齐,起到补偿skew的作用。

3)怎么做:

Write Leveling的基本过程是,DDR进入Write Leveling后,

用DQS的上升沿采样CLK信号的状态,

然后将采样结果通过DQ pin 反馈给MC(DRAM内部MicroController),

MC根据收到的反馈结果后调整CLK-to-DQS的关系,

将这个过程不断重复,直到training成功。

LPDDR4的DQ[7:0]传输DQS[0]的反馈结果,DQ[8:15]传输DQS[1]反馈结果。

也就是说LPDDR4的两个channel要独立的做Write Leveling,每个channel的16比特也要分两个byte lane来做。

LPDDR4的Write Leveling的具体过程如下:(可查看DDR 规格)

1) MC设置MR2-OP[7]使LPDDR4进入Write Leveling模式

2) 一旦进入Write leveling模式,在tWLDQSEN时间后,MC必须驱动DQS到低电平

3) 在tWLMRD时间后提供第一个DQS信号输入。tWLMRD是和不同的MC有关

4) 由于第一个DQS沿不稳定,所以DRAM或许能抓到第一个DQS沿,也可能抓不到,因此MC每次必须提供两个连续的DQS脉冲。每次用DQS的沿去采到时钟的电平,DRAM会在tWLO时间后异步的通过所有DQ的变化来反馈给MC(修改DQS的相位直到某个相位可以满足,反馈的电平从0变为1的迁移,此时可以认为是满足相位要求,退出WL)

5) MC参考DRAM提供的反馈结果,来增到或减小DQS_t and/or DQS_C的延时设置

6) 重复第4到第5步,直到合适的DQS_t/DQS_c延时建立

7) 通过设置MR2-OP[7]=0, 退出Write-Leveling模式

其中第4步的判断标准是:DQS上升沿去采样到CLK电平,发现迁移(由之前的0变为1)

详细解释如下:

Write Leveling的功能是调整DRAM颗粒端DQS信号和CLK信号边沿对齐;调节过程描述:DDR控制器不停地调整DQS信号相对于CLK的延迟,DRAM芯片在每个DQS上升沿采样CLK管脚上的时钟信号,如果采样值一直低,则会将所有的DQ[n]保持为低电平来告知DDR控制器,tDQSS(DQS, DQS# rising edge to CK, CK# rising edge,在标准中要求为+/-0.25 tCK。tCK为CLK时钟周期)相位关系还未满足,如果发现在某个DQS上升沿,采样到此时的CLK电平发现了迁越(由之前的低跳变为高),则认为此时DQS和CLK已经满足tDQSS,同时通过DQ[n]向DDR控制器发送一个高,表征一个写均衡成功,同时DDR控制器会锁住这个相位差。这样,在每个DRAM端,看到的CLK和DQS信号都是边沿对齐的。

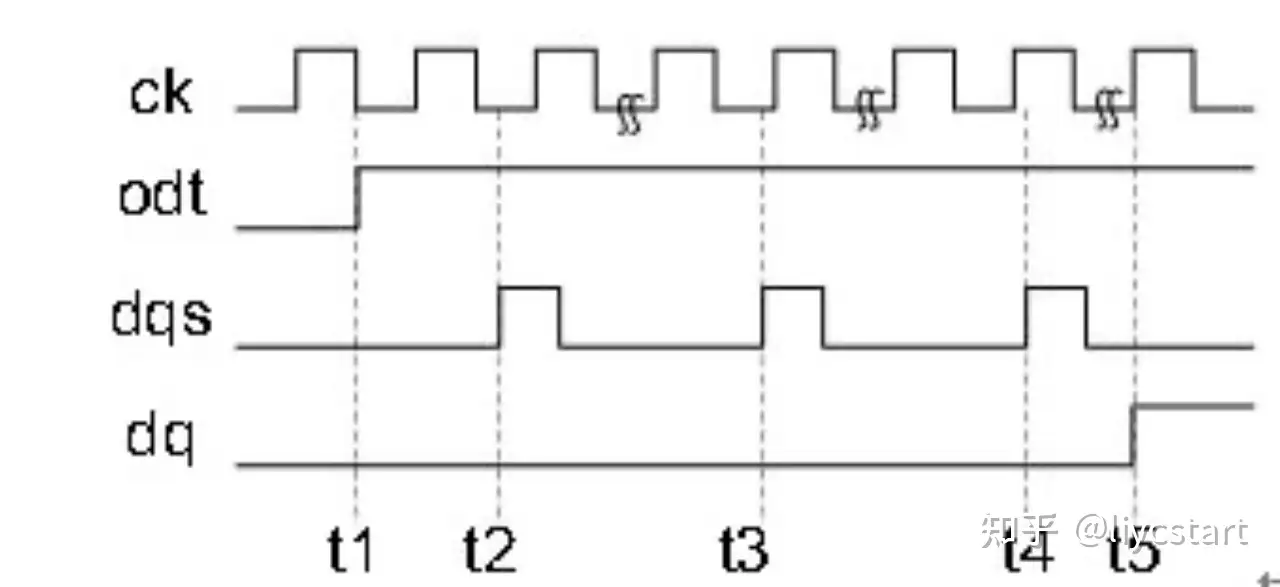

参考DDR3标准的写入均衡图,写入均衡的修调过程:

t1:将ODT拉起,使能on die termination;

t2:等待tWLDQSEN时间后(保证DQS管脚上的ODT已设置好),DDR控制器将DQS置起;DDR memory在DQS上升沿采样CK信号,发现CK=0,则DQ保持为0。

t3:DDR控制器将DQS置起;DDR memory在DQS上升沿采样CK信号,发现CK=0,则DQ仍然保持为0。

t4:DDR控制器将DQS置起;DDR memory在DQS上升沿采样CK信号,发现CK=1,则等待一段时间后,DDR memory将dq信号置起。

采取以上策略的原因:对于DDR controller来说,其无法测定clk边沿和dqs边沿的绝对位置,故采用了不断调整dqs delay,在dqs上升沿判断clk从0到1或1到0的一个变化,一旦检测到变化,则写入均衡停止。

2.6 DQ training

DQ有多bits,同步到到接收方,就需要调整好DQS与CLK的相位。有以下3步:

1. MPR Pattern Write

2. Read Centering

3. Write Centering

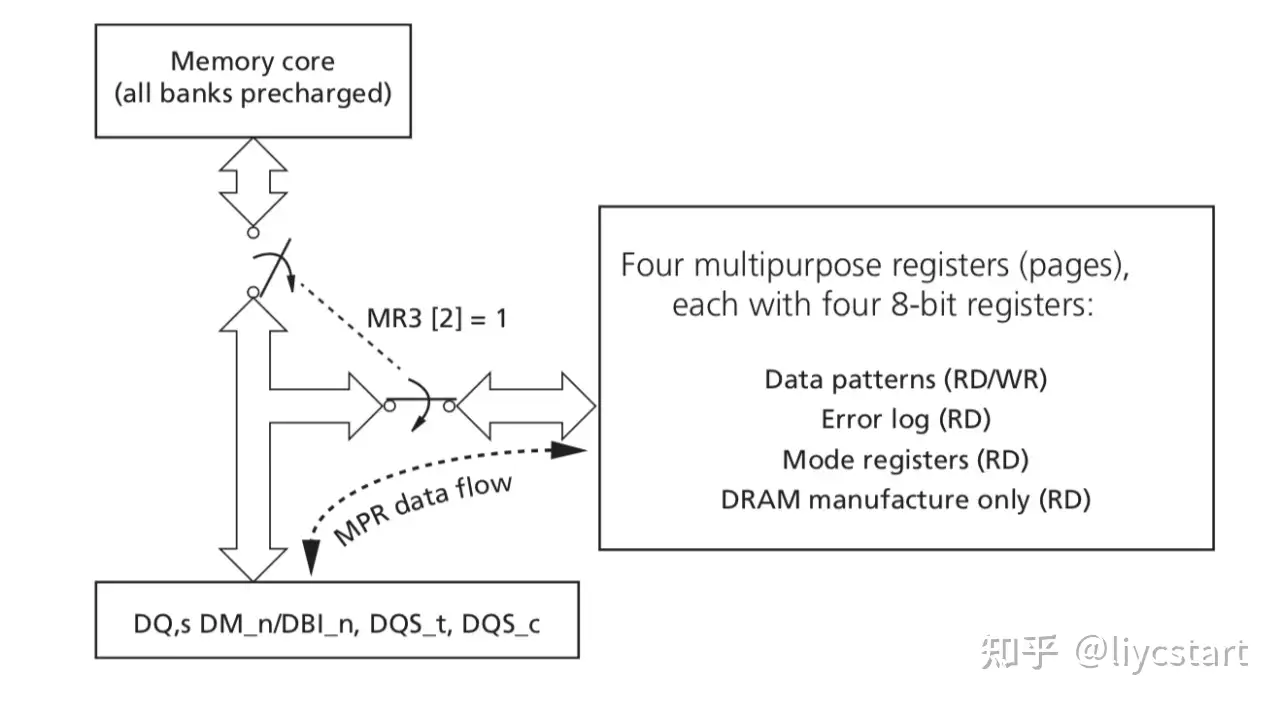

2.6.1读写切换到4个MPR可编程寄存器:

DDR4 DRAM 包含4个 8 位可编程寄存器,称为 MPR 寄存器,用于 DQ 位训练(即读写居中)。

通过设置模式寄存器 MR3[2] = 1 启用 MPR 访问模式。

启用此模式后, DRAM 的 READ 和 WRITE 的发送(DQ/CA),被转移到多用途寄存器,而不是存储区。

2.6.2读中心化(为了使ddr controller/phy 的读捕抓电路在数据眼图的中间获取数据)

1) 切到MPR

2) 然后启动连续的 READ 流, 存储器返回在上一个 MPR 模式写入步骤中写入的模式。 假设这种模式是交替的 1-0-1-0-...

3) 在读取过程中,内部读取捕获电路要么增加或减少内部读取延迟寄存器,以找到数据眼的左右边缘。

4) 当检测到眼图边缘时,读取延迟寄存器会被适当设置,以确保在眼图中心捕获数据。

5) 对每个 DQ 数据位重复上述步骤

2.6.3写中心化(为了使 DRAM的write strobe edge在写数据的中间,把数据写到DRAM中)

1) 启动连续的 WRITE 和 READ 流

2) 逐渐改变数据位的写入延迟

3) 将读回的数据与写入的数据进行比较

3.周期性校准

在网络交换机或路由器等设备中,在其运行过程中可能会有电压和温度的变化。为了保证信号的完整性和数据访问的可靠性,在初始化和读写训练时训练的一些参数必须重新运行。内存控制器和PHY ip通常提供以下两个周期性校准过程。

•Periodic ZQ -也被称为ZQ校准短(ZQCS)。它用于定期运行ZQ校准,以调整前面描述的240Ω电阻。

•Periodic Read Centering —— 重新计算读延迟和其他读相关参数

启用周期性校准是可选的,因为如果您知道您的设备将部署在稳定的温度条件下,那么初始ZQ校准和读写training就足够了。

通常,内存控制器或PHY允许您设置一个计时器,并通过它们的寄存器使能周期性校准。一旦定时器被设置,定时校准将在每次定时器过期时运行.

转LPDDR4x 的 学习总结(6) - initialization & training - 知乎 (zhihu.com)

标签:training,电阻,DQS,initialization,校准,ZQ,DRAM,LPDDR4x,DQ From: https://www.cnblogs.com/RZQYSQ/p/16870486.html