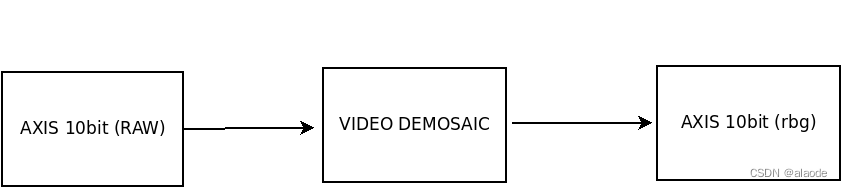

功能

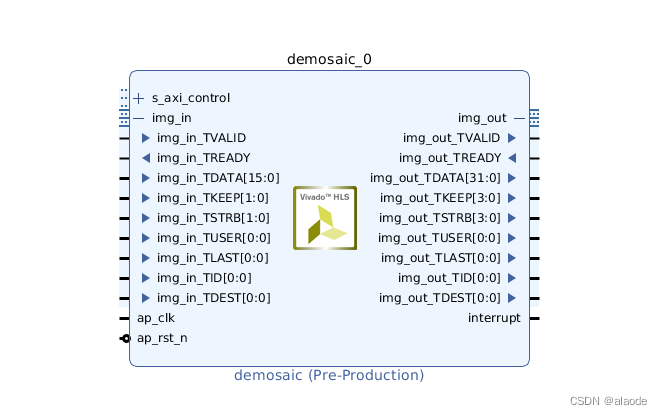

1. 单axi-stream 接口输入(10bit raw输入),axis输出(rgb10bit输出)。

![]() 编辑

编辑

2. 使用xilinx hls 编写。

![]() 编辑

编辑

3. 配置寄存器有

#pragma HLS INTERFACE s_axilite port=height //宽

#pragma HLS INTERFACE s_axilite port=width //高

#pragma HLS INTERFACE s_axilite port=cfa //CFA pattern

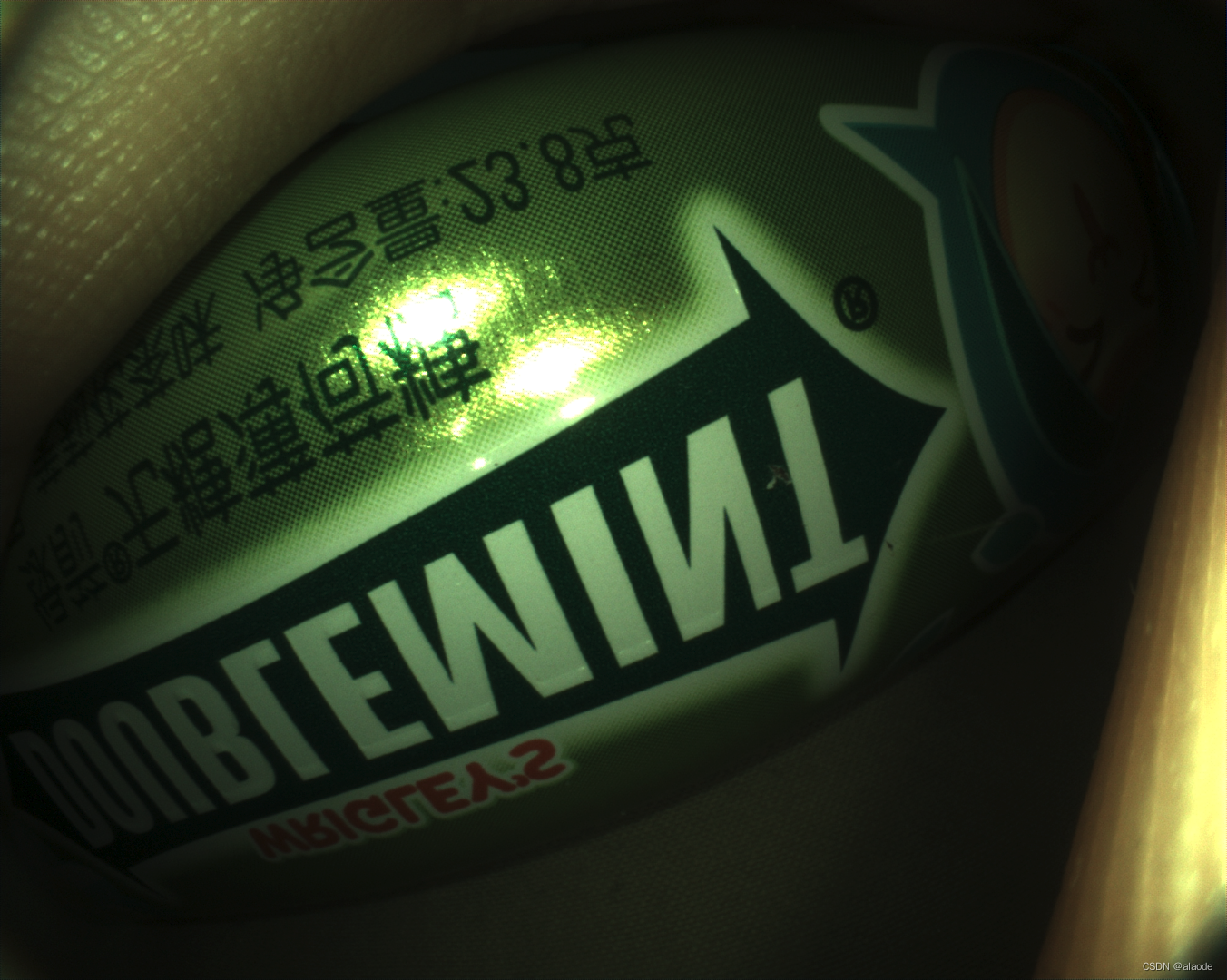

效果

![]() 编辑

编辑

支持

支持xilinx 所有系列fpga

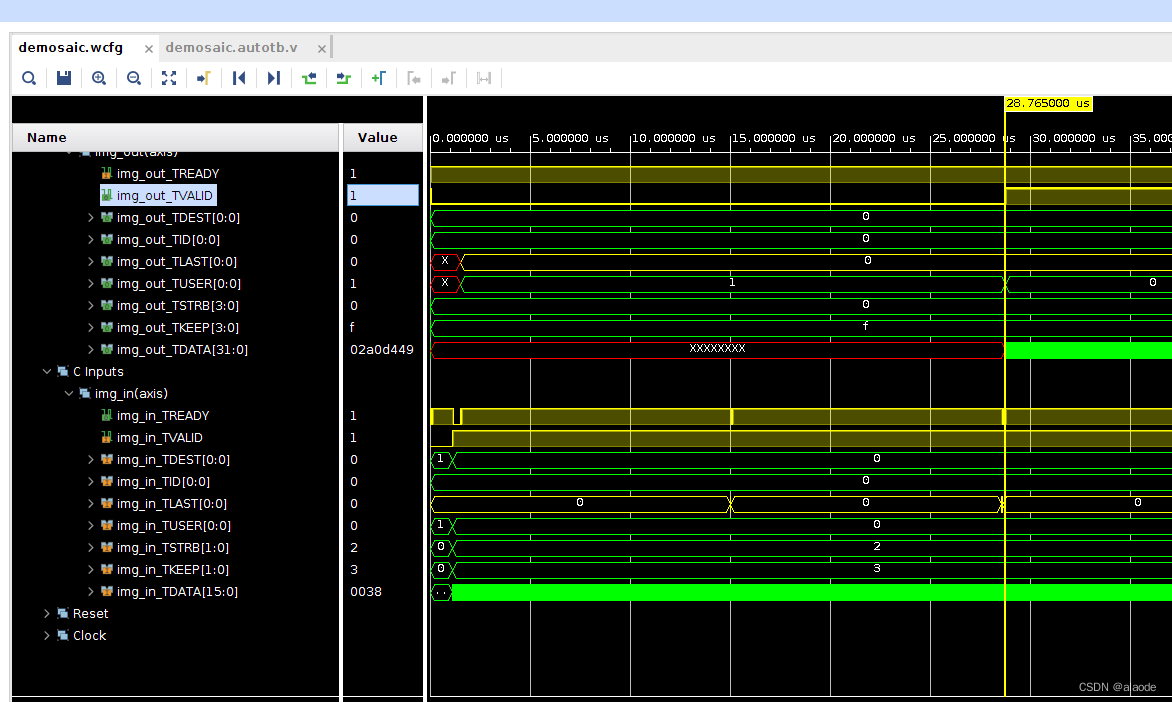

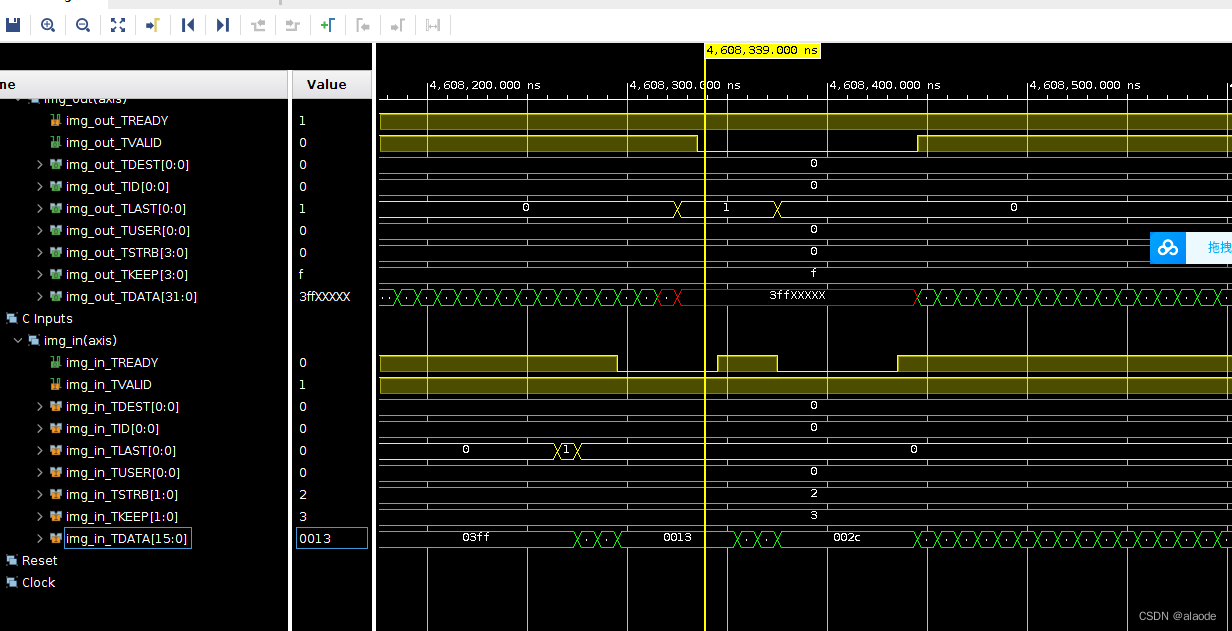

仿真c/rtl

对ip 进行仿真。是否能满足时序要求。

图像开始传输

![]() 编辑

编辑

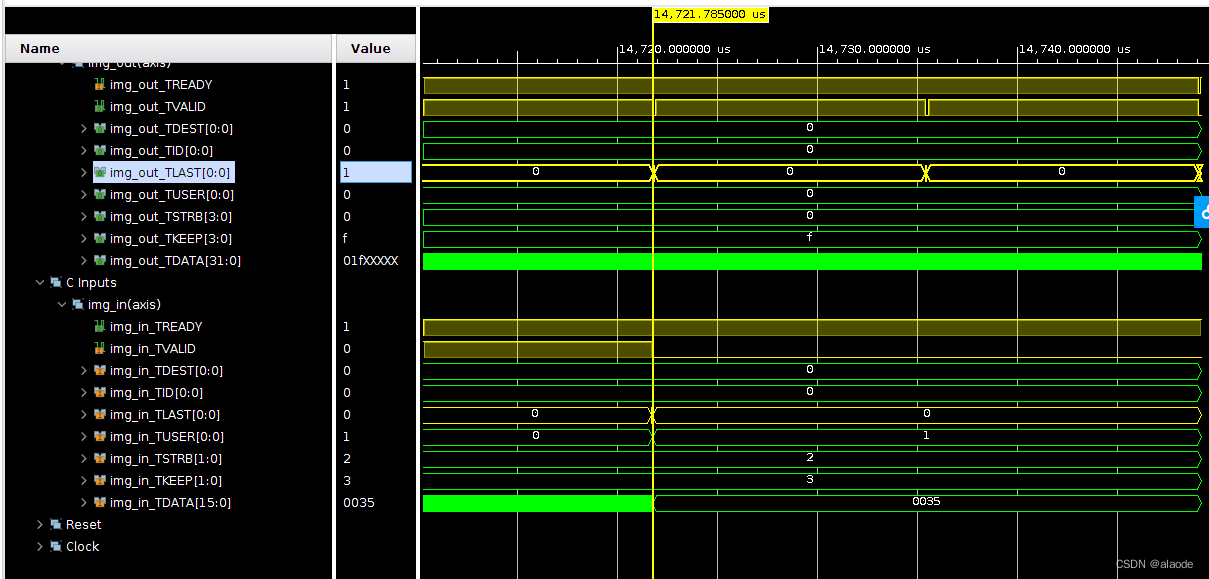

图像结束传输

![]() 编辑

编辑

行尾

![]() 编辑

编辑

ip 接口

![]() 编辑

编辑

// control

// 0x00 : Control signals

// bit 0 - ap_start (Read/Write/COH)

// bit 1 - ap_done (Read/COR)

// bit 2 - ap_idle (Read)

// bit 3 - ap_ready (Read)

// bit 7 - auto_restart (Read/Write)

// others - reserved

// 0x04 : Global Interrupt Enable Register

// bit 0 - Global Interrupt Enable (Read/Write)

// others - reserved

// 0x08 : IP Interrupt Enable Register (Read/Write)

// bit 0 - enable ap_done interrupt (Read/Write)

// bit 1 - enable ap_ready interrupt (Read/Write)

// others - reserved

// 0x0c : IP Interrupt Status Register (Read/TOW)

// bit 0 - ap_done (COR/TOW)

// bit 1 - ap_ready (COR/TOW)

// others - reserved

// 0x10 : Data signal of width

// bit 31~0 - width[31:0] (Read/Write)

// 0x14 : reserved

// 0x18 : Data signal of height

// bit 31~0 - height[31:0] (Read/Write)

// 0x1c : reserved

// 0x20 : Data signal of cfa

// bit 31~0 - cfa[31:0] (Read/Write)

// 0x24 : reserved

// (SC = Self Clear, COR = Clear on Read, TOW = Toggle on Write, COH = Clear on Handshake)

#define XDEMOSAIC_CONTROL_ADDR_AP_CTRL 0x00

#define XDEMOSAIC_CONTROL_ADDR_GIE 0x04

#define XDEMOSAIC_CONTROL_ADDR_IER 0x08

#define XDEMOSAIC_CONTROL_ADDR_ISR 0x0c

#define XDEMOSAIC_CONTROL_ADDR_WIDTH_DATA 0x10

#define XDEMOSAIC_CONTROL_BITS_WIDTH_DATA 32

#define XDEMOSAIC_CONTROL_ADDR_HEIGHT_DATA 0x18

#define XDEMOSAIC_CONTROL_BITS_HEIGHT_DATA 32

#define XDEMOSAIC_CONTROL_ADDR_CFA_DATA 0x20

#define XDEMOSAIC_CONTROL_BITS_CFA_DATA 32