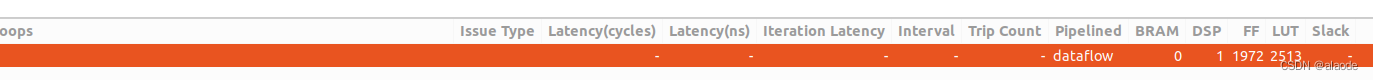

功能

1. 单axi-stream 接口输入,axis输出。(10bit rbg输入,10bit rbg输出。输入为大分辨率,输出为小分辨率)

![]() 编辑

编辑

2. 使用xilinx hls 编写。

![]() 编辑

编辑

20221027 优化

![]() 编辑

编辑

3. 配置寄存器有

#pragma HLS INTERFACE s_axilite port=startx //crop起始点

#pragma HLS INTERFACE s_axilite port=starty //crop起始点

#pragma HLS INTERFACE s_axilite port=width //输入图像的宽度

#pragma HLS INTERFACE s_axilite port=height //输入图像的高度

#pragma HLS INTERFACE s_axilite port=width_crop //输出图像的宽度

#pragma HLS INTERFACE s_axilite port=height_crop //输出图像的高度效果

![]() 编辑

编辑

输入图像 大分辨率

![]() 编辑

编辑

输出图像 小分辨率

支持

支持xilinx 所有系列fpga

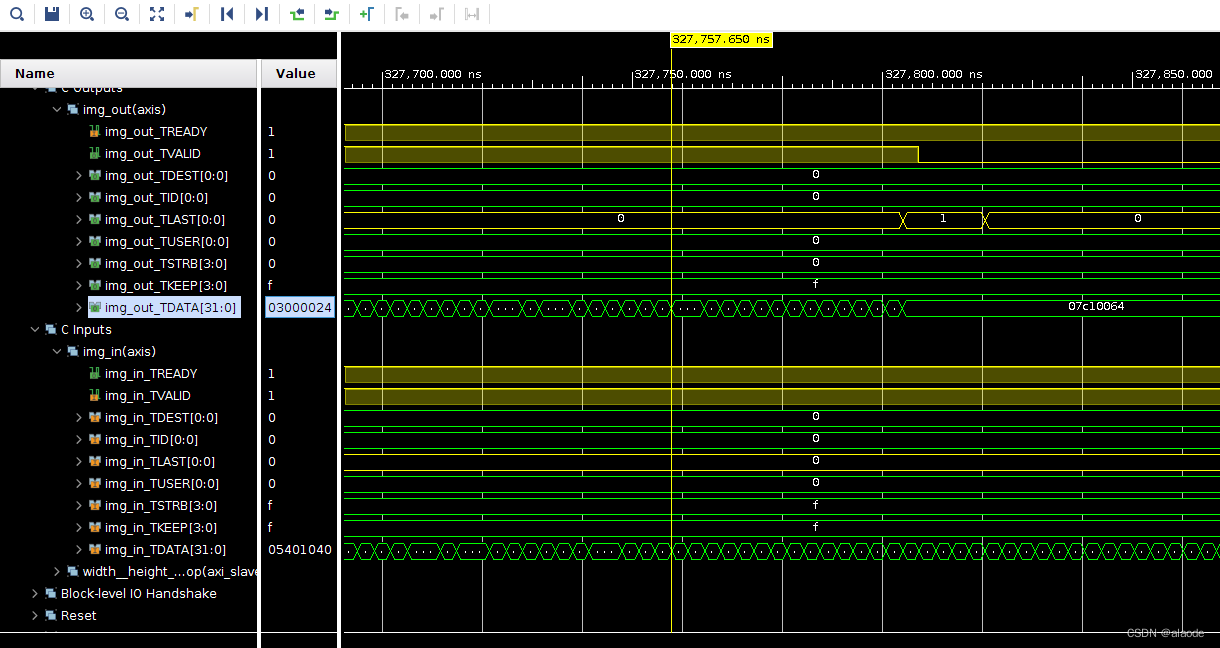

仿真

图像开始输出位置

![]() 编辑

编辑

图像输出行结束

![]() 编辑

编辑

ip 接口

![]() 编辑

编辑