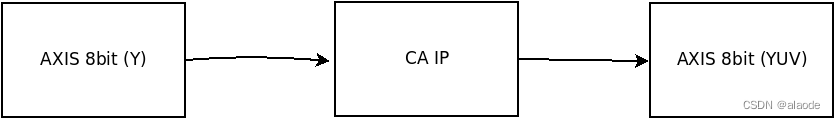

功能

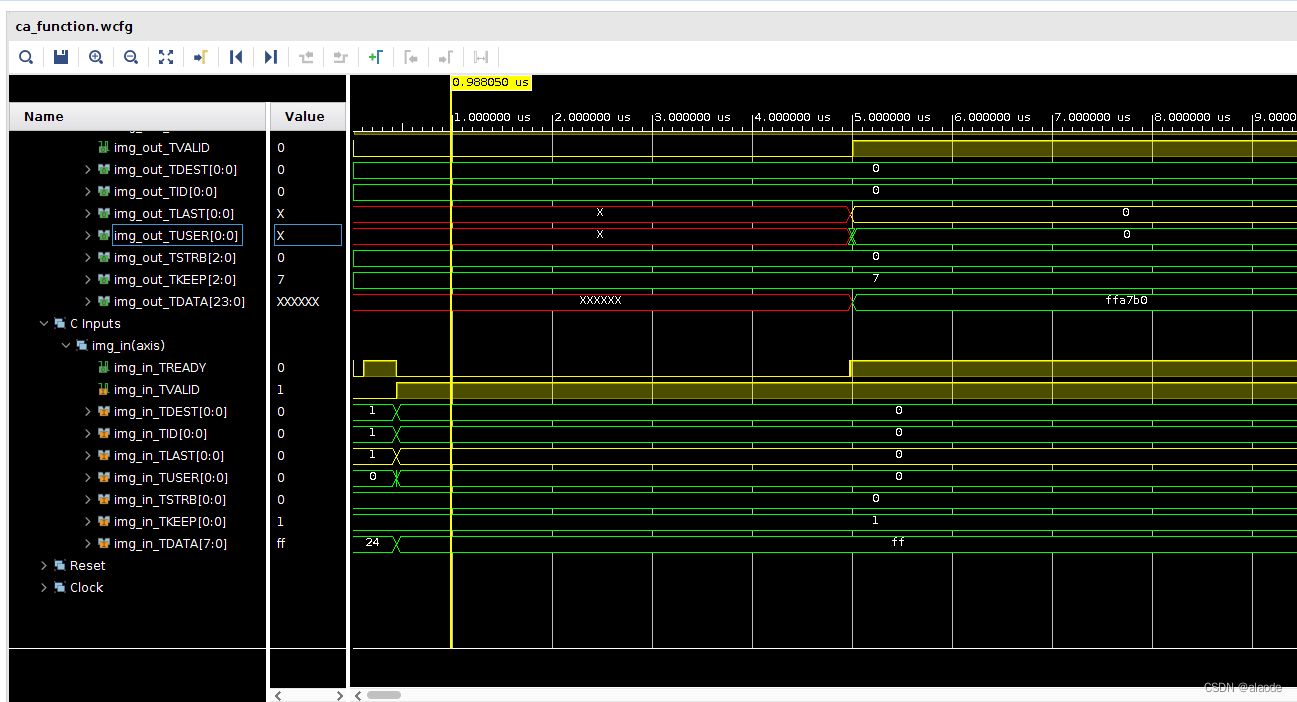

1. 单axi-stream 接口输入,axis输出。( y8bit输入,8bit yuv输出)

![]() 编辑

编辑

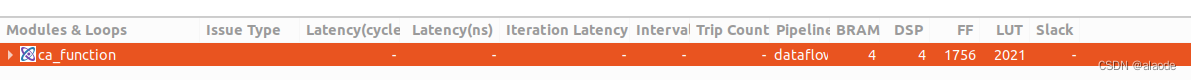

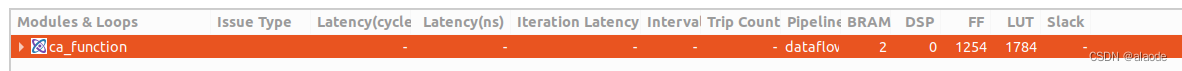

2. 使用xilinx hls 编写。

![]() 编辑

编辑

20221027 优化

![]() 编辑

编辑

3. 配置寄存器有

#pragma HLS INTERFACE s_axilite port=height //宽

#pragma HLS INTERFACE s_axilite port=width //高

#pragma HLS INTERFACE s_axilite port=lutu //u查找表

#pragma HLS INTERFACE s_axilite port=lutv //查找表

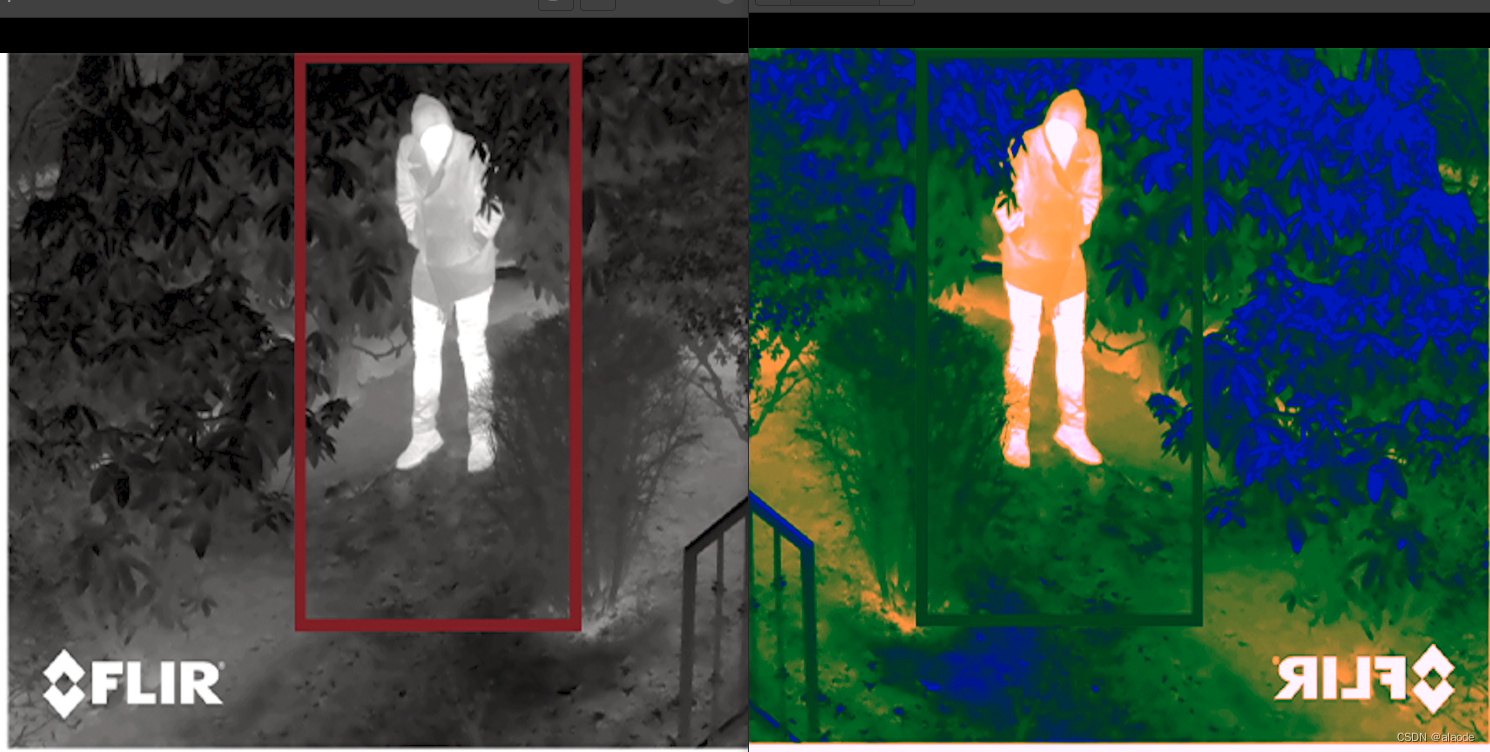

效果

![]() 编辑

编辑

支持

支持xilinx 所有系列fpga

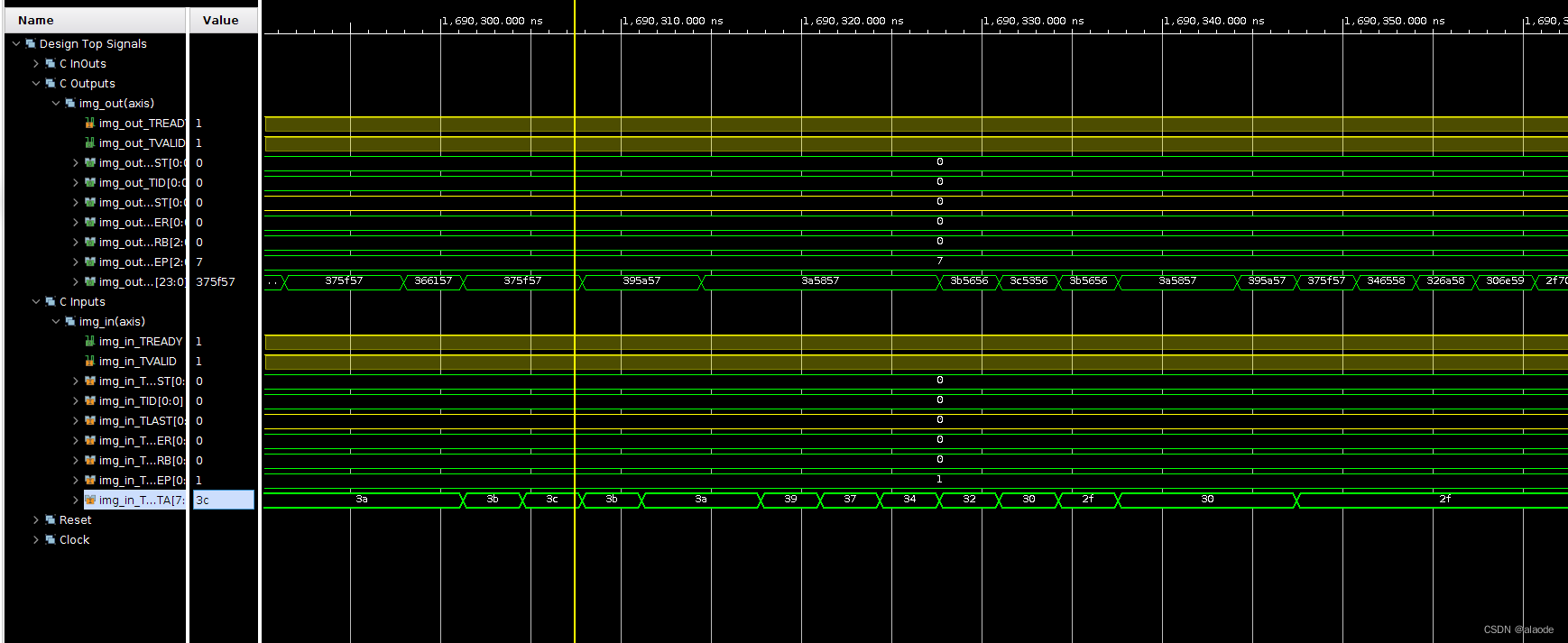

仿真

图像输入

![]() 编辑

编辑

编辑

编辑

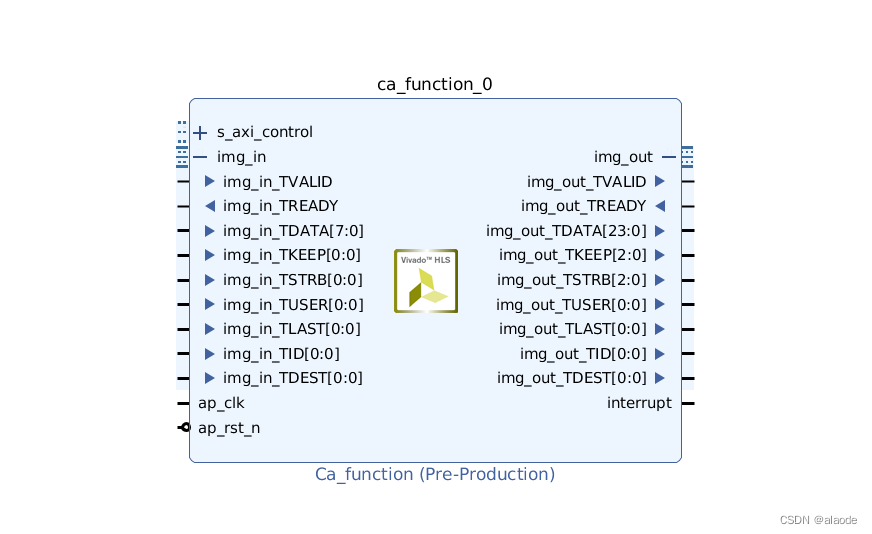

中间数据

![]() 编辑

编辑

![]() 编辑

编辑

#define XCA_FUNCTION_CONTROL_ADDR_AP_CTRL 0x000

#define XCA_FUNCTION_CONTROL_ADDR_GIE 0x004

#define XCA_FUNCTION_CONTROL_ADDR_IER 0x008

#define XCA_FUNCTION_CONTROL_ADDR_ISR 0x00c

#define XCA_FUNCTION_CONTROL_ADDR_WIDTH_DATA 0x010

#define XCA_FUNCTION_CONTROL_BITS_WIDTH_DATA 32

#define XCA_FUNCTION_CONTROL_ADDR_HEIGHT_DATA 0x018

#define XCA_FUNCTION_CONTROL_BITS_HEIGHT_DATA 32

#define XCA_FUNCTION_CONTROL_ADDR_ALL_PIXEL_DATA 0x020

#define XCA_FUNCTION_CONTROL_BITS_ALL_PIXEL_DATA 32

#define XCA_FUNCTION_CONTROL_ADDR_LUTU_BASE 0x100

#define XCA_FUNCTION_CONTROL_ADDR_LUTU_HIGH 0x1ff

#define XCA_FUNCTION_CONTROL_WIDTH_LUTU 8

#define XCA_FUNCTION_CONTROL_DEPTH_LUTU 256

#define XCA_FUNCTION_CONTROL_ADDR_LUTV_BASE 0x200

#define XCA_FUNCTION_CONTROL_ADDR_LUTV_HIGH 0x2ff

#define XCA_FUNCTION_CONTROL_WIDTH_LUTV 8

#define XCA_FUNCTION_CONTROL_DEPTH_LUTV 256