0 前言

这段时间涉及到了IO-PAD,在IO-PAD的RTL的时候注意到了pullup和pulldown,对这个知识比较好奇,就研究了一下,顺便记录下来,IO-PAD的内容等我再研究研究再考虑记录吧 >_<

1 pullup和pulldown的介绍

pullup和pulldown并非是verilog的内置原语,仅在仿真或综合过程中起作用,用来设置信号的默认状态

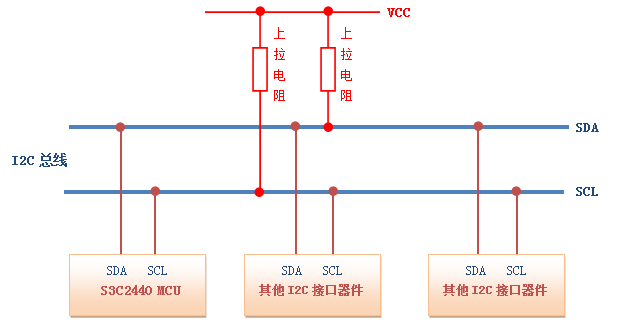

在实际的硬件电路中,用来代表上拉和下拉,就比如在I2C中,SCL和SDA两个信号是open-drain的,在实际使用过程中往往需要接上拉电阻,如下图

接在VCC的两个电阻就是上拉电阻,这个上拉电阻在verilog中就可以用pullup表示

下面结合实例来看看怎么使用

2 不使用pullup和pulldown的情况

`timescale 1ns/10ps

module tb;

logic dout;

logic sel;

assign dout = sel ? 1'bz : 1'b0;

initial begin

sel = 1'b0;

#10;

sel = 1'b1;

#10;

sel = 1'b0;

#10;

$finish;

end // initial begin

initial begin

$monitor("\t", $time, ,"sel = %0b, dout = %0b", sel, dout);

end

endmodule

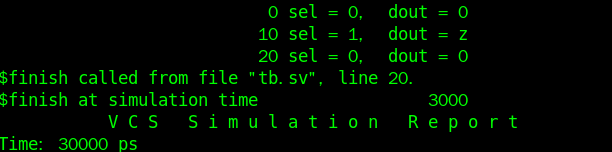

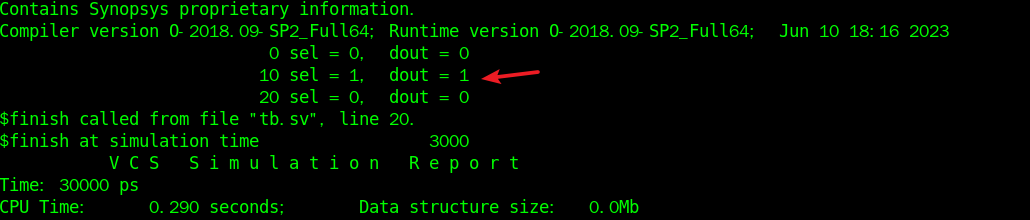

在这个例子中,当sel = 1'b1时输出highz,sel = 0时输出0,在initial·中对sel先后赋值0和1,来看看运行结果

可以看到当sel = 0时,dout = 0,当sel = 1时,dout = z,这个结果符合预期

注意,在这个例子中,并没有使用到pullup,下面给出使用pullup的例子

2 使用pullup和pulldown的情况

`timescale 1ns/10ps

module tb;

logic dout;

logic sel;

assign dout = sel ? 1'bz : 1'b0;

pullup(dout);

initial begin

sel = 1'b0;

#10;

sel = 1'b1;

#10;

sel = 1'b0;

#10;

$finish;

end // initial begin

initial begin

$monitor("\t", $time, ,"sel = %0b, dout = %0b", sel, dout);

end

endmodule

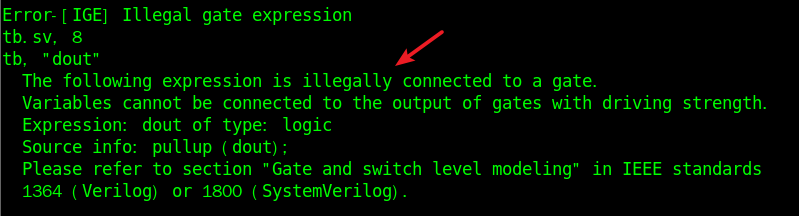

同样的例子,加上了pullup(dout)语句(第7行),其他的均为改变,首先可以看到pullup有被highlight,说明这是一个关键词

下面开始编译

报错了,给的原因是logic声明的变量不能连接到带有驱动强度的gate输出端,那把logic声明改成wire,修改后的代码如下

`timescale 1ns/10ps

module tb;

wire dout;

logic sel;

assign dout = sel ? 1'bz : 1'b0;

pullup(dout);

initial begin

sel = 1'b0;

#10;

sel = 1'b1;

#10;

sel = 1'b0;

#10;

$finish;

end // initial begin

initial begin

$monitor("\t", $time, ,"sel = %0b, dout = %0b", sel, dout);

end

endmodule

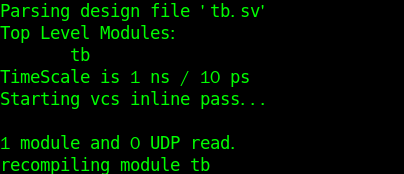

再次编译

编译通过,下面执行仿真,来看看仿真结果

可以看到在这个例子中,当sel = 1时,dout = 1,不再是highz

3 push-pull和open-drain的介绍

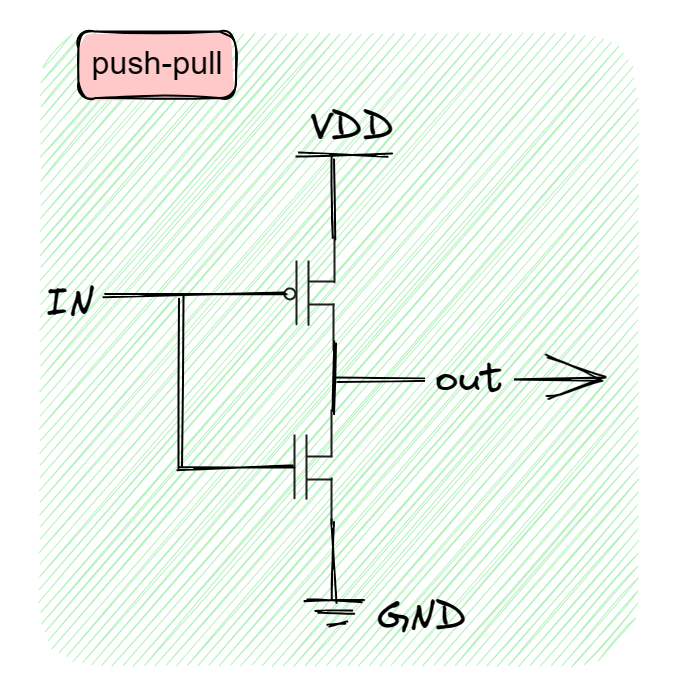

就拿mos管来简单介绍一下吧

这是一个push-pull的电路,由两个mos管组成,上面的是PMOS,下面的是NMOS

当IN = 1时,NMOS导通,PMOS截止,最终OUT = 0,电流方向为OUT -> NMOS,这个过程叫挽

当IN = 0时,NMOS截止,PMOS导通,最终OUT = 1,电路方向为PMOS -> OUT,这个过程叫推

这就是push-pull(推挽)

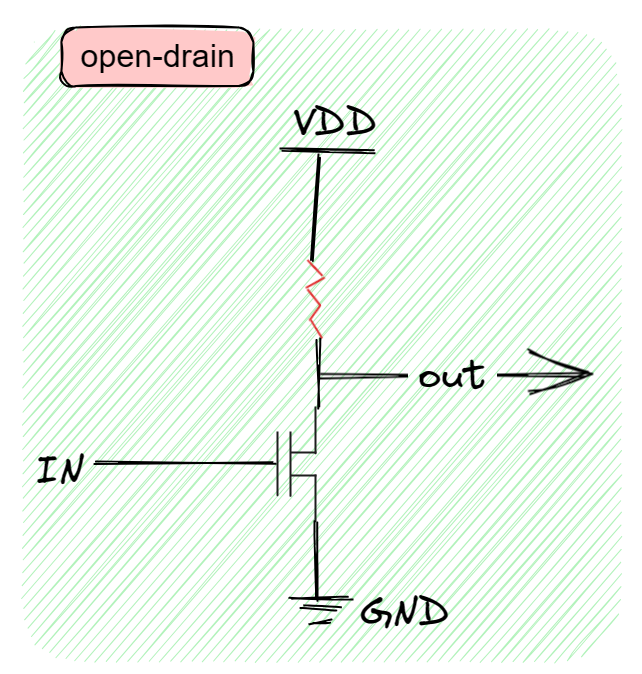

这是open-drain,与push-pull不同的是上面的PMOS换成了电阻,这个电阻就是上拉电阻

同样的,当IN = 1时,NMOS导通,OUT = 0

那当 IN = 0时呢?NMOS截止,如果此时不接上拉电阻,那么OUT端此时的状态是不确定的(单看这个电路的情况下)

当接入一个上拉电阻后,由于MOS管截止后,电阻可以看做是无穷大,此时从VDD -> GND就可以看做是一个电阻R和一个电阻无穷大的NMOS串联,那么在OUT点的电压自然约等于VDD

OK,先这样,至于在用pullup的时候为什么不能用logic声明,下次介绍吧

标签:10,dout,initial,pulldown,b0,verilog,pullup,sel From: https://www.cnblogs.com/ICcode/p/17472109.html