目 录

1 硬件资源

2 引脚说明(篇幅问题,暂不提供详细内容)

3 电气特性

4 机械尺寸

5 底板设计注意事项

硬件资源

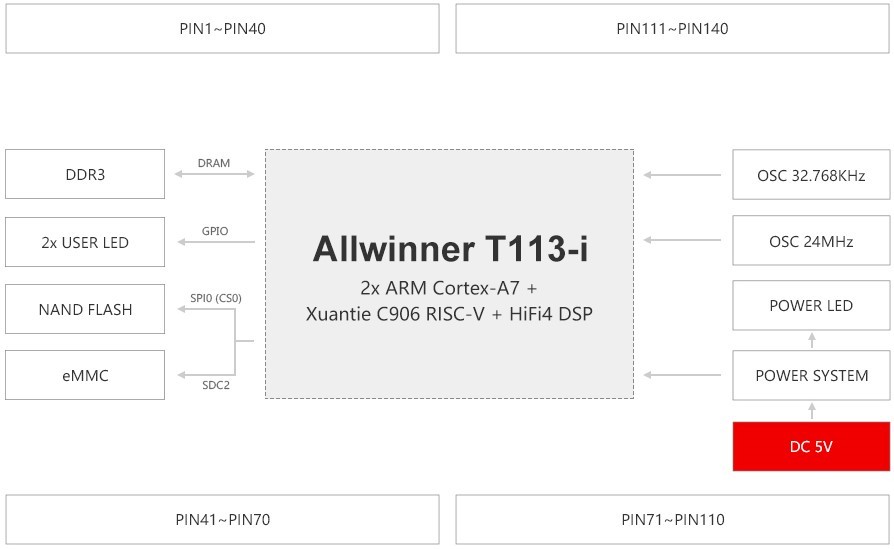

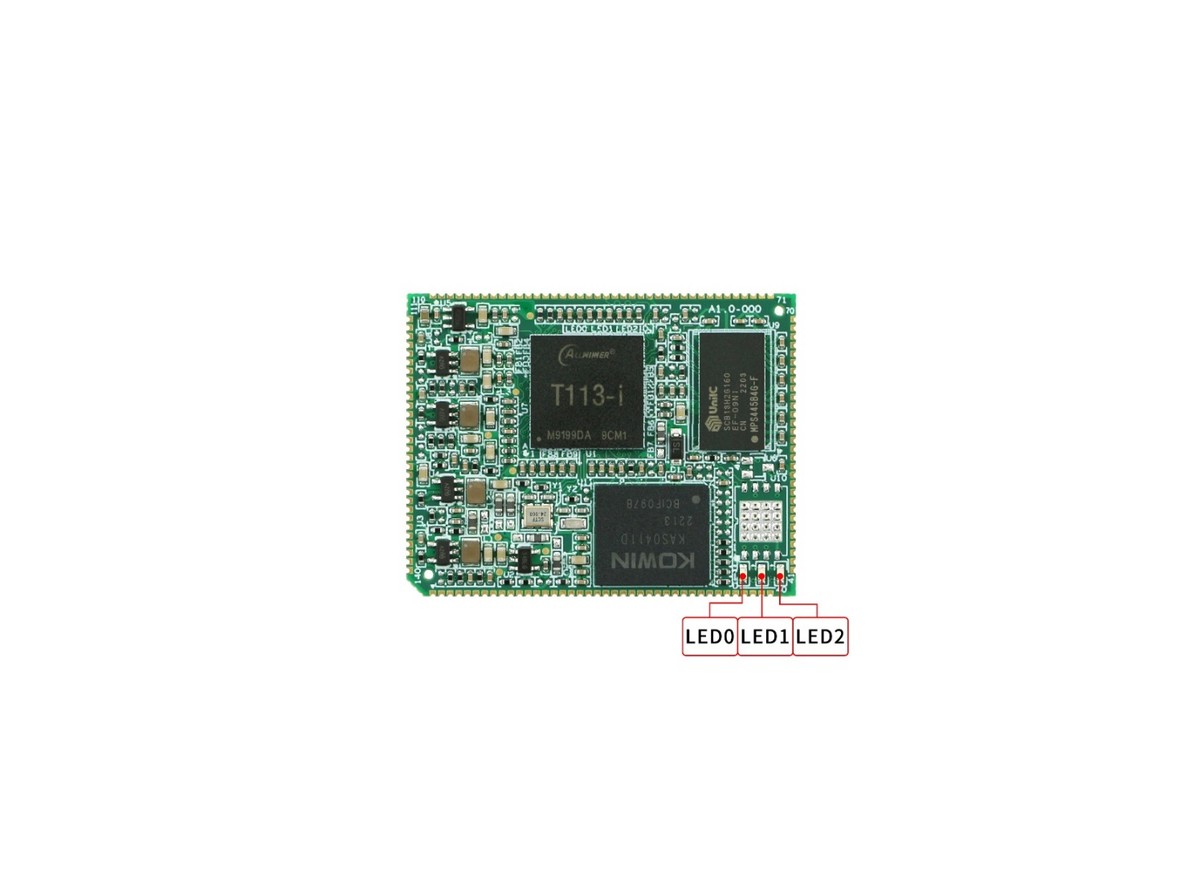

SOM-TLT113核心板板载CPU、ROM、RAM、晶振、电源、LED等硬件资源,并通过邮票孔连接方式引出IO。

图 1 核心板硬件框图

图 1 核心板硬件框图

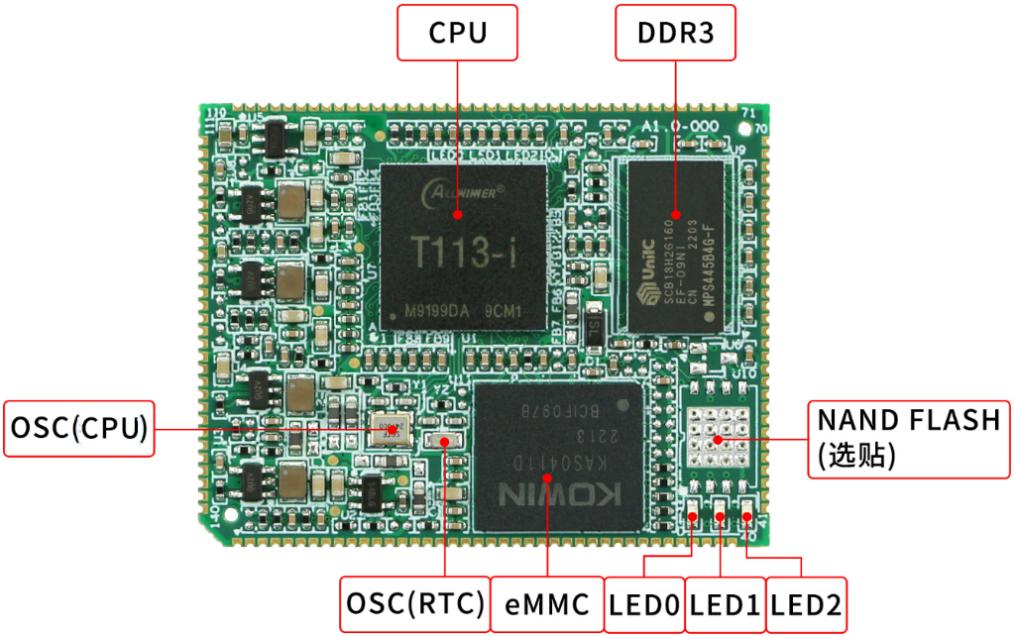

图 2

图 2

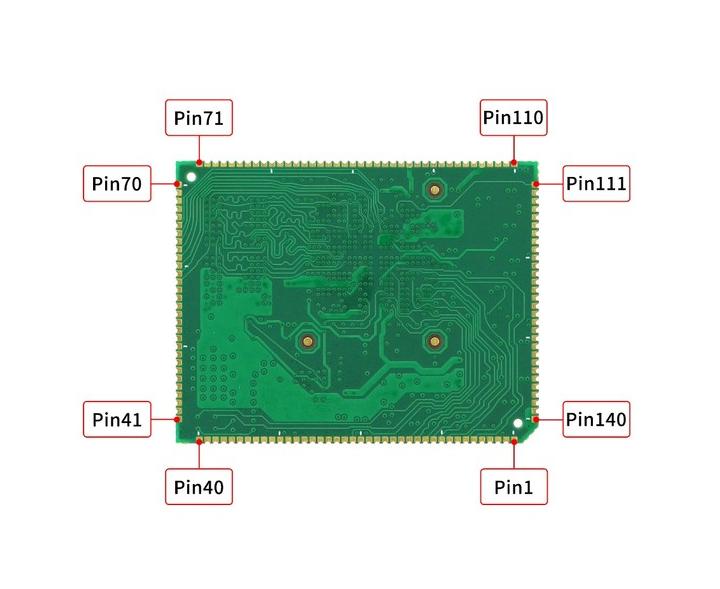

图 3

图 3

CPU

核心板CPU型号为全志科技T113-i,LFBGA封装,工作温度为-40°C~85°C,引脚数量为337个,尺寸为13mm*13mm。

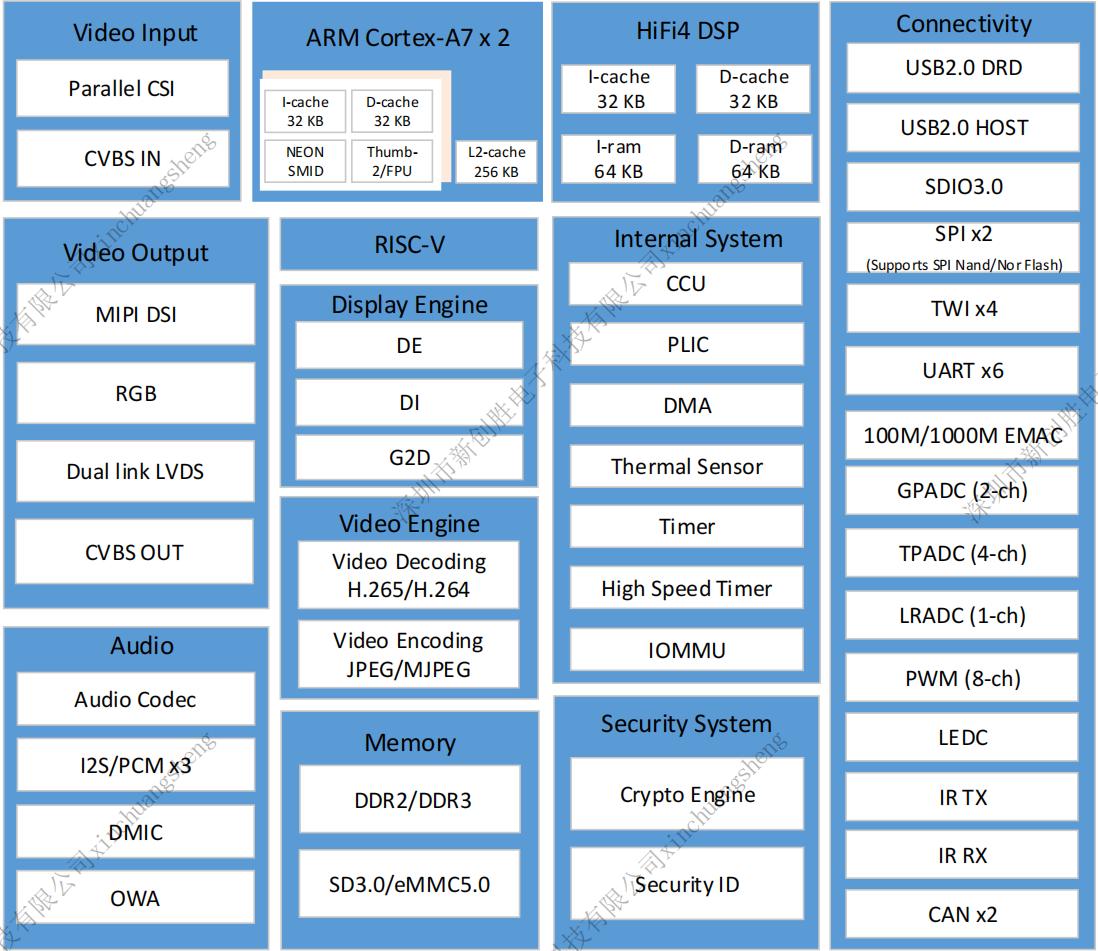

T113-i处理器架构如下:

表 1

|

T113-i |

全志科技T113-i,22nm |

|

|

2x ARM Cortex-A7,主频高达1.2GHz |

||

|

1x HiFi4 DSP,主频高达600MHz |

||

|

1x 玄铁C906 RISC-V(64bit),主频高达600MHz |

||

|

Decoder |

H.265 [email protected] up to 4K@30fps H.264 BP/MP/[email protected] up to 4K@24fps MPEG-4 SP/ASP L5.0 up to 1080p@60fps MPEG-2/MPEG-1 MP/HL up to 1080p@60fps JPEG/Xvid/Sorenson Spark up to 1080p@60fps MJPEG up to 1080p@30fps |

|

|

Encoder |

JPEG/MJPEG up to 1080p@60fps |

|

图 4 T113-i处理器功能框图

图 4 T113-i处理器功能框图

ROM

NAND FLASH

核心板通过SPI0(CS0)总线连接工业级NAND FLASH,型号兼容兆易创新(GigaDevice)公司的GD5F2GQ5UEYIG(256MByte),江波龙(Longsys)公司的F35SQA002G(256MByte)。

eMMC

核心板通过SMHC(主机控制器)连接至eMMC,使用SDC2总线,采用4bit数据线。eMMC型号为康盈(KOWIN)公司的KAS0411D(4GByte)。

备注:由于SDC2与SPI0总线存在引脚复用关系,因此核心板可选贴eMMC或NAND FLASH。

RAM

核心板通过专用SDRAM总线连接1片DDR3,采用16bit数据线。DDR3型号兼容紫光国芯(UniIC)公司的SCB15H1G160AF-13KI(128MByte)、SCB13H2G160EF-09NI(256MByte)和SCB13H4G160AF-11MI(512MByte),力积存储(ZENTEL)公司的A3T1GF40CBF-GMLI(128MByte),以及江波龙(Longsys)公司的F60C1A0002-M69W(256MByte)和F60C1A0004-M79W(512MByte),支持DDR3-1600工作模式(800MHz)。

晶振

核心板采用两个工业级晶振Y1和Y2。Y1晶振时钟频率为24MHz,为CPU提供系统时钟源。Y2晶振时钟频率为32.768KHz,用作CPU内部RTC使用。

电源

核心板采用分立电源供电设计,所选电源方案均满足工业级环境使用要求。电源系统设计满足系统的供电和CPU上电、掉电时序要求,采用5V直流电源供电。

LED

核心板板载3个LED。其中LED0为电源指示灯,系统上电后默认会点亮。LED1和LED2为用户可编程指示灯,分别对应F2/PC0和F1/PC1两个引脚,高电平点亮。

图 5

图 6

外设资源

核心板通过邮票孔引出的主要外设资源及性能参数,如下表所示。

表 2

|

外设资源 |

数量 |

性能参数 |

|

CSI |

1 |

支持8位DVP并行接口传输,支持1080P@30fps; |

|

CVBS IN |

2 |

CVBS输入,支持NTSC和PAL制式; |

|

CVBS OUT |

1 |

CVBS输出,支持NTSC和PAL制式; |

|

LVDS DISPALY |

2 |

包含LVDS0、LVDS1输出,最高支持1080p@60fps; 备注:LVDS0、LVDS1与LCD0(RGB DISPLAY)引脚复用,同时LVDS0与MIPI DSI引脚复用; |

|

RGB DISPALY |

1 |

LCD0输出,最高支持1080P@60fps; |

|

MIPI DSI |

1 |

包含4个数据通道,最高支持1200P@60fps; 符合MIPI DSI V1.01和MIPI D-PHY V1.00; |

|

Audio Codec |

1 |

包含2通道DAC,采样率8KHz~192KHz; 包含3通道ADC,采样率8KHz~48KHz; 包含3路单声道MIC IN、1路立体声LINE IN、1路立体声FM IN;包含1路立体声差分LINE OUT、1路立体声H/P(Headphone) OUT; |

|

USB DRD |

1 |

USB2.0(USB0),支持DRD模式; 支持高速模式(480Mbps)、全速模式(12Mbps)、低速模式(1.5Mbps); |

|

USB HOST |

1 |

USB2.0(USB1); 支持高速模式(480Mbps)、全速模式(12Mbps)、低速模式(1.5Mbps); |

|

SMHC |

2 |

支持SD3.0,SDIO3.0,MMC5.0协议; SDC0:4位数据总线(推荐作为底板Micro SD功能); SDC1:4位数据总线; SDC2:4位数据总线; 备注:核心板板载eMMC已使用SDC2,未引出至邮票孔引脚; |

|

TWI(I2C) |

4 |

支持标准模式(100Kbps)和高速模式(400Kbps); |

|

SPI |

1 |

支持SPI模式和DBI(Display Bus Interface)模式; 支持Master Mode、Slave Mode; 每路SPI支持1个片选信号; 最高支持100MHz工作频率; 备注:核心板板载NAND FLASH已使用SPI0,未引出至邮票孔引脚;并且SPI0与SDC2存在引脚复用关系; |

|

UART |

6 |

支持4Mbps波特率(64MHz APB时钟); 支持硬件或软件流控; |

|

PWM |

8 |

支持0~100%可调占空比,支持PWM输出、输入捕获,输出频率为0~24MHz或100MHz; |

|

Ethernet |

1 |

1路EMAC,支持RMII/RGMII PHY接口(10/100/1000Mbps); |

|

GPADC |

2 |

12位SAR型A/D转换器,采样频率高达1MHz; |

|

TPADC |

4 |

12位SAR型A/D转换器,采样频率高达1MHz,支持4线电阻式触摸屏检测输入; |

|

LRADC |

1 |

6位A/D转换器,采样频率高达2KHz,支持保持键和通用键; |

|

LEDC |

1 |

支持1024个LED串行连接,LED数据传输速率高达800Kbps; |

|

I2S/PCM |

3 |

全双工,采样率8KHz~384KHz; |

|

DMIC |

1 |

最高支持8通道,采样率8KHz~48KHz; |

|

OWA |

1 |

One Wire Audio,兼容S/PDIF协议; |

|

CIR |

2 |

包含CIR TX、CIR RX,可通过红外线进行远程控制; |

|

CAN |

2 |

支持CAN 2.0A和CAN 2.0B协议; |

|

JTAG |

3 |

包含ARM、RISC-V和HiFi4 DSP JTAG; |

引脚说明

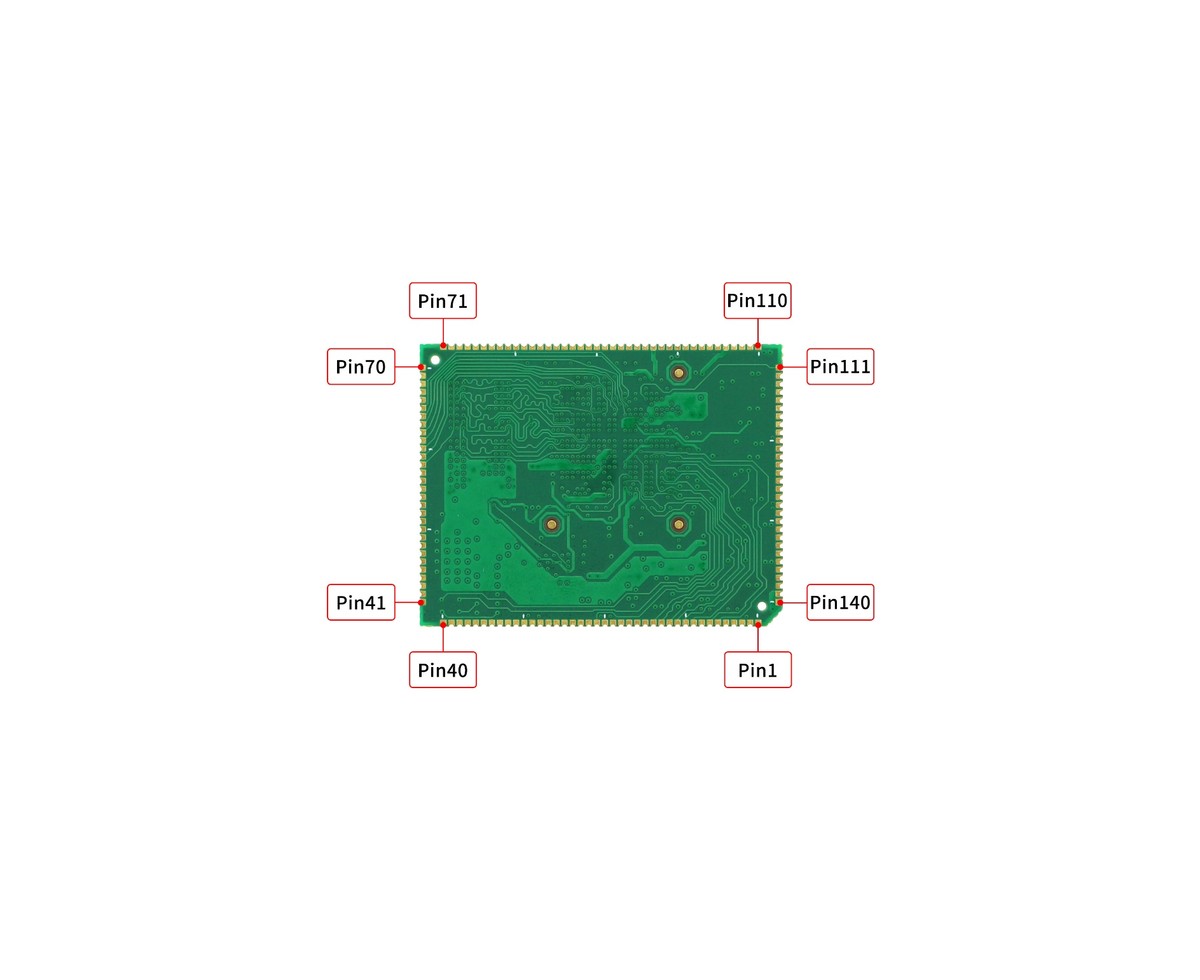

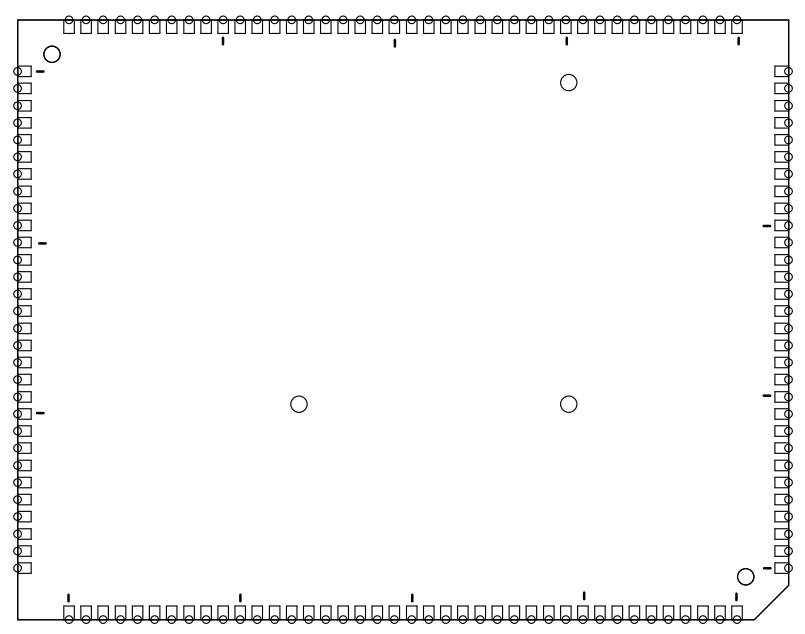

引脚排列

核心板邮票孔引脚采用2x 30pin + 2x 40pin,共140pin规格,引脚排列如下图所示。

图 7 核心板引脚排列示意图

图 7 核心板引脚排列示意图

电气特性

工作环境

表 10

|

环境参数 |

最小值 |

典型值 |

最大值 |

|

工作温度 |

-40°C |

/ |

85°C |

|

存储温度 |

-50°C |

/ |

90°C |

|

工作湿度 |

35%(无凝露) |

/ |

75%(无凝露) |

|

存储湿度 |

35%(无凝露) |

/ |

75%(无凝露) |

|

工作电压 |

/ |

5.0V |

/ |

功耗测试

表 11

|

工作状态 |

电压典型值 |

电流典型值 |

功耗典型值 |

|

空闲状态 |

5.0V |

0.12A |

0.60W |

|

满负荷状态 |

5.0V |

0.22A |

1.10W |

备注:功耗基于TLT113-EVM评估板测得。测试数据与具体应用场景有关,仅供参考。

空闲状态:系统启动,评估板不接入其他外接模块,不执行程序。

满负荷状态:系统启动,评估板不接入其他外接模块,运行DDR压力读写测试程序,2个ARM Cortex-A7核心使用率约为100%。

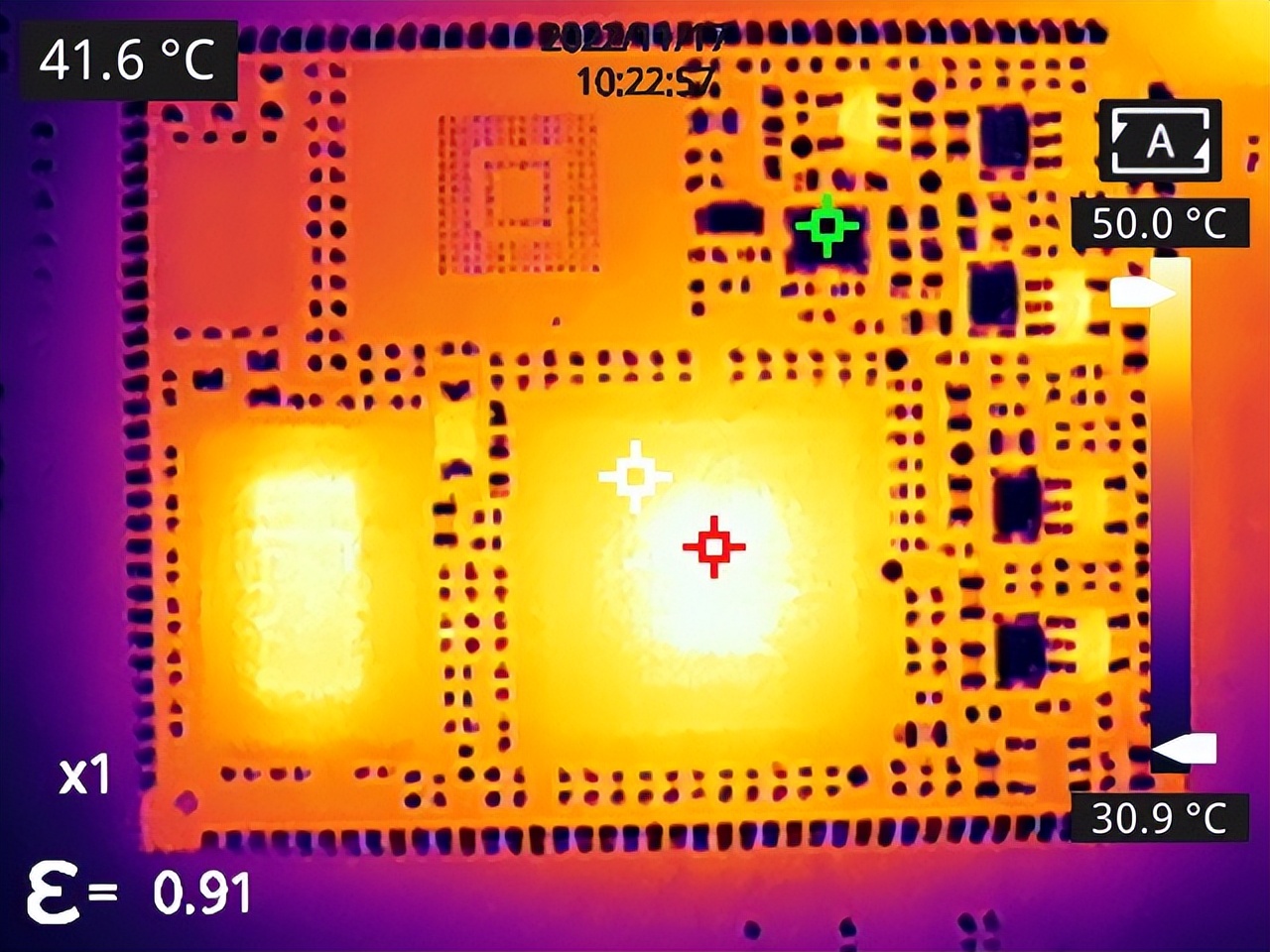

热成像图

核心板在常温环境、自然散热(不安装散热片与风扇)、满负荷状态下,稳定工作10min后,测得热成像图如下所示。

备注:不同测试条件下结果会有所差异,请参考测试结果,并根据实际情况合理选择散热方式。

图 8

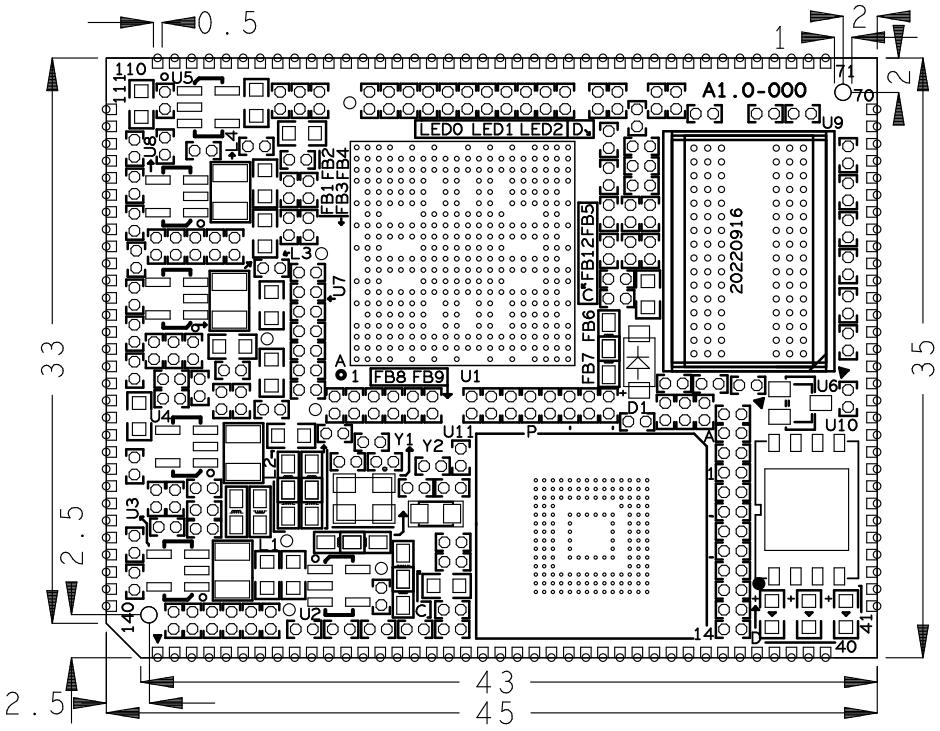

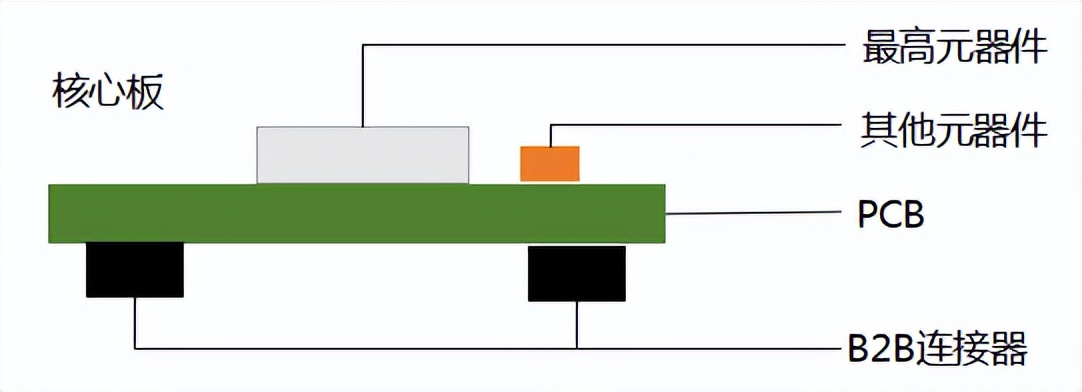

机械尺寸

核心板主要硬件相关参数如下所示,仅供参考。

表 12

|

PCB尺寸 |

35mm*45mm |

|

PCB层数 |

8层 |

|

元器件最高高度 |

1.33mm |

|

PCB板厚 |

1.6mm |

|

重量 |

NAND FLASH配置:7.1g |

|

eMMC配置:7.3g |

图 9

图 10

元器件最高高度:指核心板最高元器件水平面与PCB正面水平面的高度差。核心板最高元器件为CPU(U1)。

图 11

底板设计注意事项

最小系统设计

基于SOM-TLT113核心板进行底板设计时,请务必满足最小系统设计要求,具体如下。

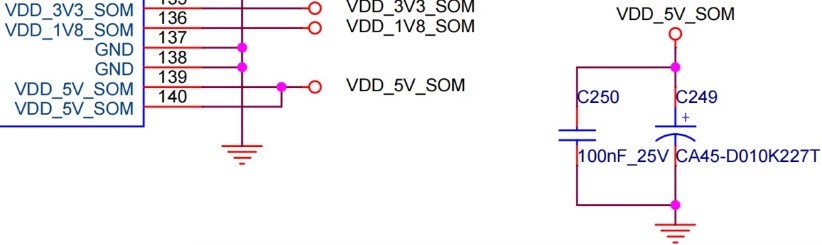

电源设计说明

- VDD_5V_SOM

VDD_5V_SOM为核心板的主供电输入,电源功率建议参考评估板按最大10W进行设计。

图 12

VDD_5V_SOM在核心板内部未预留总电源输入的储能大电容,底板设计时请参照评估底板原理图,在靠近邮票孔焊盘位置放置100~220uF储能大电容。

图 13

- VDD_5V_MAIN & VDD_3V3_MAIN & VDD_1V8_MAIN

VDD_5V_MAIN、VDD_3V3_MAIN、VDD_1V8_MAIN为底板提供的外设电源。为了使VDD_5V_MAIN、VDD_3V3_MAIN、VDD_1V8_MAIN满足处理器的上电、掉电时序要求,推荐使用VDD_3V3_SOM来控制DCDC电源使能。

图 14

图 15

图 16

- 系统启动配置

F5/PC5/BOOT_SEL1、H3/PC4/BOOT_SEL0引脚在CPU内部已默认上拉处理,并且核心板内部系统启动配置电路同时对F5/PC5/BOOT_SEL1、H3/PC4/BOOT_SEL0引脚进行设计(详情请查看引脚说明)。核心板已分别支持Micro SD、NAND FLASH和eMMC启动,评估底板无需再次设计系统启动配置电路。

图 17

系统复位信号

- M2/RESETn

M2/RESETn为CPU的复位输入、输出引脚,可通过按键复位CPU,或CPU输出控制外设接口的复位。

备注:M2/RESETn复位输出信号在VDD_5V_SOM电源输入92.5ms后将拉高至高电平,若底板外设使用M2/RESETn作为系统复位信号,请注意电源上电时序设计。

- A18/FEL

A18/FEL为CPU固件强制烧录引脚,硬件系统未上电时将A18/FEL接地,上电后再将A18/FEL释放,则系统进入固件升级模式(通过USB0)。

其他设计注意事项

保留Micro SD卡接口

评估底板通过SDC0总线引出Micro SD接口,主要用于调试过程中使用Linux系统启动卡来启动系统,或批量生产时可基于Micro SD卡快速固化系统至NAND FLASH或eMMC,底板设计时建议保留此外设接口。

保留UART0接口

评估底板将UART0通过CH340T芯片引至Type-C接口,作为系统调试串口使用,底板设计时建议保留UART0作为系统调试串口。

标签:底板,必看,引脚,核心,全志,支持,玄铁,VDD,CPU From: https://www.cnblogs.com/Tronlong818/p/17083705.html