文章目录

文章目录

前言

本章关于vivado仿真软件的使用介绍

提示:以下是本篇文章正文内容,下面案例可供参考

一、Vivado Simulato介绍

Vivado Simulato是我们的仿真模拟器,用于硬件调试和判断代码正确性。

Vivado 设计套件内部集成了仿真器Vivado Simulator,能够在设计流程的不同阶段运行设计的功能仿真和时序仿真,结果可以在Vivado IDE 集成的波形查看器中显示。Vivado 还支持与诸如ModelSim、Verilog Compiler Simulator (VCS)、Questa Advanced Simulator 等第三方仿真器的联合仿真。

二、功能仿真需要的文件

1.设计HDL 源代码,也被称为UUT(Unit Under Test):可以是VHDL 语言或Verilog 语言,既可以是设计的顶层模块,也可以是设计的下层子模块。

2.测试激励代码,也被称为TestBench:根据UUT 顶层输入/输出接口的设计要求,来产生顶层输入接口的测试激励并监视顶层输出接口。由于不需要进行综合,书写具有很大的灵活性。

3.仿真模型/库:根据设计内调用的器件供应商提供的模块而定,如:FIFO、ADD_SUB 等。在使用Vivado Simulator 时,仿真器所需的仿真模型/库是预编译好并集成在Vivado 中的,因此不需要进行额外的预编译操作,直接加载HDL 设计和TestBench 即可执行仿真。

三、具体步骤

在Vivado IDE 中进行仿真,首先需要创建一个TestBench。我们点击“Sources”窗口中的“+”号(Add Sources 命令),在弹出的窗口中选择“Add or Create Simulation Sources”,如下图所示:

点击next,在接下来的页面中点击“Create File”,如下图所示:

在弹出的对话框中输入TestBench 的文件名“tb_led_twinkle”,如下图所示:

TestBench 源文件名称的前缀“tb_”可以用来向用户示意:该源文件是一个TestBench 源文件,仅用于

仿真,并不能用于设计的综合和实现。建议大家按照这种规范来创建TestBench,以免设计源文件和仿真源

文件相混淆。

点击OK,然后直接点击“Finish”即可,如下图所示:

在弹出的自动定义模块窗口中我们直接点击OK 即可,结束TestBench 源文件的创建,如下图所示:

此时我们就可以在Source 窗口中看到刚刚创建的TestBench,双击打开它后发现其模块内部什么都没有定义,如下图所示:

然后写入test bench的代码

`timescale 1ns / 1ps //仿真时间单位/仿真时间精度

module tb_led_twinkle();

reg sys_clk;

reg sys_rst_n;

wire [1:0]led;

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

#200

sys_rst_n = 1'b1;

end

always #10 sys_clk = ~sys_clk;//生成时钟

led_twinkle u_led_twinkle(

.sys_clk (sys_clk), //系统时钟

.sys_rst_n (sys_rst_n), //系统复位,低电平有效

.led (led) //LED灯

);

endmodule

保存之后,因为仿真主要看的是逻辑功能,所以有时候为了快一点,可以先在源代码里修改一下。

在“Flow Navigator”窗口中点击“Run Simulation”并选择“Run Behavioral Simulation”,如下图所示:

Run Behavior Simulation 功能仿真

Run Post-Systhesis Functional Simulation 综合后的功能仿真

Run Post-Systhesis Timing Simulation 综合后的时序仿真

Run Post-Implementation Functional Simulation 实现后/布局布线后的功能仿真

Run Post-Implementation Timing Simulation 实现后/布局布线后的时序仿真

之后我们就进入了仿真界面,如下图所示:

(1)Scope 窗口。Scope(范围)是HDL 设计的层次划分。在Scope 窗口中,您可以看到设计层次结构。当您选择了一个Scope 层次结构中的作用域时,该作用域内的所有HDL 对象,包括reg、wire 等都会出现在“Objects”窗口中。您可以在“Objects”窗口中选择HDL 对象,并将它们添加到波形窗口中。

(2)Object 窗口。“Objects”窗口会显示在“Scopes”窗口中选择的范围内的所有HDL 仿真对象。例如,我们在Scope 窗口中选择“u_led_twinkle”,在“Objects”窗口中就会自动显示出led_twinkle 模块中所有的对象。如下图所示:

(3)波形窗口。用于显示所要观察信号的波形。若要向波形窗口添加单个HDL 对象或多个HDL 对象,在“Objects”窗口中,右键单击一个或多个对象,然后从下拉菜单中选择“Add to Wave Window”选项。例如,我们把“u_led_twinkle”模块下的“cnt”计数器添加到波形窗口中,如下图所示:

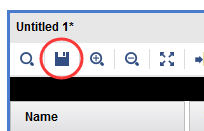

一般地,每当我们进行一次仿真时,都会把当前波形的配置信息保存下来,包括波形窗口中具有哪些信号等等,以便在下一次打开仿真器进行仿真时,继续使用上一次仿真的配置信息。我们点击波形窗口中的保存按钮,如下图所示:

之后会弹出“Save Waveform”对话框,提示用户将当前波形配置信息保存为“.wcfg”后缀的文件,且工具已经自动地输入了文件名“tb_led_twinkle_behav”,文件的保存目录也被工具自动设置为了当前的工程目录,所以我们保持其默认状态即可,直接点击“Save”。如下图所示:

注意,.wcfg 文件只是包含波形窗口的配置信息,并不包含波形的数据文件,波形的数据文件被存储在另外的文件中。

(4)仿真工具栏。仿真工具栏包含运行各个仿真动作的命令按钮,从左至右依次是:

• Restart:将仿真时间重置为零,此时波形窗口中原有的波形都会被清除。下次执行仿真时,会从0时刻重新开始。

• Run all:运行仿真,直到其完成所有事件或遇到HDL 语句中的 s t o p 或 stop 或 stop或finish 命令为止。注意,如果没有在TestBench 语句中加入 s t o p 或 stop 或 stop或finish 命令,当点击Run all 命令时,仿真器会无休止地一直仿真下去,除非用户点击仿真工具栏中的“Break”按钮来手动地结束仿真。但是,如果此时需要仿真的设计比较复杂,则仿真器在运行仿真时会耗费电脑大量的CPU 和内存资源,此时有可能会造成电脑卡顿甚至死机的情况。所以,如果设计比较复杂,且没有在TestBench 语句中加入 s t o p 或 stop 或 stop或finish 命令,最好不要轻易点击Run all 命令。

• Run For:运行特定的一段时间。紧随在后面的两个文本框用于设定仿真时长的数值大小和时间单位。

• Step:按步运行仿真,每一步仿真一个HDL 语句。

• Break:暂停当前仿真。

• Relaunch:重新编译仿真源并重新启动仿真。在使用Vivado 仿真器来调试HDL 设计时,您可能会根据仿真结果来对您的HDL 源代码进行修改。在修改完HDL 源代码后,可以点击Relaunch 按钮来重新加载UUT 设计和TestBench,以重新对修改后的HDL 源代码进行仿真。此时就不需要再关闭并重新打开仿真器了

在刚打开仿真器时,仿真器会首先将TestBench 中的信号加入到波形窗口中,并执行一段时长的仿真,仿真的时长由Settings 设置窗口中的参数值指定,如下图所示:

此时就可以看到波形窗口中就出现了波形,我们点击波形窗口中的显示工具栏中的“Zoom Fit”按钮,波形就会自动缩放到整个窗口,如下图所示:

然后查看之间的时间之类的。