1.介绍

本文章旨在帮助HNU的同学更优雅的完成数电的FPGA毕设(使用DE2-115),文章将涉及完成FPGA项目需要掌握的知识,资源分享以及一些关于完成项目的经验指导。大家快快搬好小板凳,准备发车吧(doge)。

2.基础知识学习指导

Verilog

想要完成FPGA的项目,那必不可少的就是

Verilog这个硬件描述语言,可以说Verilog是一切一切的基础,下面将给出如何更好的学习Verilog

视频推荐:【三天入门verilog速成】 https://www.bilibili.com/video/BV1iv4y1F7Km

看完这个视频,基本上就可以上手写代码了,当然建议看完以后再根据UP主的PPT自己再整体过一遍,这样就差不多了,下面这个链接是PPT的百度网盘链接

链接:https://pan.baidu.com/s/1mnE-7S4ymgYH8GBsk41v8w?pwd=i81l

提取码:i81l

Quartus下载

quartus 18.1

下载链接:https://pan.baidu.com/s/1i0sjRkMIFU693LjjbEePOA

提取码:delp

链接放这了,老师分享的,有需要的自取,本篇教程也都是根据quartus 18.1来写的

Quartus使用

Quartus是一款非常强大的写FPGA的软件,如果是第一次接触FPGA就不用考虑那么多了,无脑选择Quartus即可。

下面是完成项目时在Quartus里会用到的板块,基本涵盖了所有的需求.

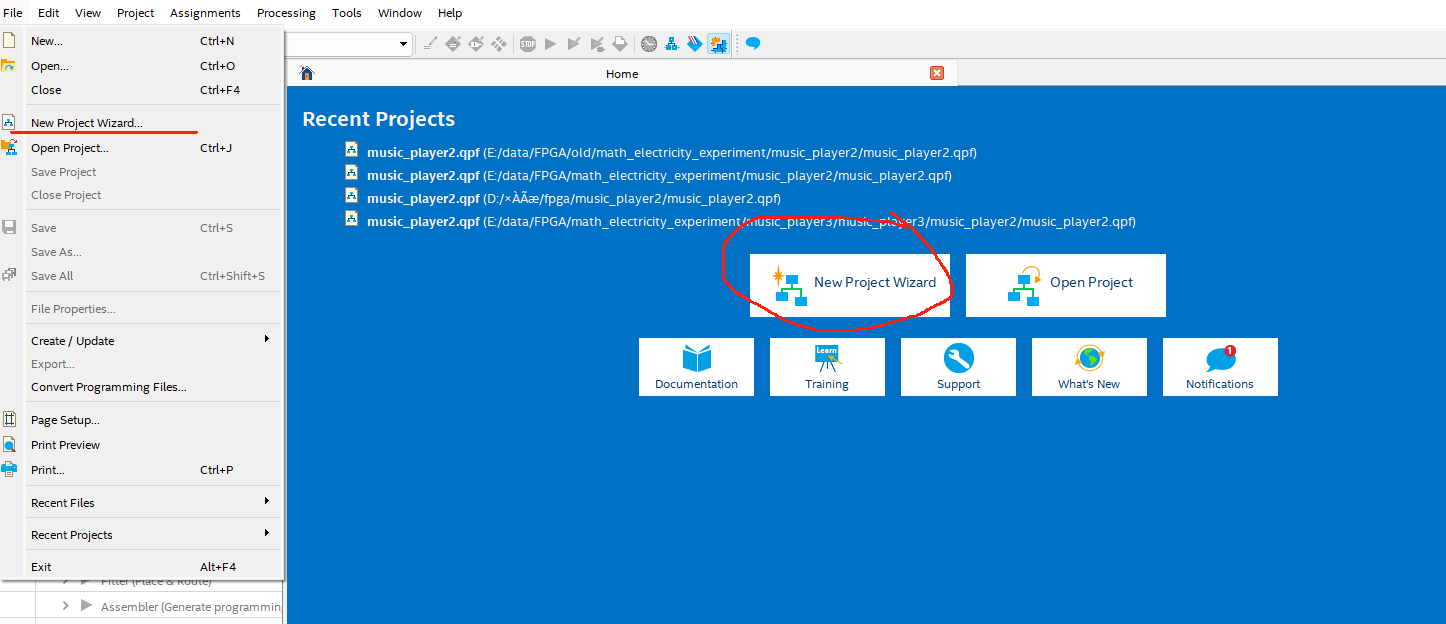

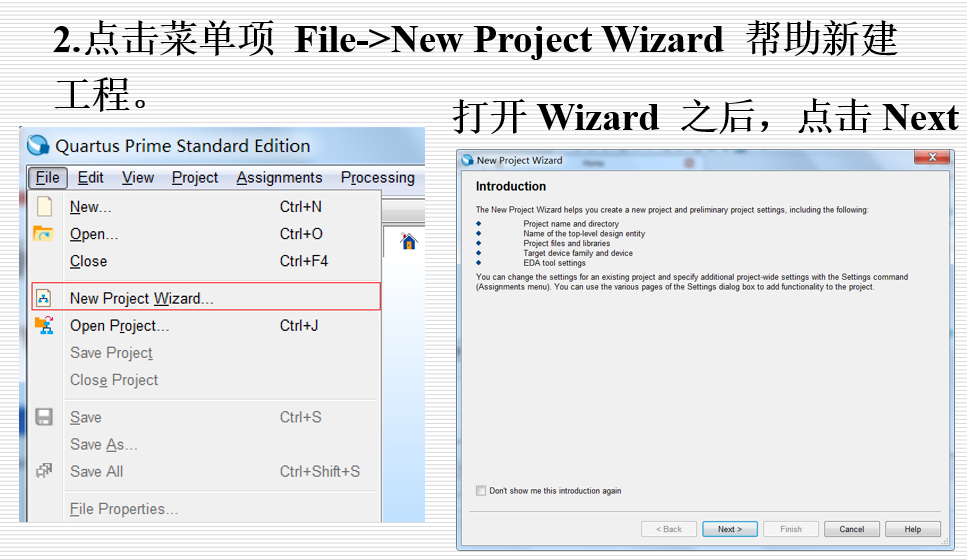

- 新建项目

这两个地方都是新建项目,针对DE2-115的建项目中需要注意的点,在后面会提到,会将整个流程带大家走一遍

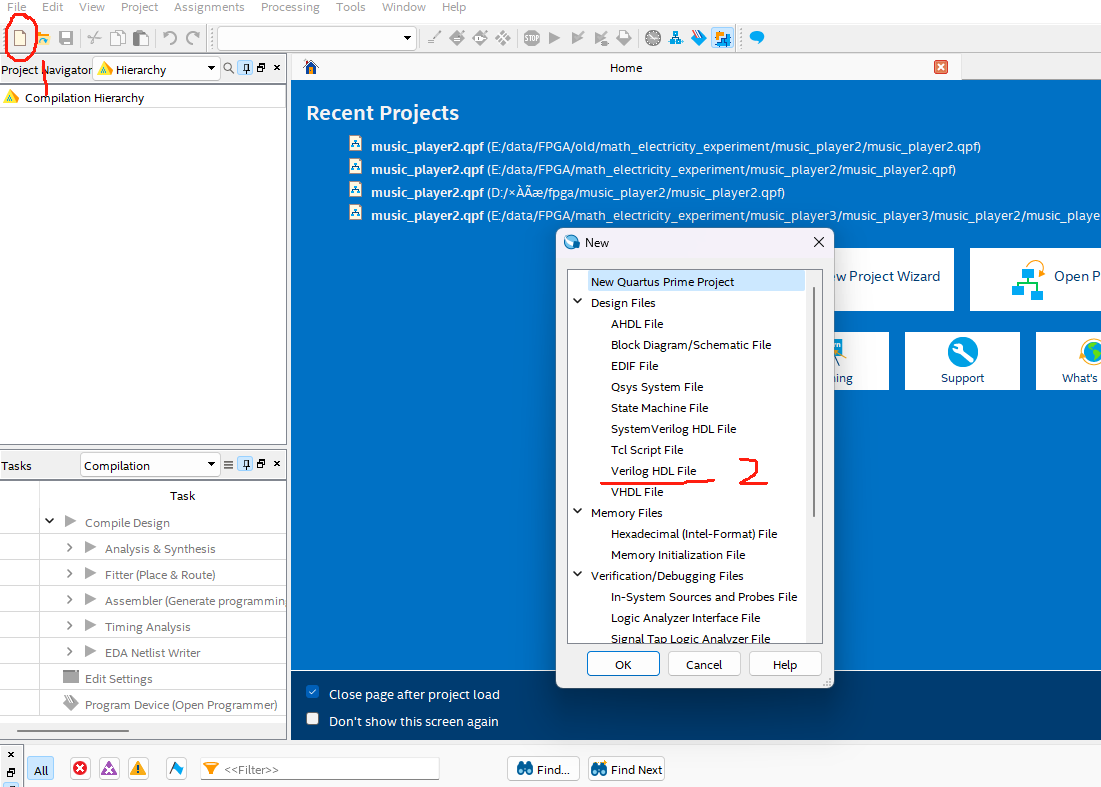

- 创建verilog文件

如图,按顺序点击,即可创建Verilog文件,保存时注意要保存到创建好的项目的目录里去,不然非常容易乱.

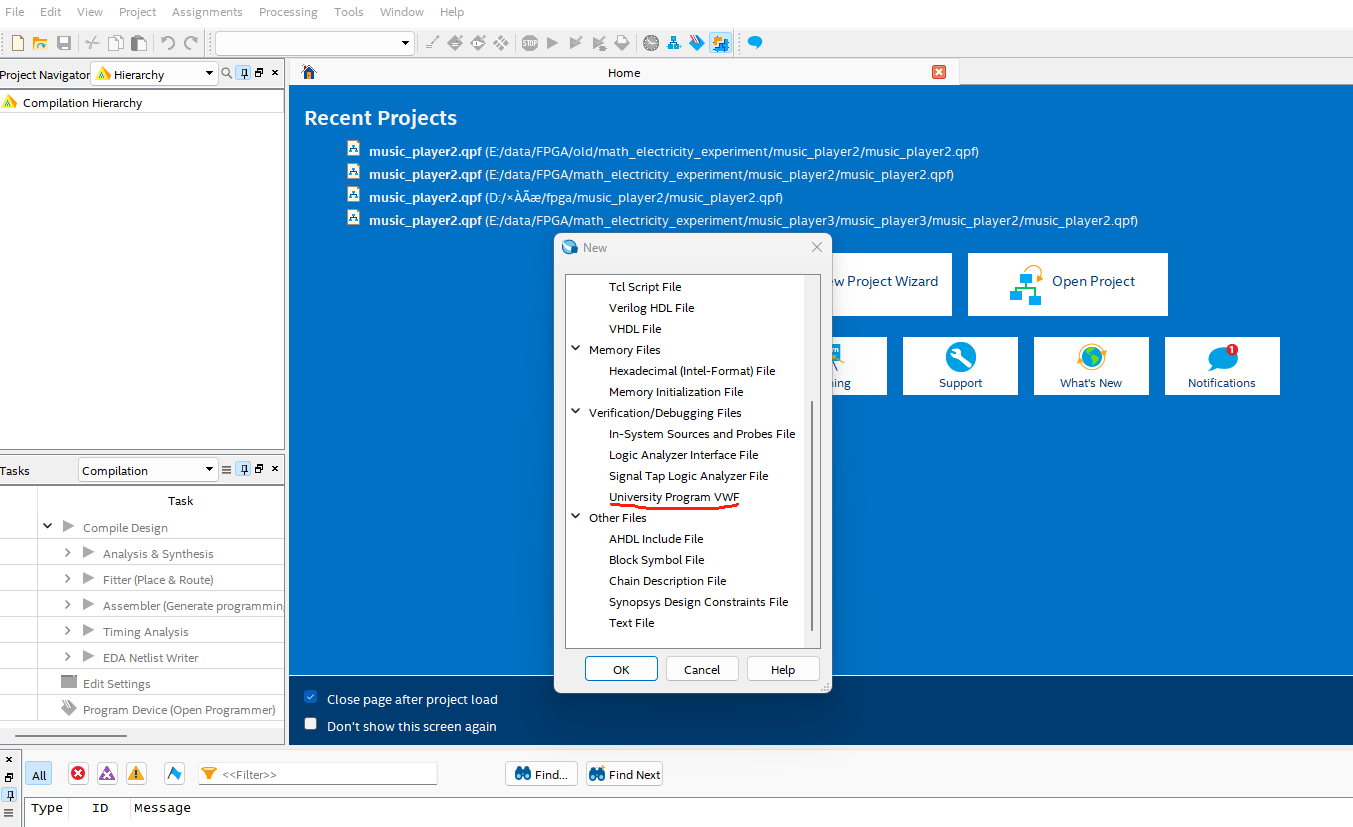

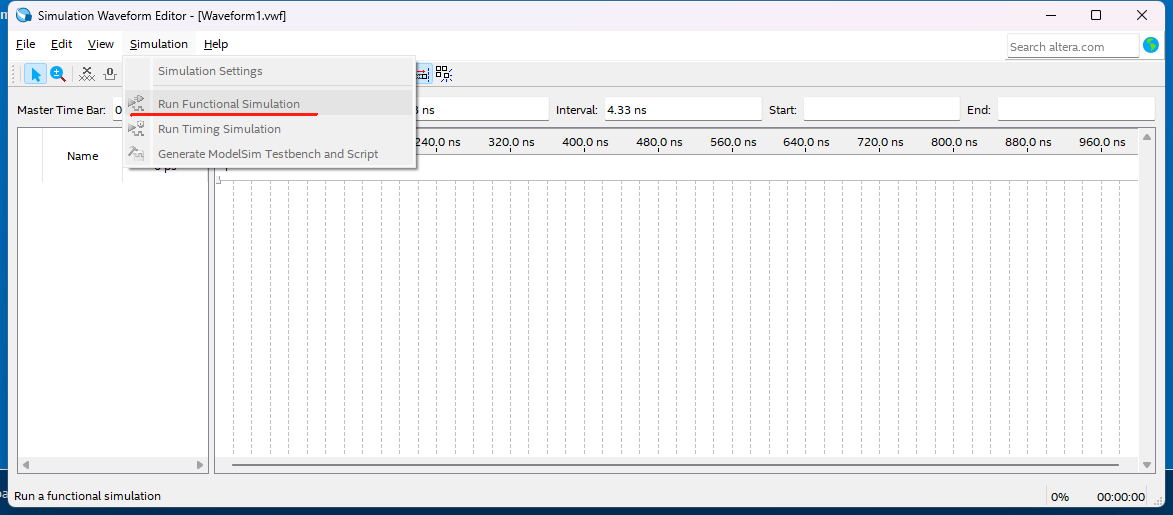

- 创建波形仿真文件及使用指南

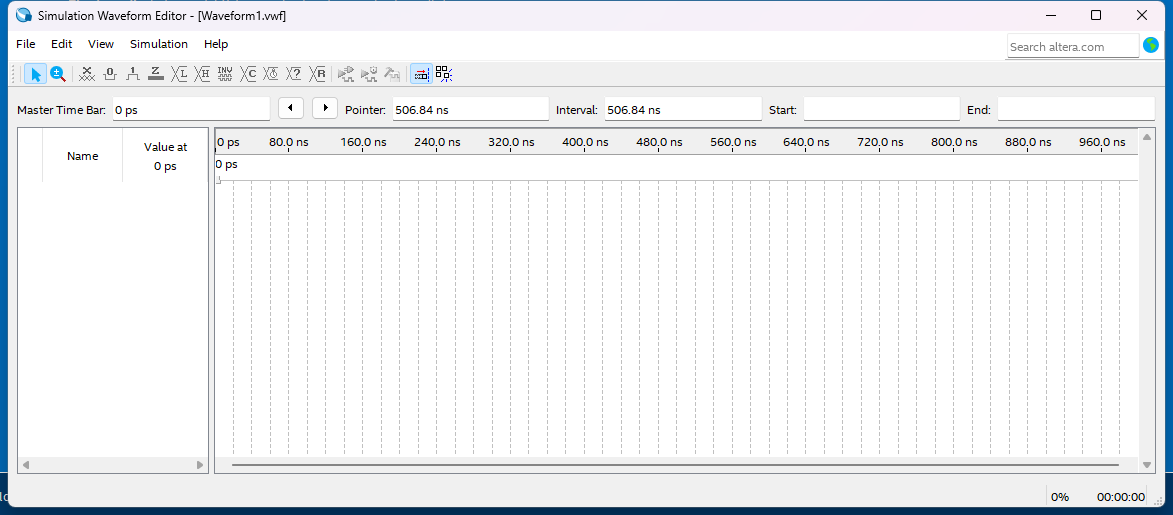

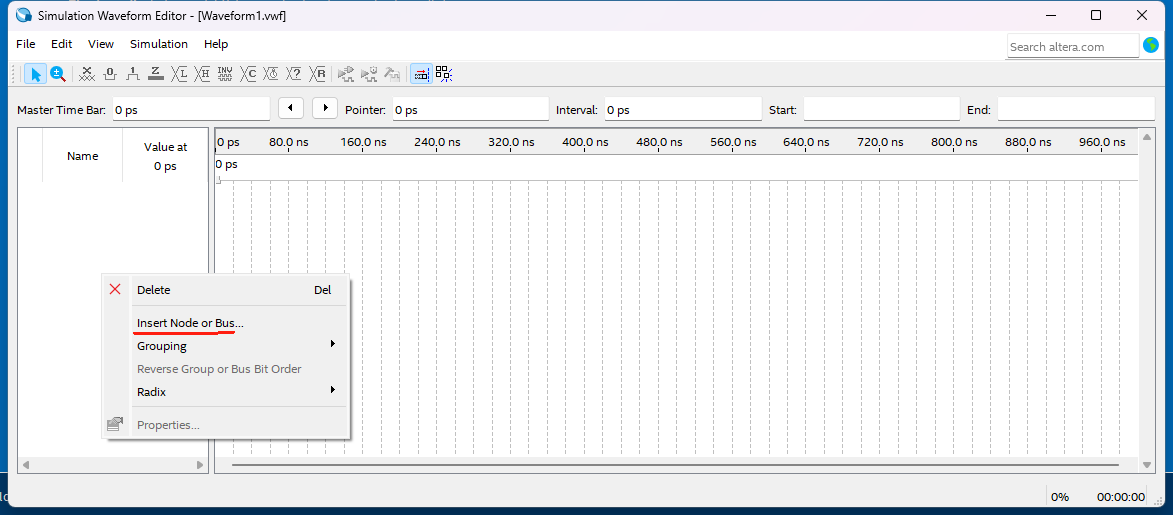

同样是上面的操作,在这个小窗口里往下翻,点开如图所示的文件,即可看到下面的界面.

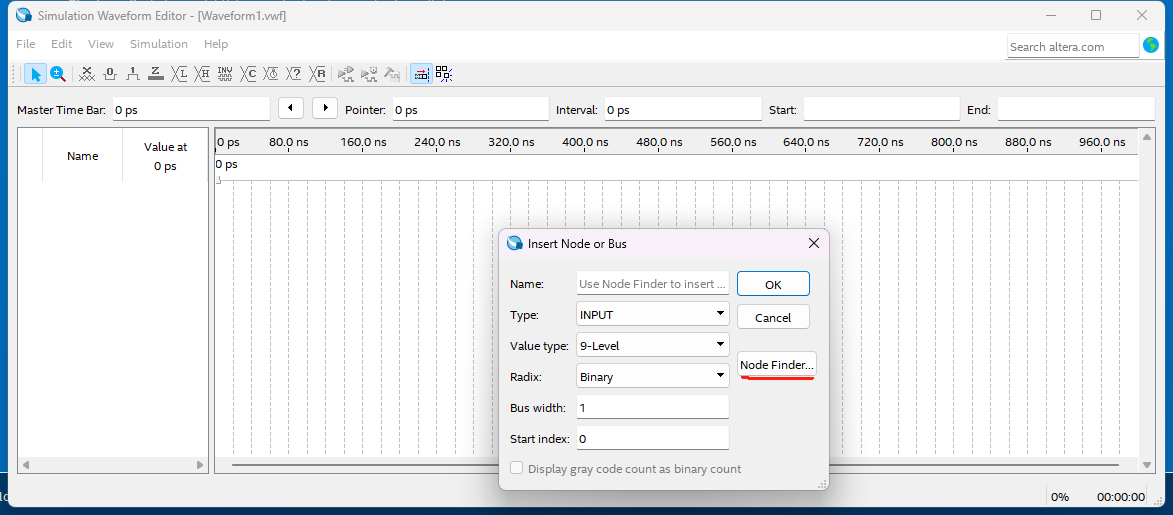

若要添加信号,则可跟随下面的图示来操作

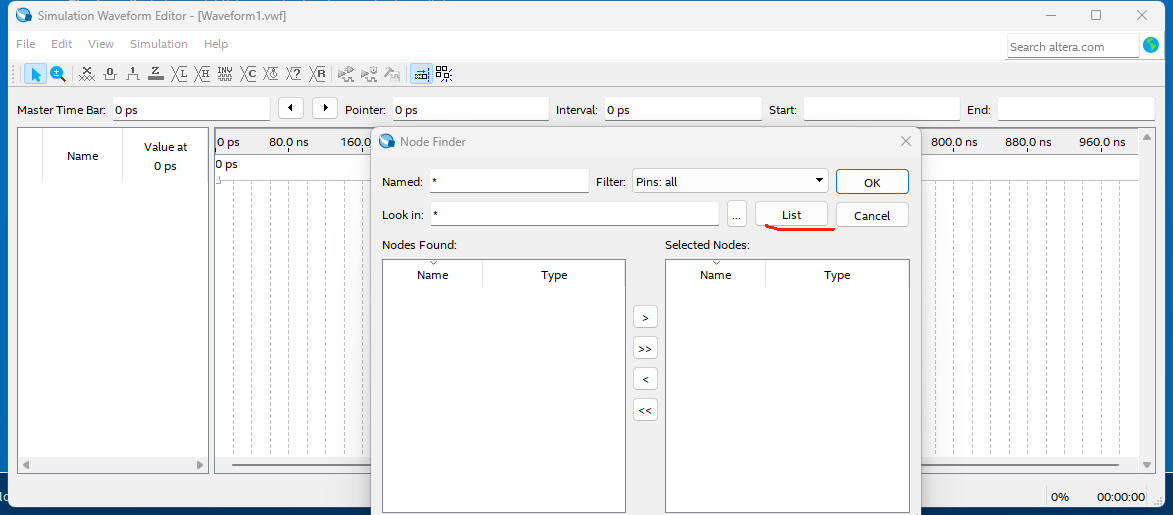

到这边选择List,有的信号下面会一一显示出来,选择需要的信号添加即可.

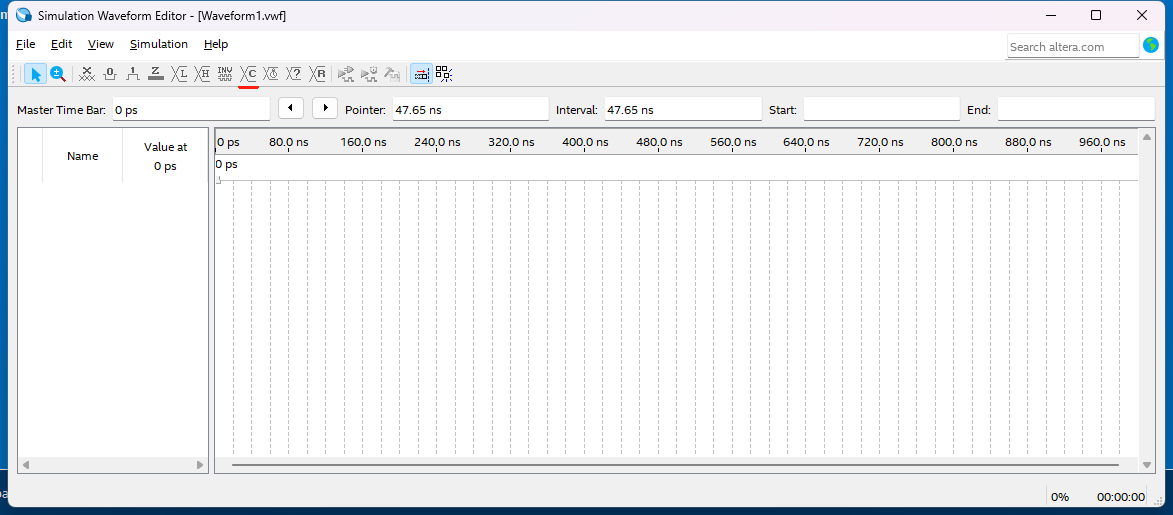

添加完信号后,可指定各个输入信号input的波形,选择好信号后,点击上图里面的C图标,即可给出脉冲。

当全部输入信号的制定好以后,点击Simulation即可启动仿真

注:我这里是因为没有打开项目,所以是灰色的。

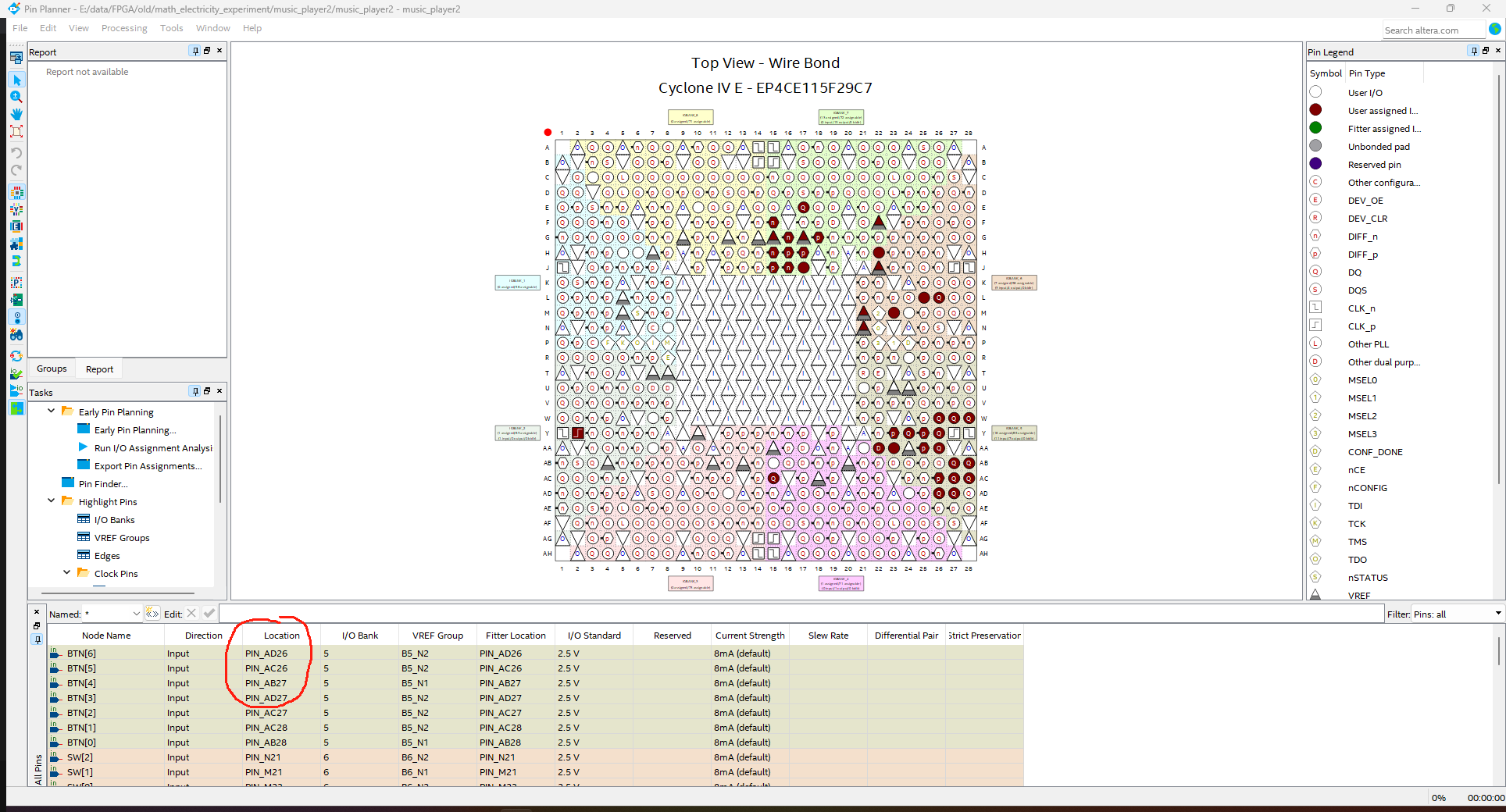

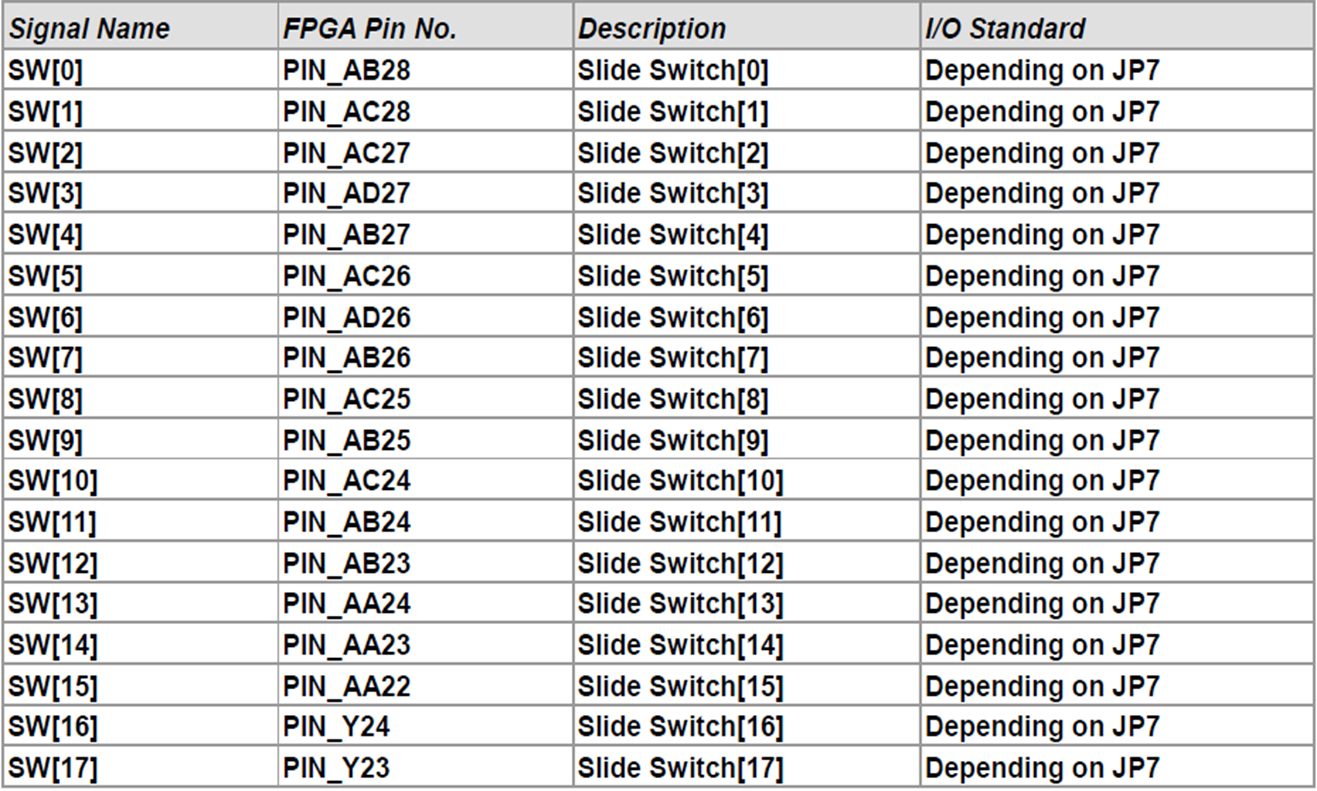

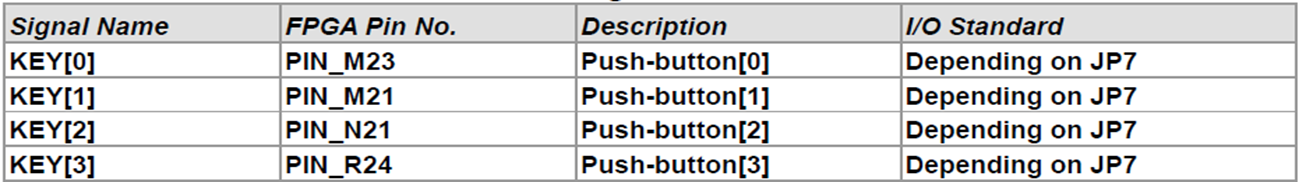

- 引脚分配

写好代码后,如果想要部署到相应的FPGA的板子上,那么就需要分配引脚.

点开如图所示的按钮,即可进入到分配引脚的界面,如下图

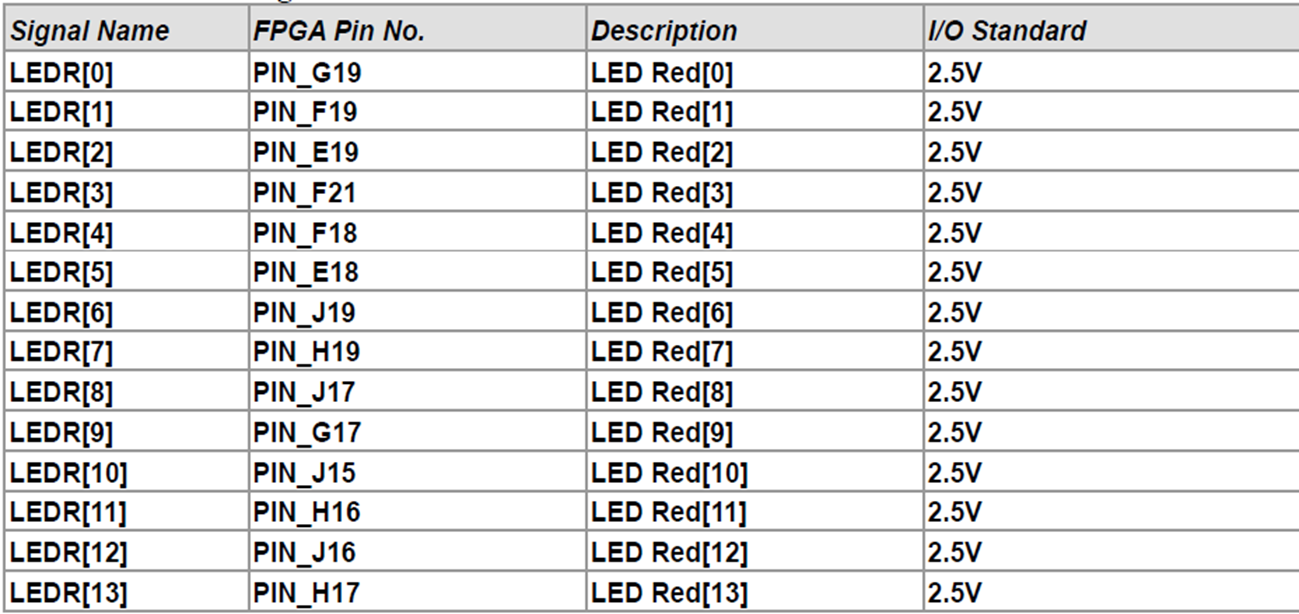

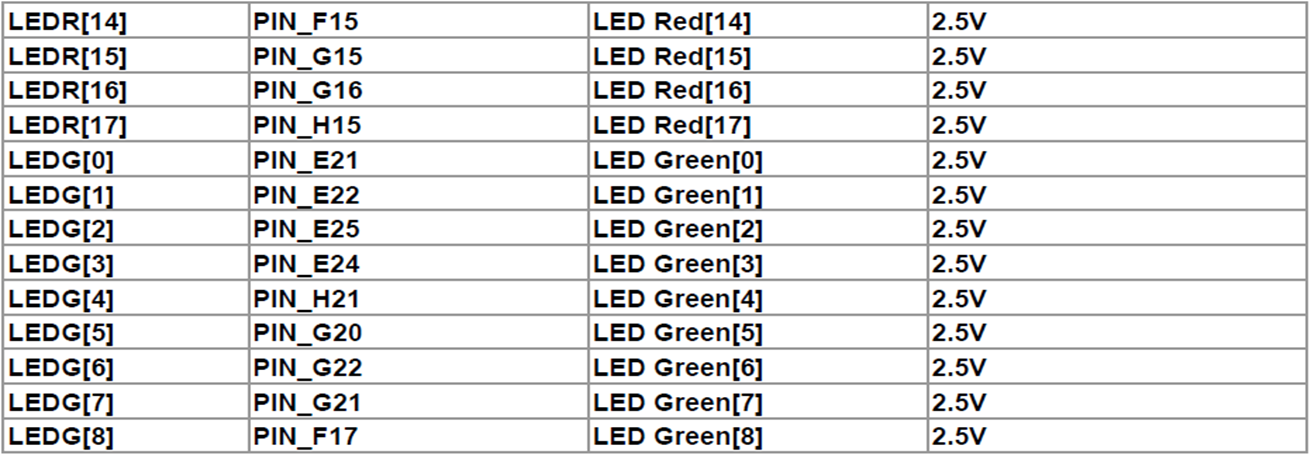

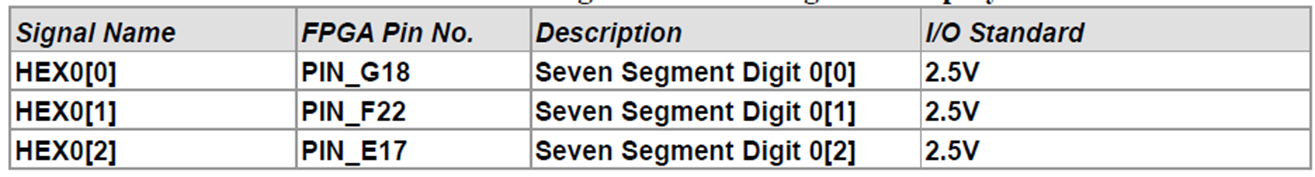

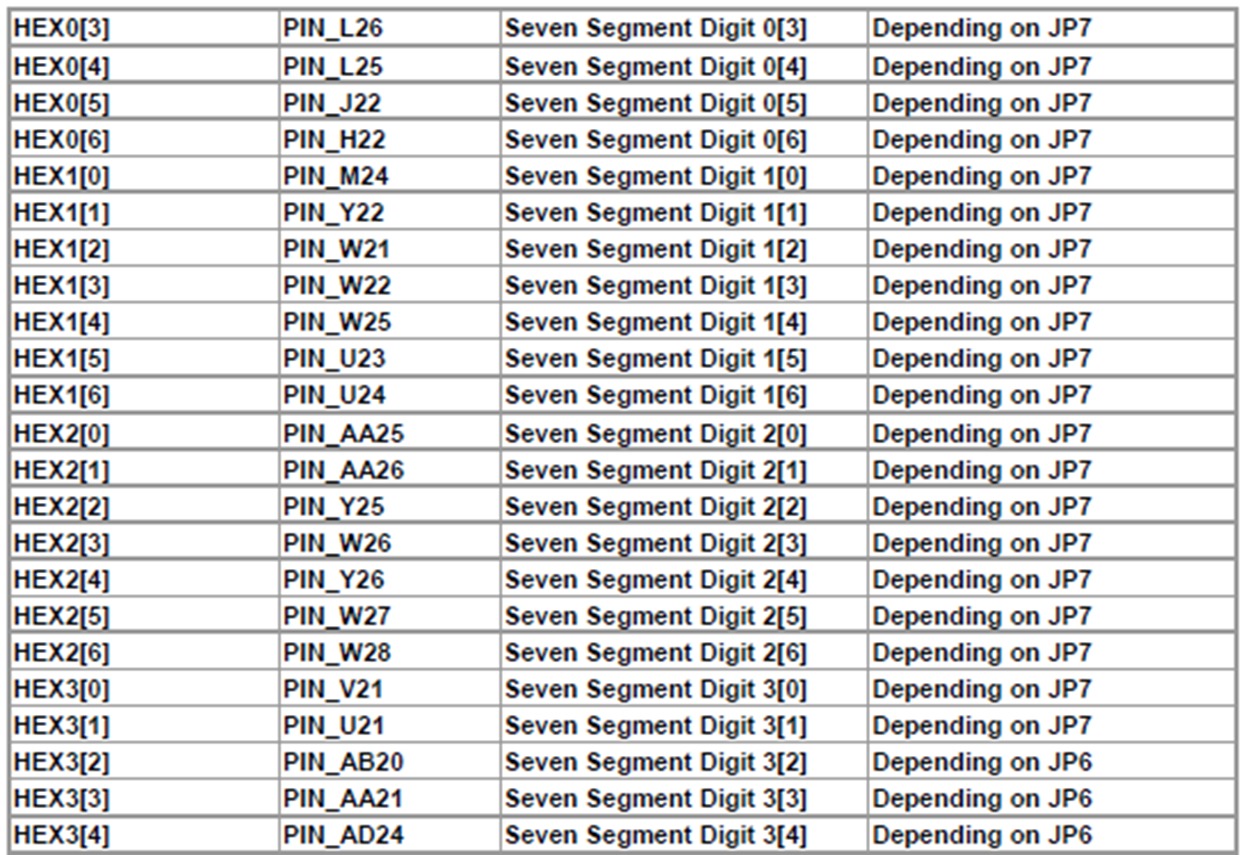

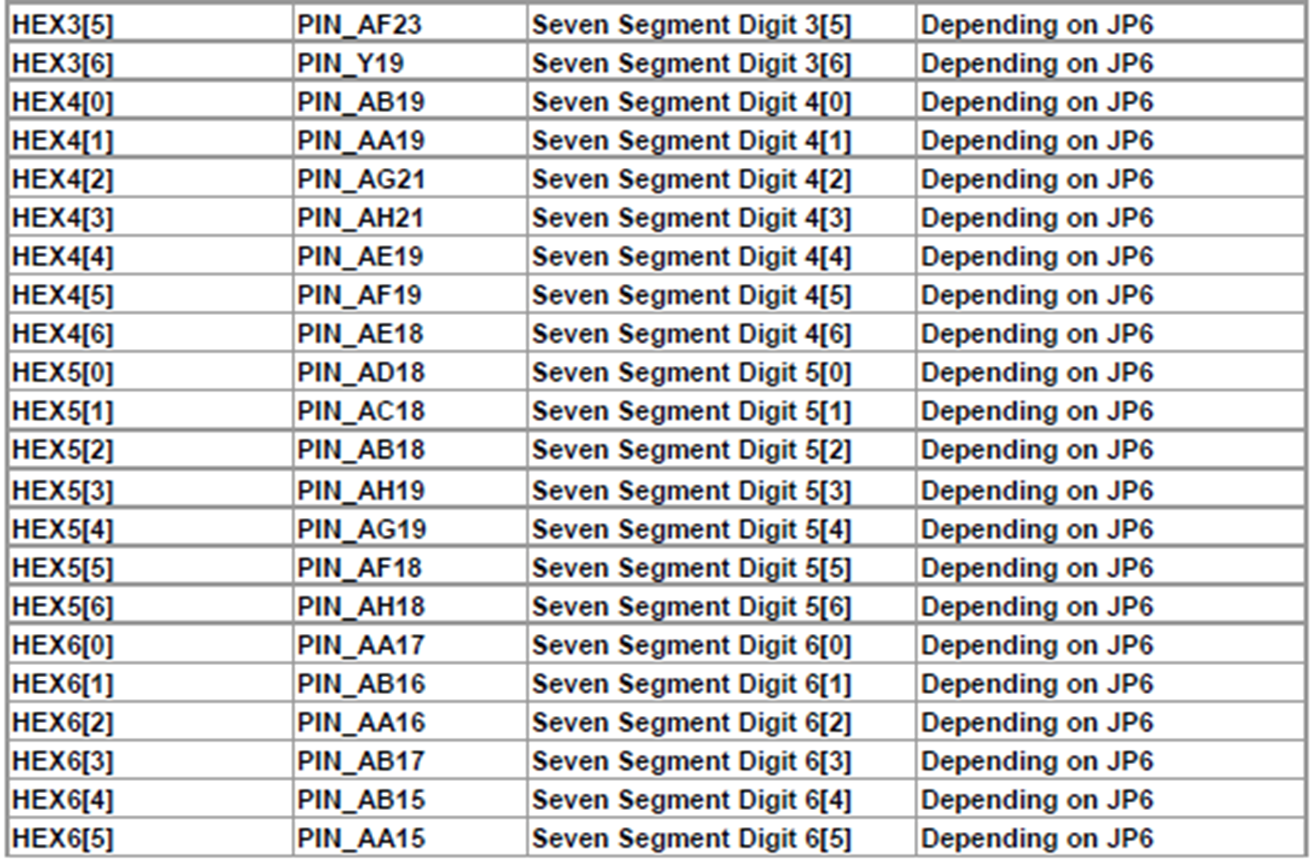

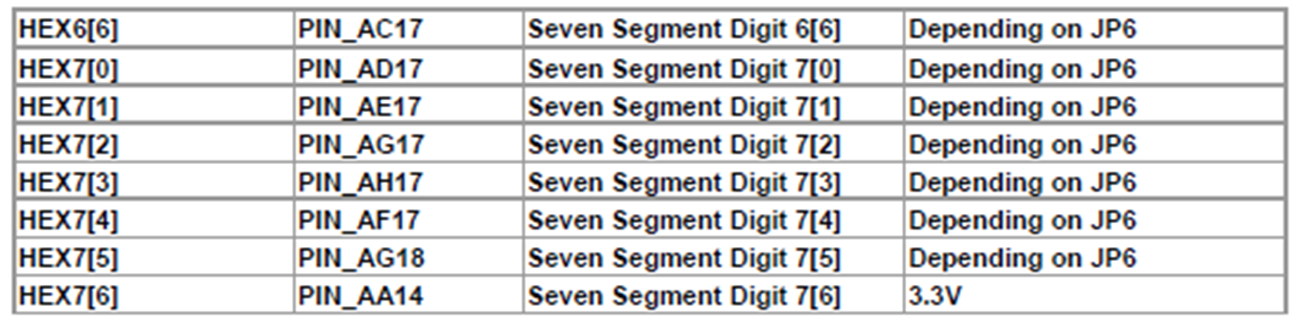

可在Location里分配到实际的引脚里,下面是DE2-115的引脚对应表.

上面是常用的引脚分配,如果想要了解更多,可以看我下面分享的这个pdf文档

链接:https://pan.baidu.com/s/1in7MwdqZ6lGI_f-FRDiMsg?pwd=eqtx

提取码:eqtx

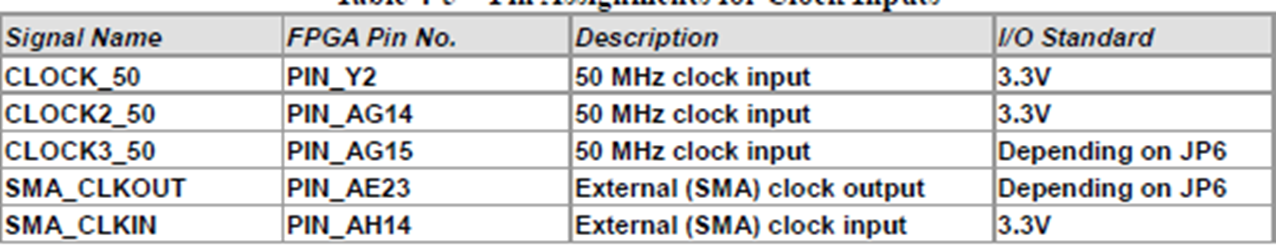

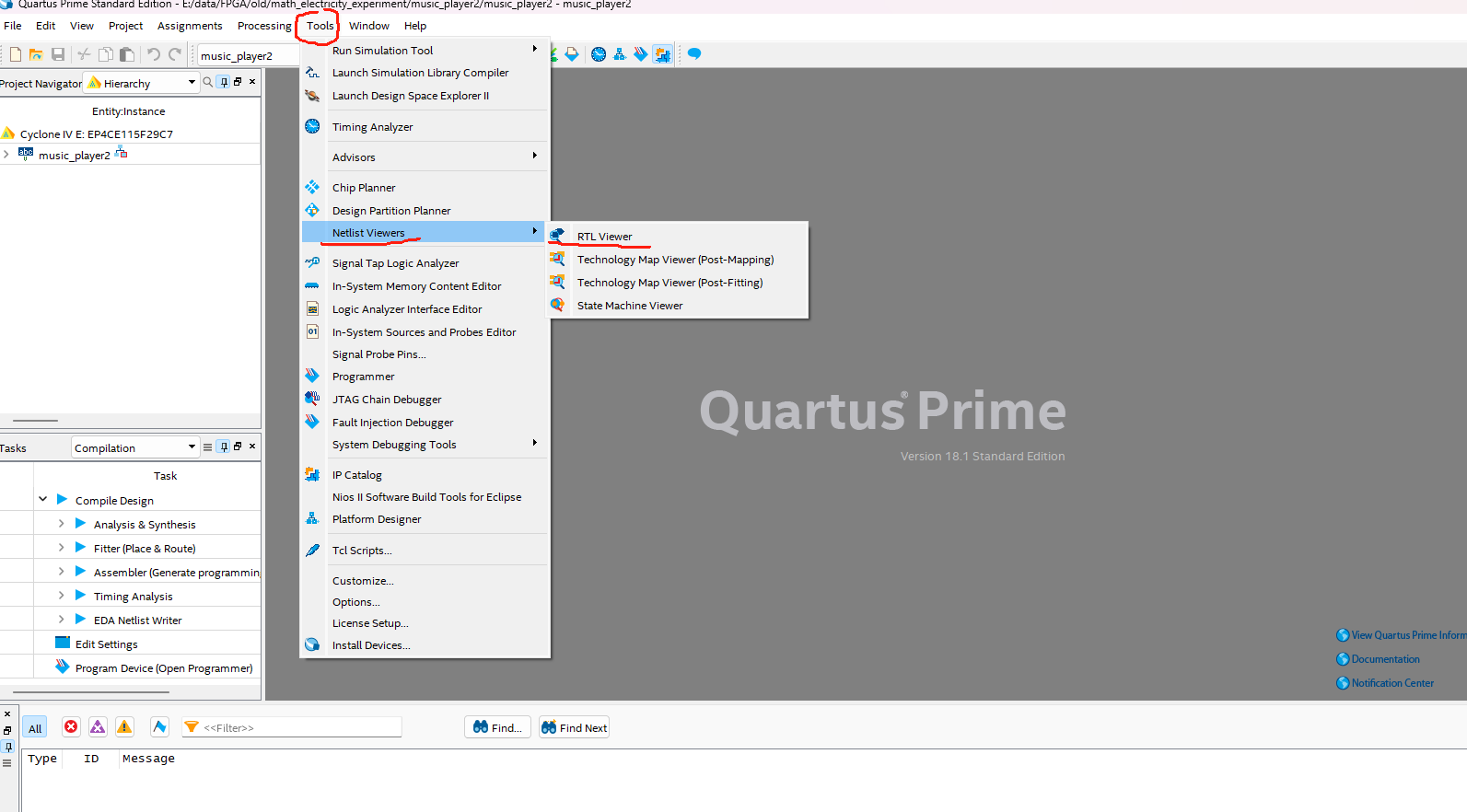

- 图生成

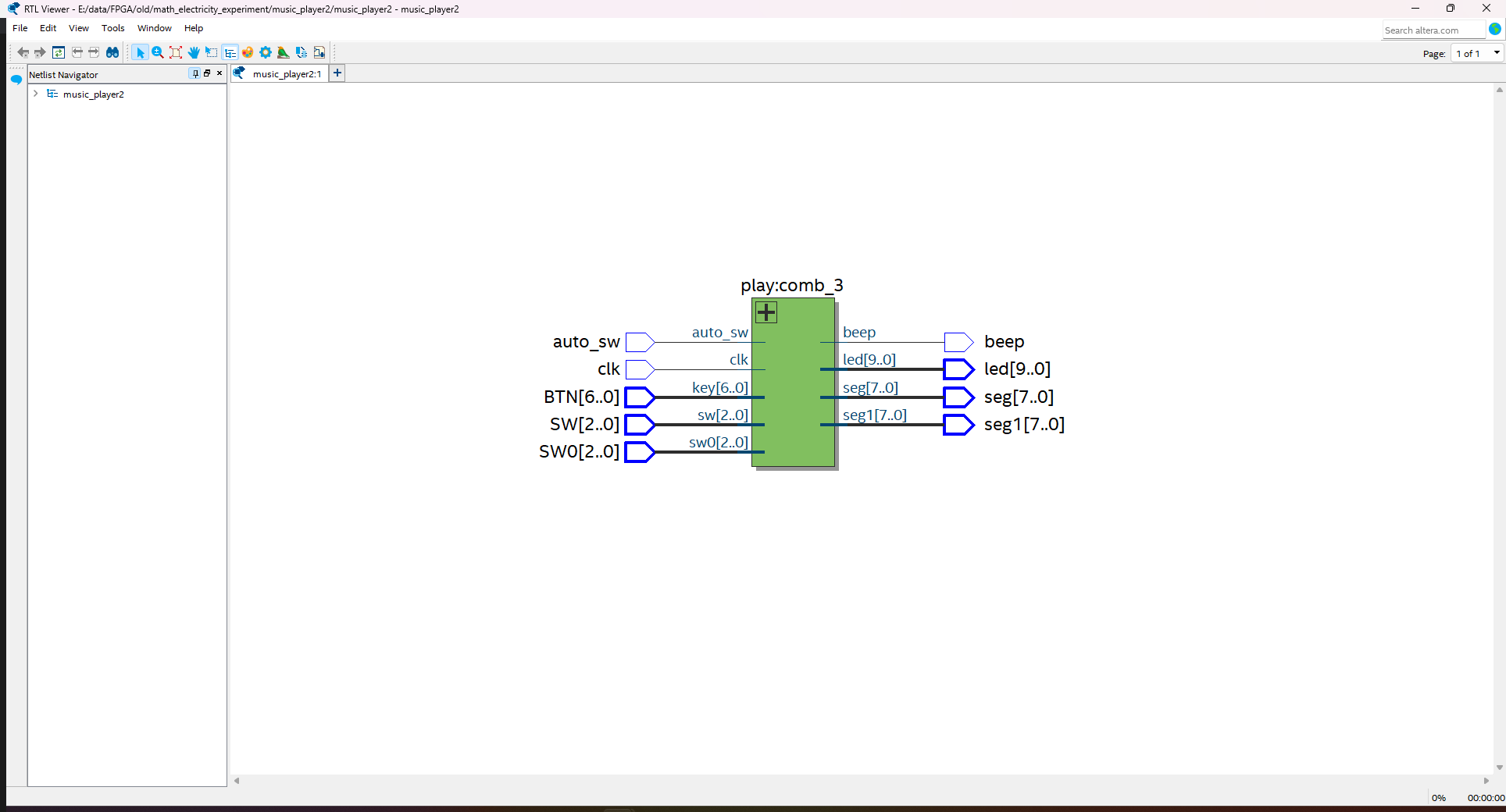

Quartus中提供了非常方便的图生成工具,如果自己的老师有要求的话,可以根据下面的步骤来生成对应自己代码的图

点开即可查看图,如下

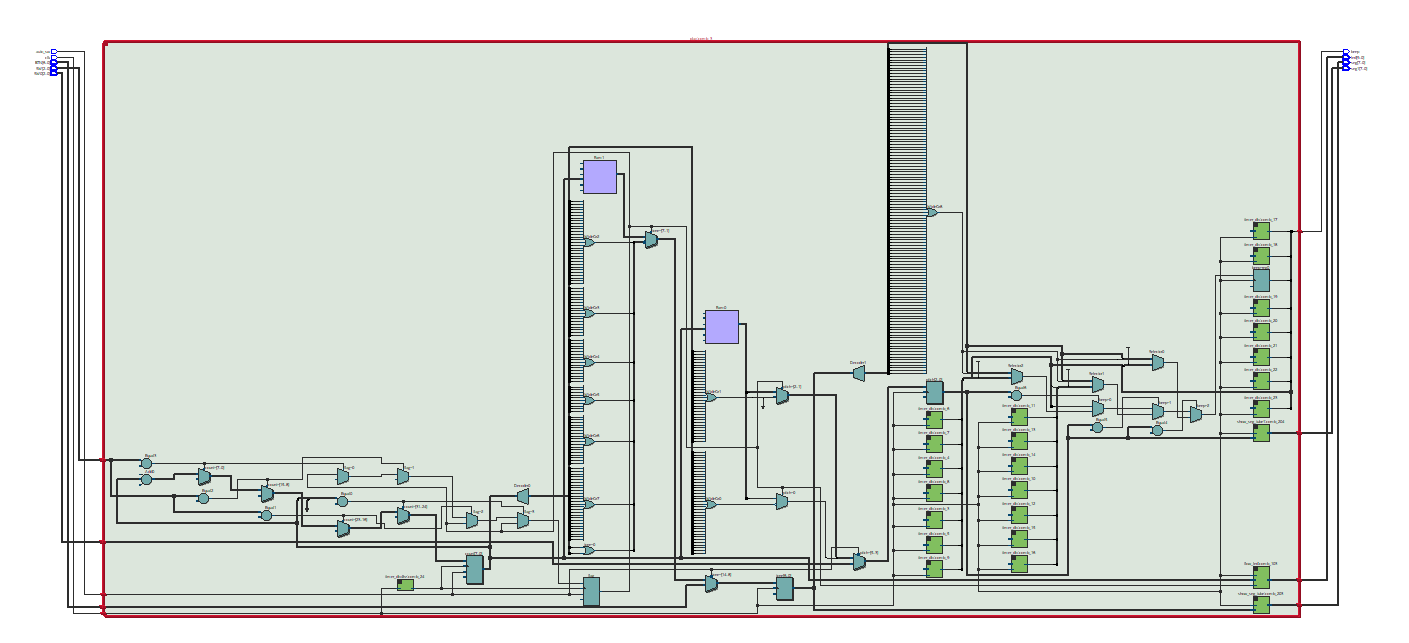

还可点开模块看里面的细节,如下

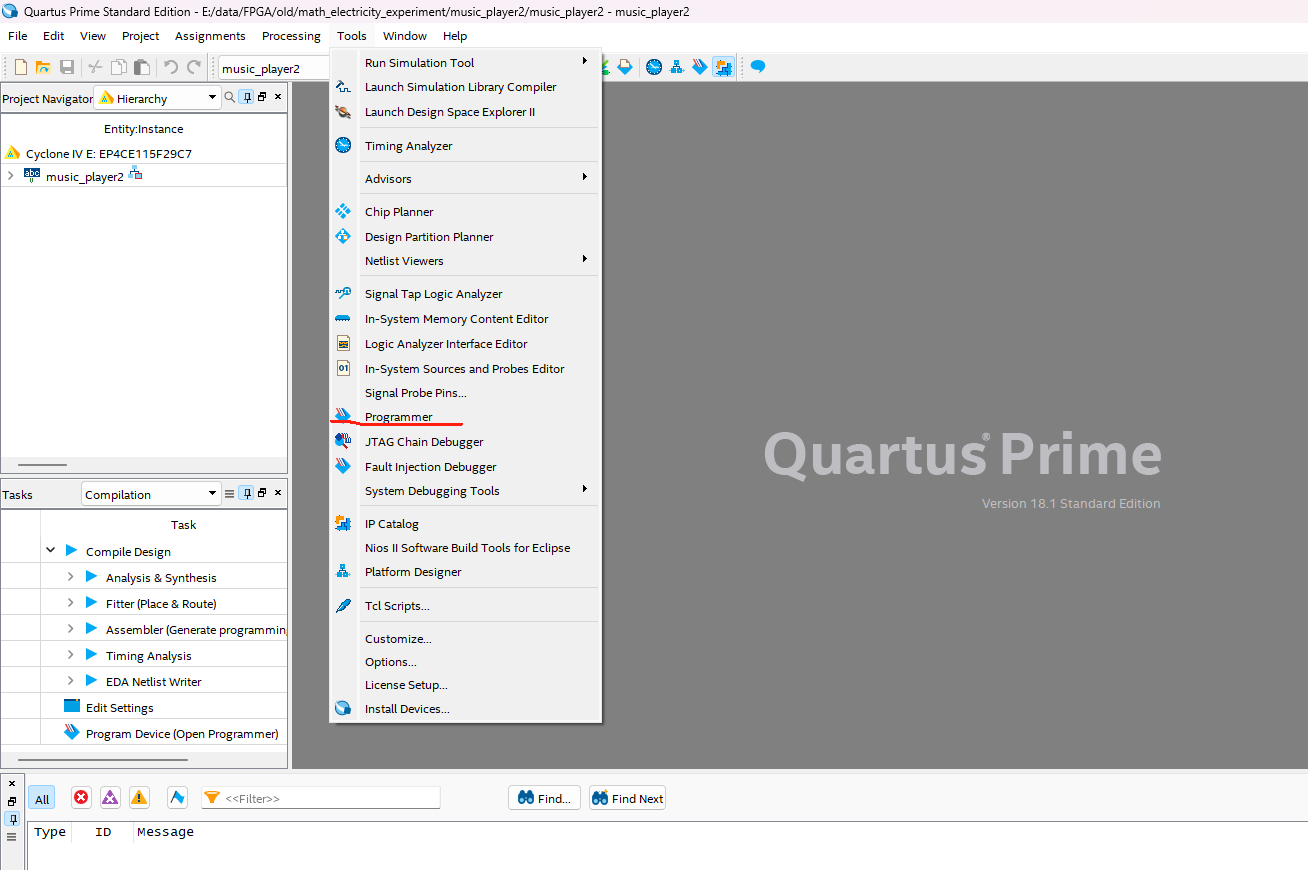

- 烧录

代码整个写完,引脚也分配完,编译通过后,就到了烧录到板子上验证的时候了,如下操作

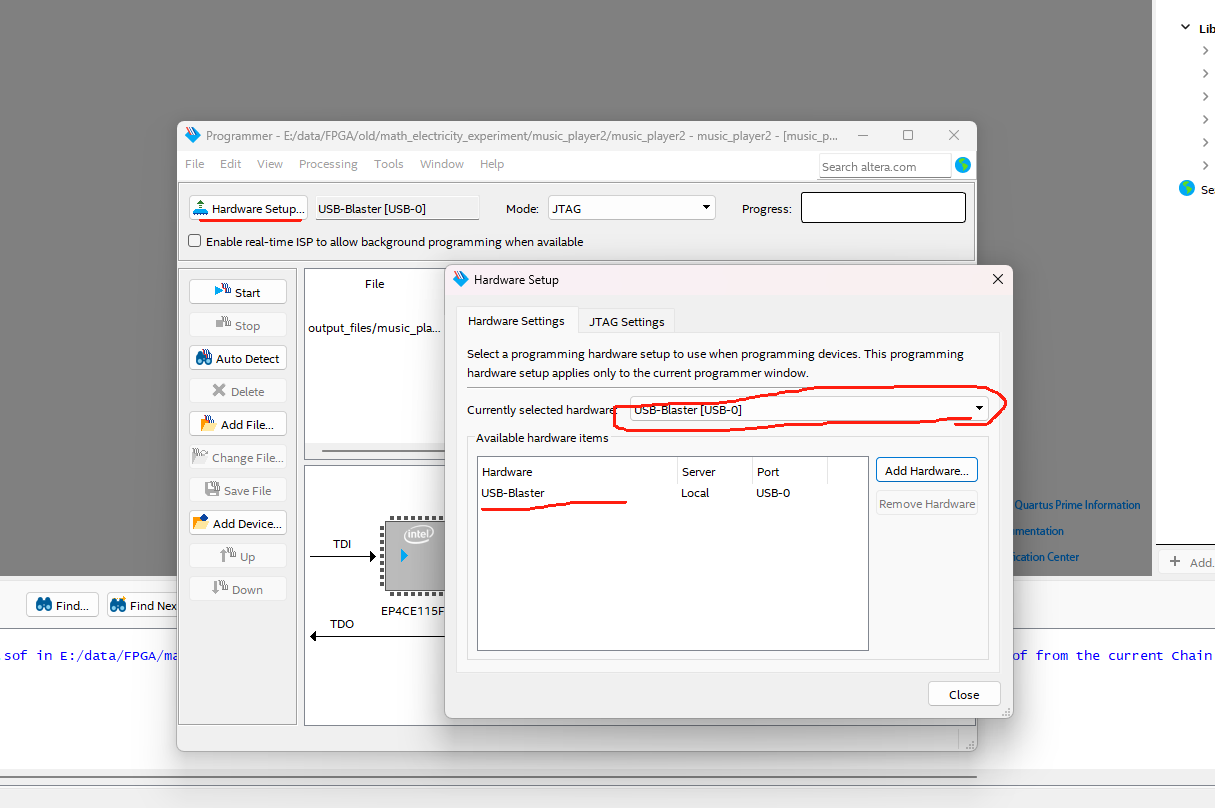

首先应该确认自己的电脑有没有CH340和USB-BLASTER的驱动。

安装方式如下,如果已经有了就可以跳过

CH340

这个去网上搜一个都行,或者点下面的这个链接下载。CH340

USB-BLASTER

这个驱动的安装需要保证先装好了Quartus,然后看这个链接里的教程安装即可[1. Quartus软件和USB-Blaster驱动安装 — 野火]FPGA Verilog开发实战指南——基于Altera EP4CE10 征途Mini开发板 文档 (embedfire.com)

两个驱动都装好后,点击Quartus里的这个按钮,即可进入到烧录界面

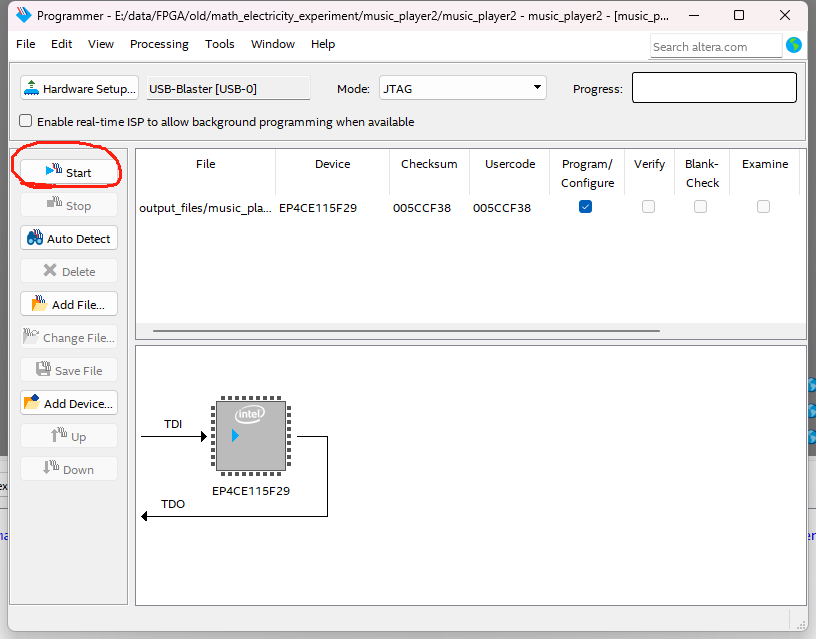

如下图,如果驱动安装没问题,有如下画面

最后,点击Start开始烧录即可

一般情况下,这样烧录进去的代码,fpga断电重启后就会没有,想了解详细的原因的可以看这篇文章。

- 编译

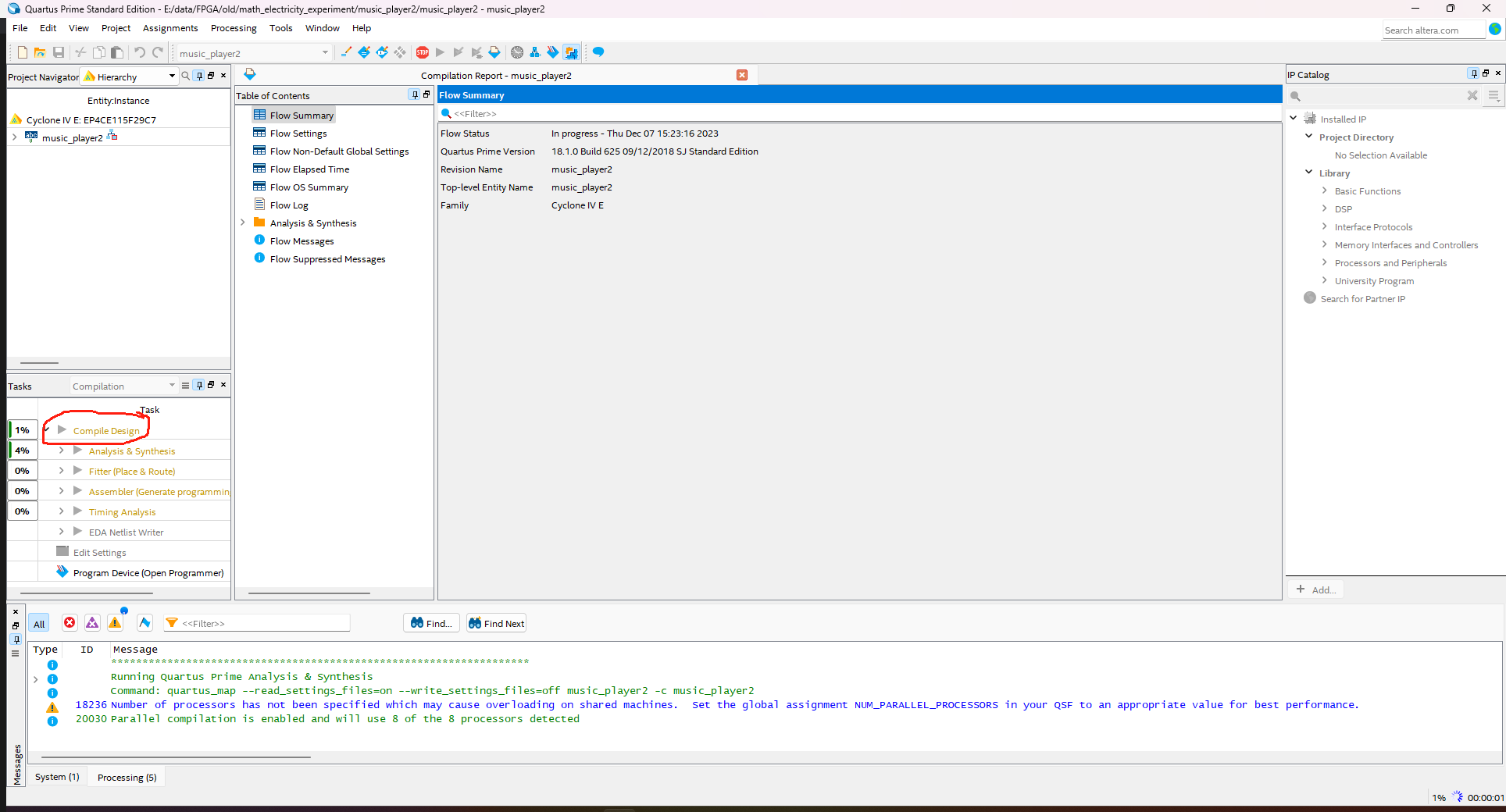

前面讲了好多,好像忘讲怎么编译了,编译其实非常简单,如下

点击一下图中的按钮(也可点击快捷键Ctrl+L),即可开始编译,正常来说编译的时间都挺长的,如果不想等那么长时间,只是想看看有没有问题,那么点击快捷键Ctrl+K即可

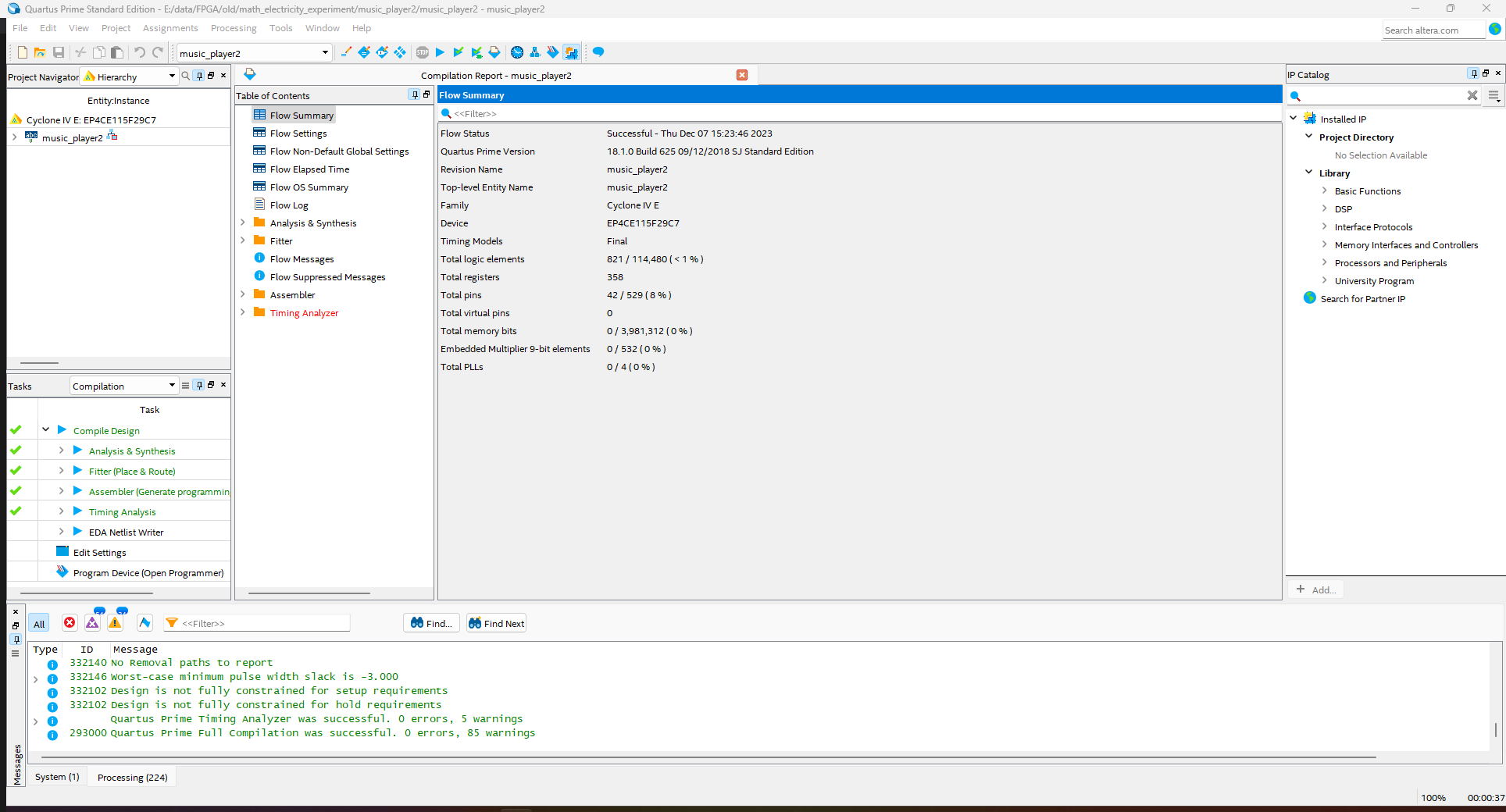

编译成功后,有如下画面

3.基本项目创建流程

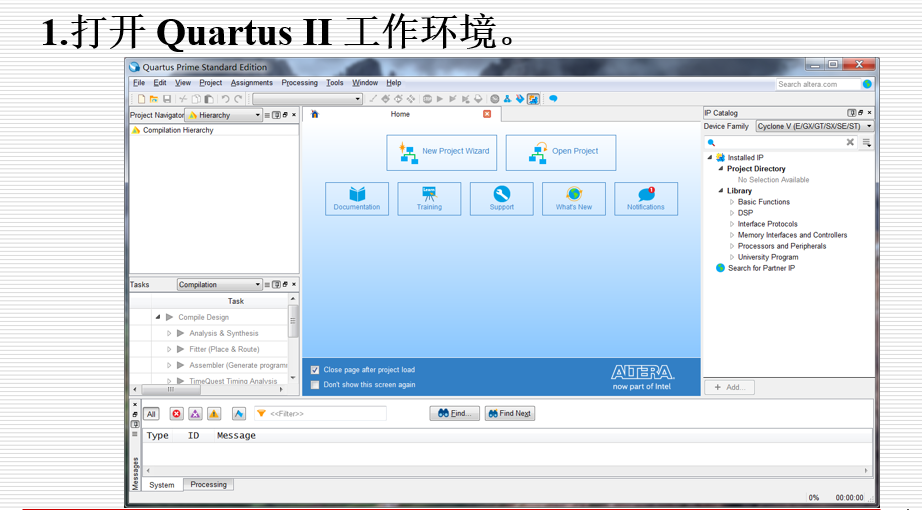

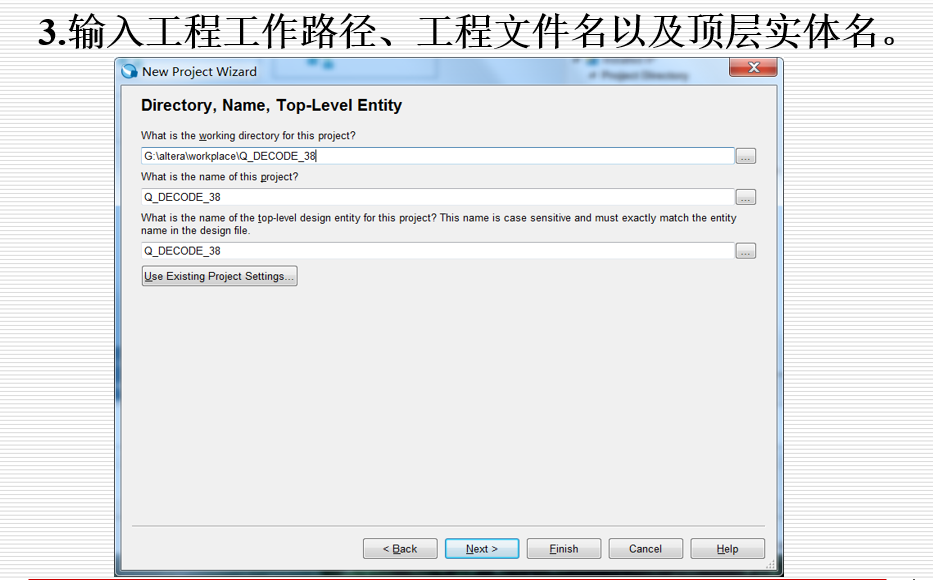

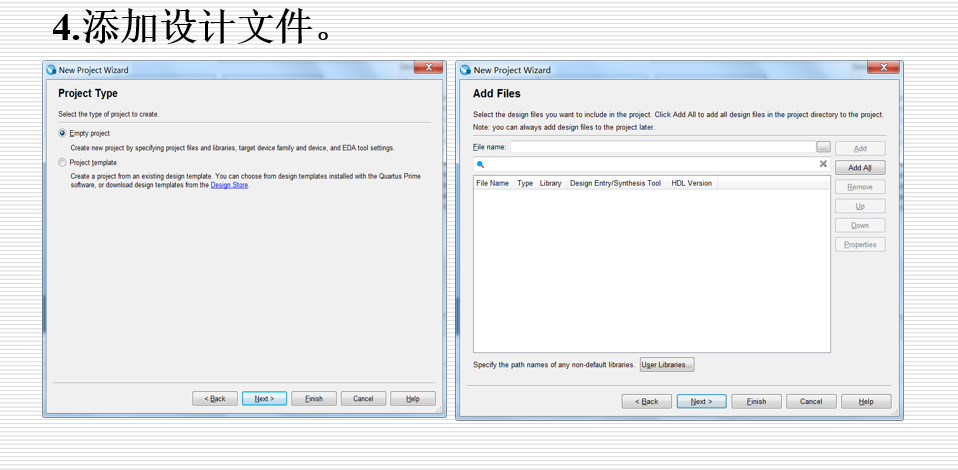

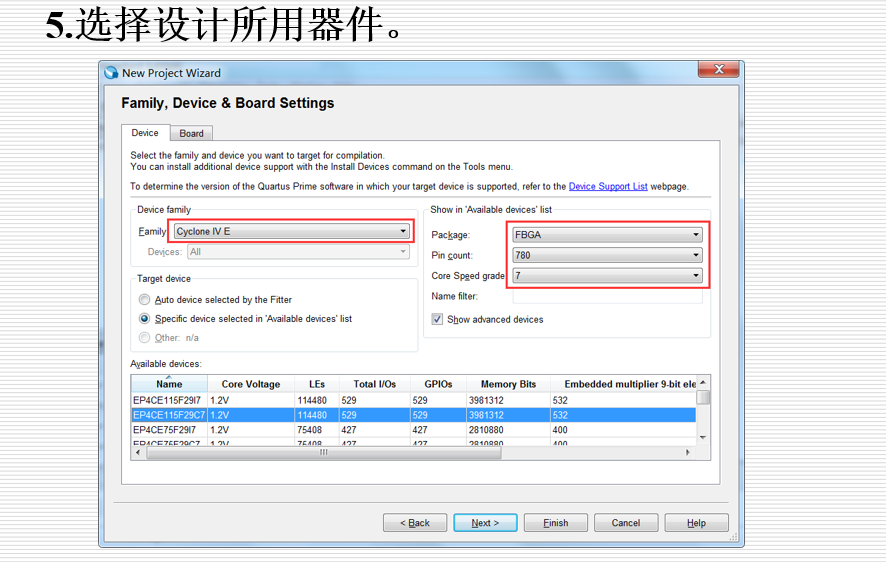

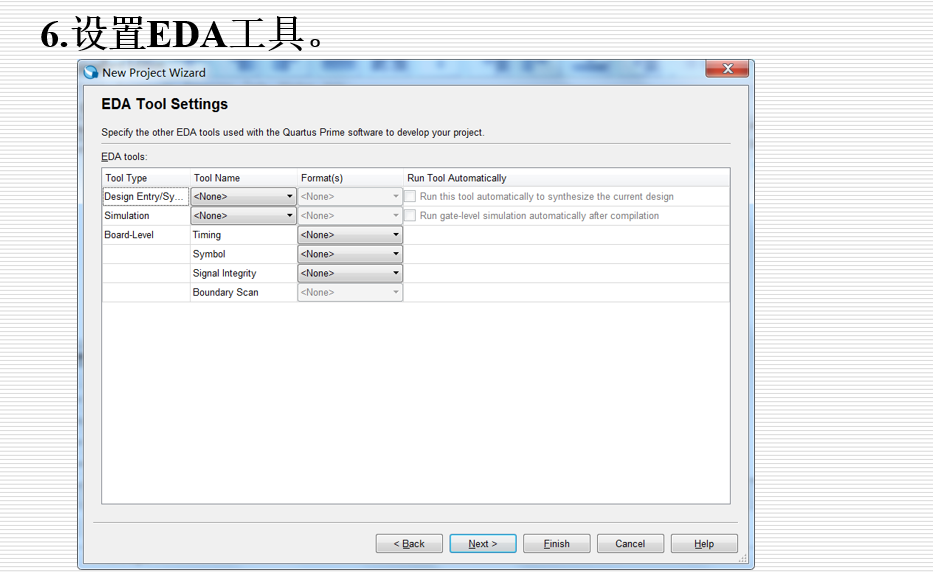

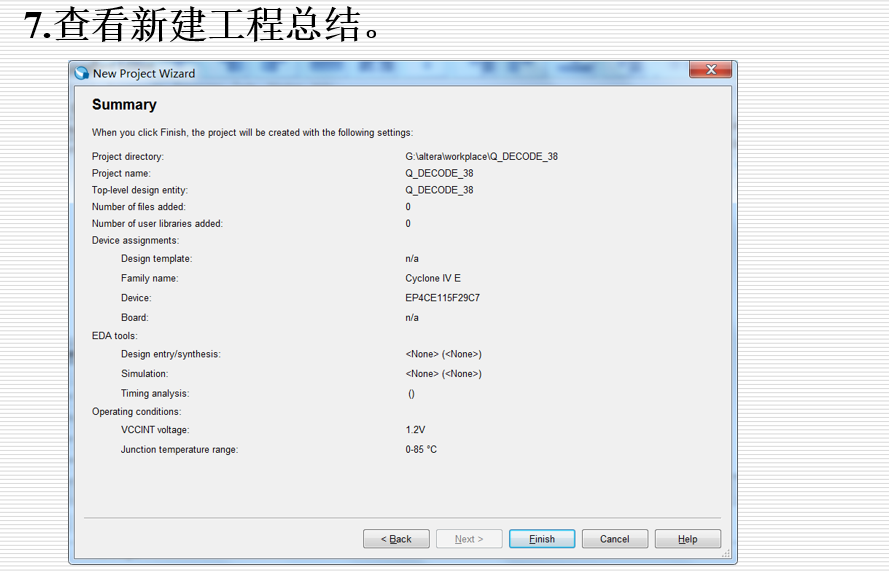

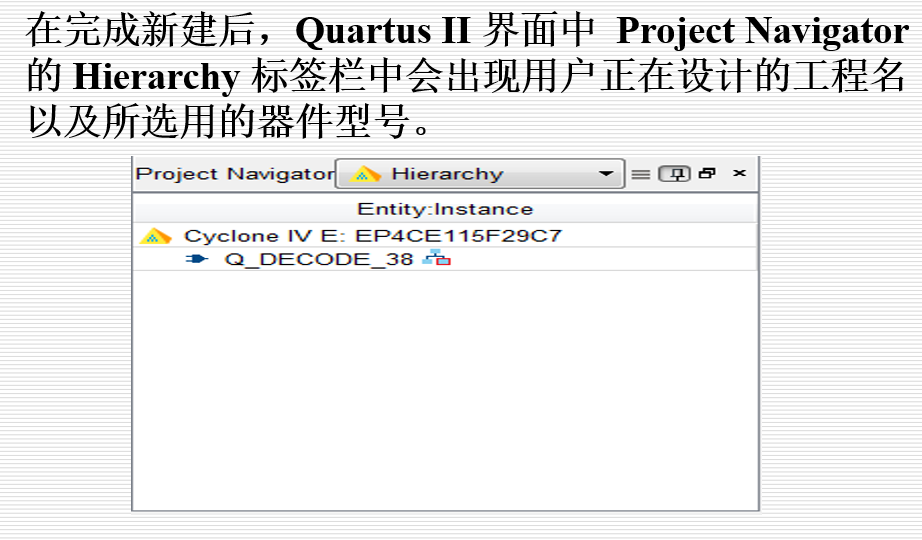

这里我就截老师的ppt里的内容了,按照步骤一步步来准没问题

按照上面的步骤建立好文件后,就可以开始写代码了

标签:烧录,毕设,FPGA,引脚,Quartus,即可,Verilog,HNU From: https://www.cnblogs.com/hnu-hua/p/17882142.html