文章目录

- 一、引脚分布介绍

-

- 1.分类

- 2.电源引脚

- 3.时钟引脚(2根)

- 4.控制引脚(4根)

- 5.端口引脚(32根)

- 二、存储器结构及空间分布介绍

-

- 1.存储器的划分方法

- 2.程序存储器(ROM)

- 3.数据存储器(RAM)

- 三、复位、时钟与时序

-

- 1.复位与复位电路

- 2.时钟电路

- 3.单片机时序

- 四、并行I/O接口

-

- 1.P1口

- 1.P3口

- 1.P0口

- 1.P2口

- 五、中断基本概念

-

- 1.中断

- 2.中断源

- 3.中断的几个概念

- 4.中断实现的功能

- 六、80C51中断的系统结构

-

- 1.中断系统的结构

- 2.中断请求标志

- 3.中断的优先级(默认)

- 七、定时/计数器的结构及原理

-

- 2.结构

- 2.工作原理

- 3.工作方式之定时

- 4.工作方式之计数

- 4.与定时/计数器相关的SFR

- 七、定时/计数器的工作方式

- 总结

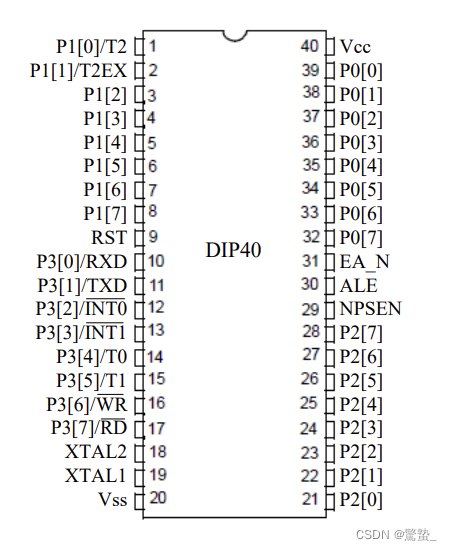

一、引脚分布介绍

1.分类

三类

- 电源及晶振引脚(共4只)

- 控制引脚(共4只)

- 端口引脚(共32只)

2.电源引脚

- Vcc(40脚):电源端,接+5V电源。

- Vss(20脚):接地端。

3.时钟引脚(2根)

- XTAL1(19脚):接外部晶振和微调电容的一端。

- XTAL2(18脚):接外部晶振和微调电容的另一端。

4.控制引脚(4根)

-

RST/Vpp(9脚):复位信号/备用电源输入引脚。

○ 当RST引脚保持两个机器周期的高电平后,就可以使80C51完成复位操作。

○ 该引脚的第二功能是VBp,即备用电源的输入端,具有掉电保护功能。

○ 若在该引脚接+5V备用电源,在使用中若主电源VCC掉电,可保护片内RAM中的信息不丢失。 ○ -

ALE(30脚):地址锁存允许信号输出。

○ 当CPU访问片外存储器时,ALE输出信号控制锁存PO口输出的低8位地址,从而实现PO口数据与低位地址的分时复用。

○ 当80C51上电正常工作后,自动在ALE端输出频率为fosc/6的脉冲序列(fosc代表振荡器的频率)。 -

EA(31脚):外部程序存储器地址允许输入端。

○ 当EA接高电平时,CPU执行片内ROM指令,但当PC值超过OFFFH时,将自动转去执行片外ROM指令;

○ 当EA接低电平时,CPU只执行片外ROM指令。对于80C31,由于其无片内ROM,故其EA必须接低电平。 -

PSEN(29脚):片外ROM读选通信号端。

5.端口引脚(32根)

- P0.0 ~ P0.7 (39 ~ 32脚) —— P0口

- P1.0 ~ P1.7 ( 1 ~ 8脚) —— P1口

- P2.0 ~ P2.7 (21 ~ 28脚) —— P2口

- P3.0 ~ P3.7 (10 ~ 17脚) —— P3口

1、P0口既可以作为普通I/O口,又可以作为外部扩展时的数据总线和地址总线的低8位,分时复用;作为普通I/O口时,外部要接上拉电阻。

2、P1口可以作为普通I/O口使用,内部带上拉电阻

3、P2口可以作为普通I/O口使用,又可作为外部扩展时地址总线的高8位,作为普通I/O时,内部带上拉电阻

4、P3口可以作为普通I/O口使用,又具有第二功能,作为普通I/O时,内部带上拉电阻

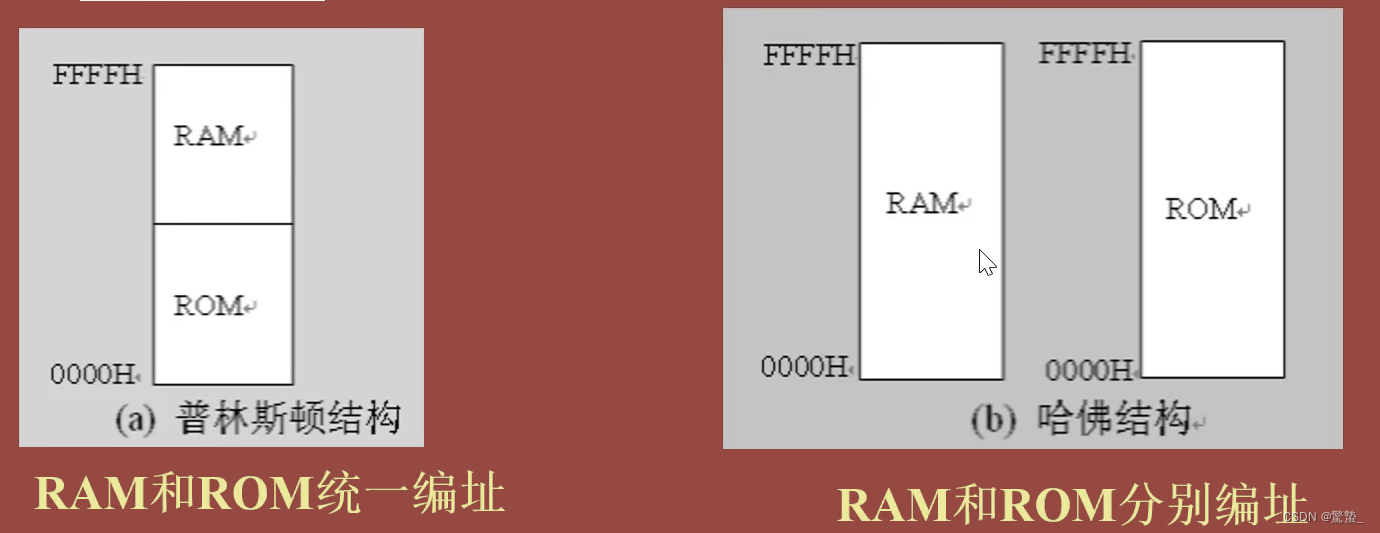

二、存储器结构及空间分布介绍

1.存储器的划分方法

冯诺依曼结构 与 哈佛结构

(51单片机是改进的哈佛结构,分时复用,但是物理存储空间分开,总线统一。)

2.程序存储器(ROM)

- 作用:存放程序、表格或常数,具有非易失性

- 特点:片内ROM与片外ROM可有2种组合方案

方案1:4KB以内的地址在片内ROM,大于4KB的地址在片外ROM中(图中折线),两者共同构成64KB空间;

方案2:片内ROM被禁用,全部64KB地址都在片外ROM中(图中直线)。

2种组合方案由EA引脚的电平状态决定:EA=1时为方案1,EA=0时为方案2

注意:ROM有6个特殊储存器单元——用于程序引导

| 存器单元 | 存器内容 |

|---|---|

| 0000H | 主程序入口地址 |

| 0003H | INT0中断程序入口地址 |

| 000BH | T0中断程序入口地址 |

| 0013H | INT1中断程序入口地址 |

| 001BH | T1中断程序入口地址 |

| 0023H | RI/TI中断程序入口地址 |

中断程序执行过程:某一突发事件 → 相应中断入口地址自动装入PC → 引导两次跳转 → 执行相应中断服务程序

主程序一般应安排在0030H地址以后(有中断需要时)

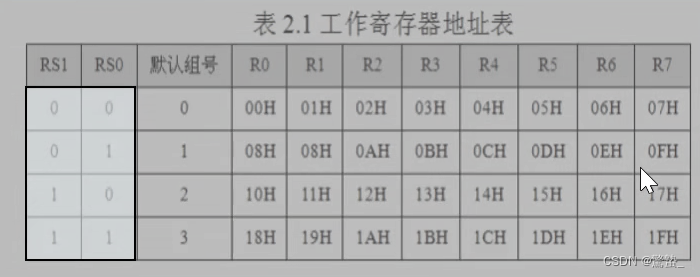

3.数据存储器(RAM)

作用:存放程序运行结果

(1) 低128字节的区域

①工作寄存器区(O0H ~1FH)

②可位寻址区(20H ~2FH)

③用户RAM区(30H ~7FH)

①区共有32个存储单元;

每个单元都有1个8位地址(字节地址)

每个单元都有1个寄存器名称(RO~R7)

32个单元分为4组(第0~第3组)

CPU只能选一组为当前工作寄存器组

当前工作寄存器组取决于PSW的设置

CPU复位后RS1和RSO默认值为0,即默认第0组为当前工作寄存器组。

②区共有16个存储单元;共有128个位地址

每个单元都有一个字节地址每个单元都有8个不同的位地址

③区共有80个存储单元;

每个单元都有一个字节地址,但没有位地址,也没有寄存器名

此区可作为堆栈区和中间数据存储区使用——用户RAM区

⚠️【注意】:①区和③区只能按字节进行数据存取操作,②区则可按字节和位两种方式存取操作。

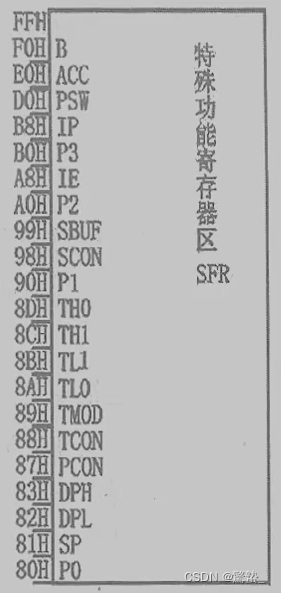

(2)高128字节RAM区

每个存储单元都有一个字节地址,但只有其中21个单元可以使用,并有相应寄存器名称。

其中,字节地址末位是0或8的SFR,都具有位地址。

三、复位、时钟与时序

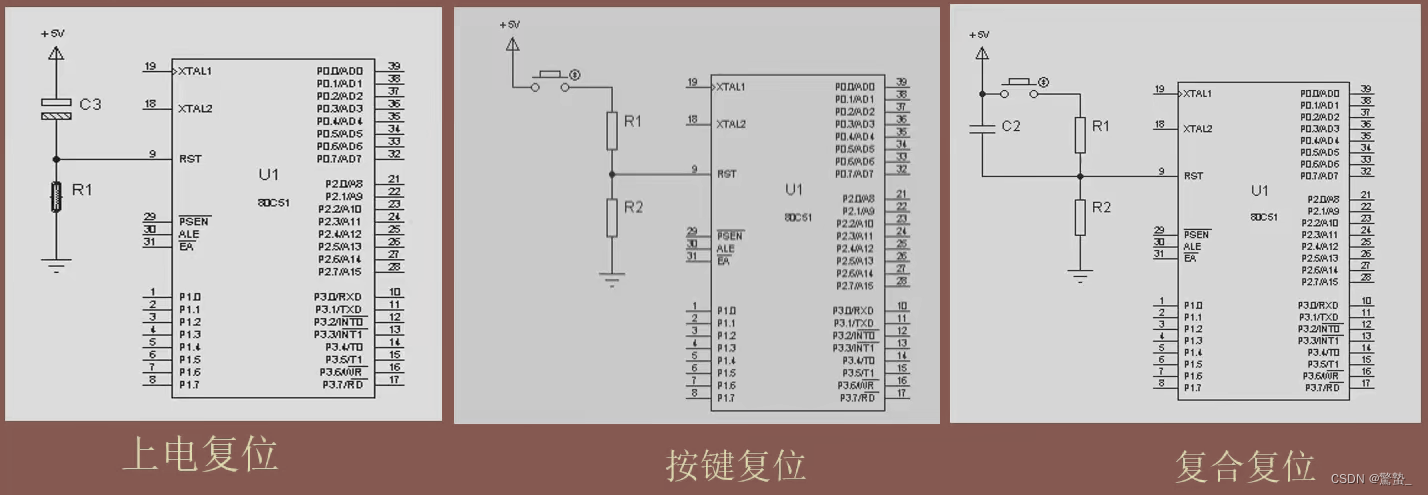

1.复位与复位电路

- 复位 —— 使单片机恢复原始默认状态的操作。

复位时片内各寄存器的初始值

| 寄存器名称 | 默认复位值 | 寄存器名称 | 默认复位值 |

|---|---|---|---|

| PC | 0000 H | TMOD | 00 H |

| A | 00 H | TCON | 00 H |

| PSW | 00 H | TH0 | 00 H |

| B | 00 H | TL0 | 00 H |

| SP | 07 H | TH1 | 00 H |

| DPTR | 0000 H | TL1 | 00 H |

| p0 ~ p3 | FF H | SCOM | 00 H |

| IP | xxx0 0000 B | SBUF | xxxx xxxx B |

| IE | 0xx0 0000 B | PCOM | 0xxx0 000 B |

表中X表示可以是任意值,B表示是二进制

在上电复位(冷启动)时的SRAM的内容为随机值,而在按键复位(热启动)时SRAM的内容保持不变。

⚠️注意:在用keil开发的程序中, keil 软件默认会在编译过程中加入把RAM初始化为00H

- 复位条件

为使电路正确复位,需要使RST信号保持至少24个时钟周期(两个机器周期)的高电平。

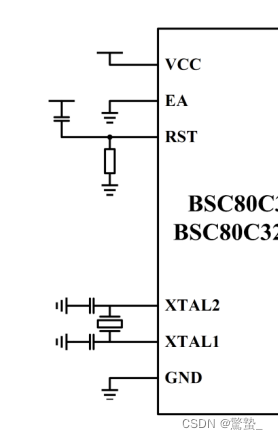

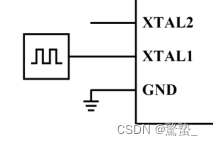

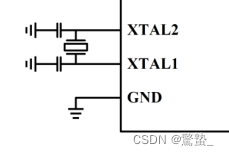

2.时钟电路

单片机需要统一的时钟控制,其时钟系统可以有两种方案。

方案一:外部时钟方式

方案二:内部时钟方式

晶振常见有:6MHz、11.0592MHz、12MHz

(其中11.0592MHz 方便对应波特率,误差小)

3.单片机时序

-

时序的概念

● 时序是对象(或引脚、事件、信息)间按照时间顺序组成的序列关系。

● 时序可以用状态方程、状态图、状态表和时序图4种方法表示,其中时序图最为常用。

● 时序图亦称为波形图或序列图,纵坐标表示不同对象的电平,横坐标表示时间(从左往右为时间正向轴),通常坐标轴可省略。 -

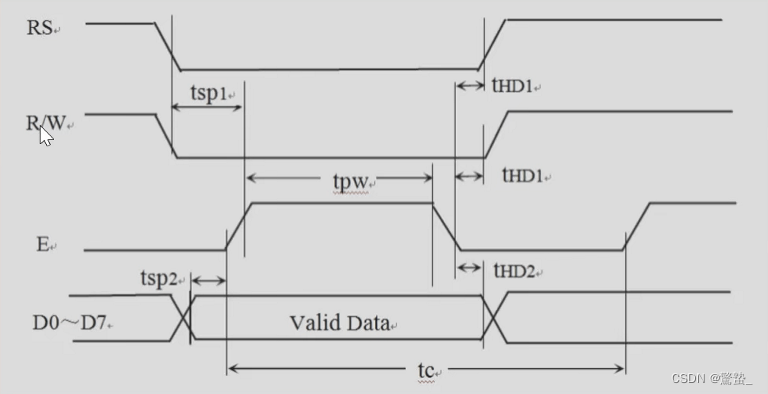

举例:

(1) 最左边是引脚的标识,表示该图反映了RS、R/W、E、D0~D7四类引脚的序列关系。

(2) 交叉线部分表示电平的变化,如高电平和低电平。

(3) 封闭菱形部分表示数据有效范围(偶尔使用文字 Valid Data)。

(4) 水平方向的尺寸线表示持续时间的长度。 -

时序关系:

● RS和R/W端首先变为低电平;

● 随后D0~D7端出现有效数据;

● R/W低电平tsp1之后,E端出现宽度为tpw的正脉冲;

● E脉冲结束并延时tHD1后,RS和R/W端恢复高电平;

● E脉冲结束并延时tHD2后,DO~D7端的本次数据结束;

随后DO~D7端出现新的数据,但下次E脉冲应在tc时间后才能出现根据这些信息便可以进行相应的软件编程了。 -

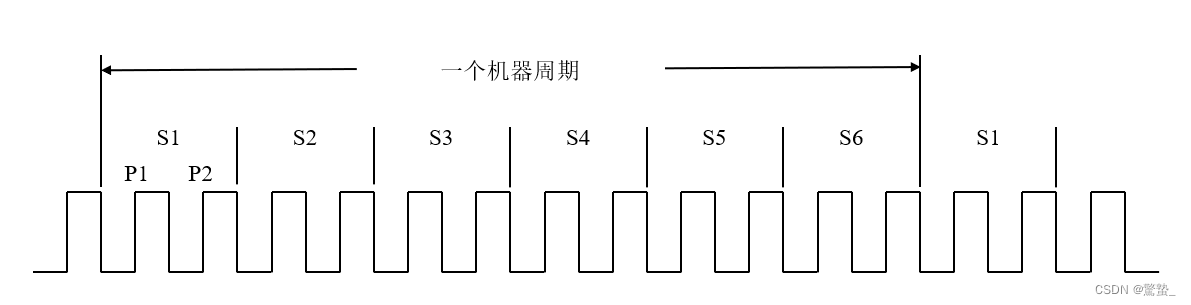

时钟的度量单位:

时钟周期(或节拍)P、状态周期S、机器周期、指令周期

● 1个状态周期(S)= 2个节拍(P)

● 1个机器周期 = 6个状态(S)= 12个节拍(P)

● 1个指令周期约为1~4个机器周期

机器周期是CPU完成一个操作的最短时间

例如:晶振为11.0592M,则时钟周期 = 1/11059200s

(12MHz→1us;6MHz→2us)

四、并行I/O接口

51单片机有32只I/O引脚,分属于4个端口(P0~P3)

- 可作为并行I/0输出通道(例如,数码管显示器连接通道)

- 可作为并行I/0输入通道(例如,按键/开关连接通道)

- 可作为串行通信通道(例如,双机通讯的连接通道)

- 可作为外部设备的连接通道(例如,存储器扩展通道)

由于工作任务不同,4个端口的内部结构也不同。

了解4类端口的内部结构对于正确使用这些I/O端口非常重要。

以下按照先易后难的原则进行学习,即P1→P3→P0→P2

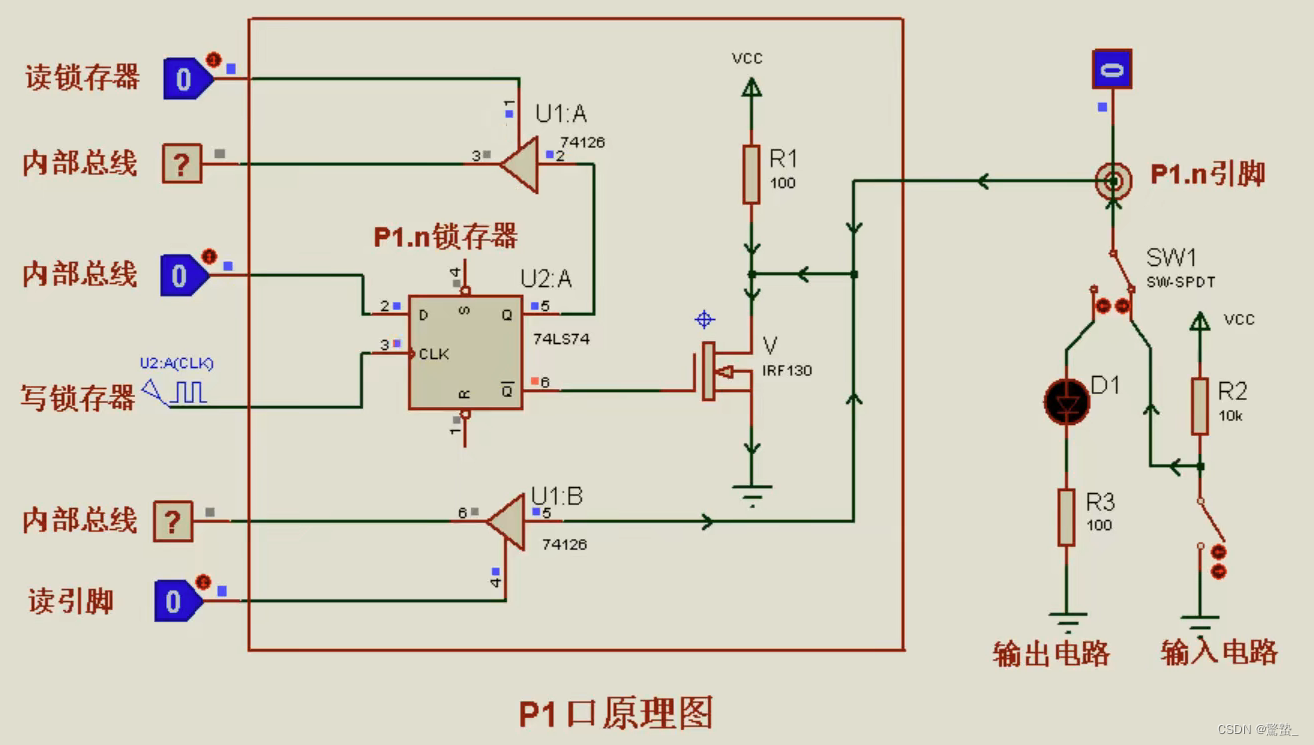

1.P1口

1个位的内部结构

(1)输出信号

复位时,锁存器自动置1,默认以高电平输出

(2) 读引脚

读引脚置1时,读入引脚值

⚠️在读入前在内部总线先写1,保证场效应管是截止的状态,使外部引脚不受影响,以免出错。

(3) 读锁存器

P1.0 = ~ P1.0; //靠读锁存器实现的

P1口的要点:

1、P1口具有通用I/O口方式,可实现输出、读引脚(输入)和读锁存器三种功能;

2、P1口为准双向通用口,作为通用输入口时应先使P1.n→1,作为通用输出口时是无条件的。

1.P3口

1个位的内部结构

P3口的第二功能:

(1)输出信号

作为通用I/O口时,第二输出功能置1。外部引脚电平由内部总线决定。

作为第二功能时,内部总线保持为1。外部引脚电平由第二输出功能端决定。

(2) 读引脚

读引脚置1时,读入引脚值

⚠️在读入前在内部总线先写1,保证场效应管是截止的状态,使外部引脚不受影响,以免出错。

(3) 读锁存器

P1.0 = ~ P1.0; //靠读锁存器实现的

P3口的要点:

1、P3口具有通用I/O口方式,可实现输出、读引脚(输入)和读锁存器三种功能;

2、P3口为准双向通用口,作为通用输入口时应先使P3.n→1,作为通用输出口时应先使第二输出端→1;

3、P3口具有第二功能方式,可实现第二输出和第二输入两种功能。

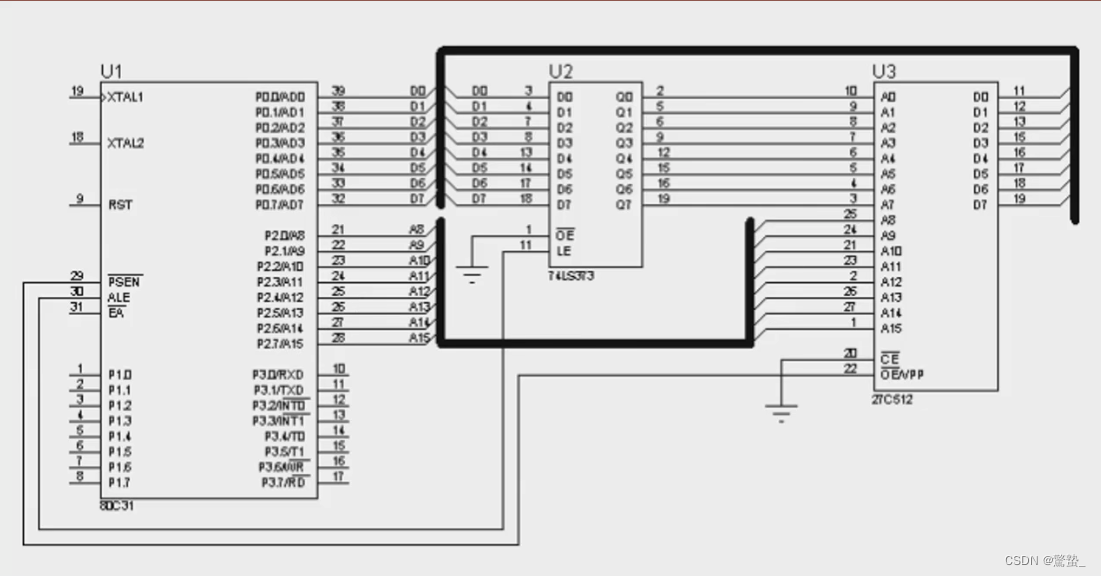

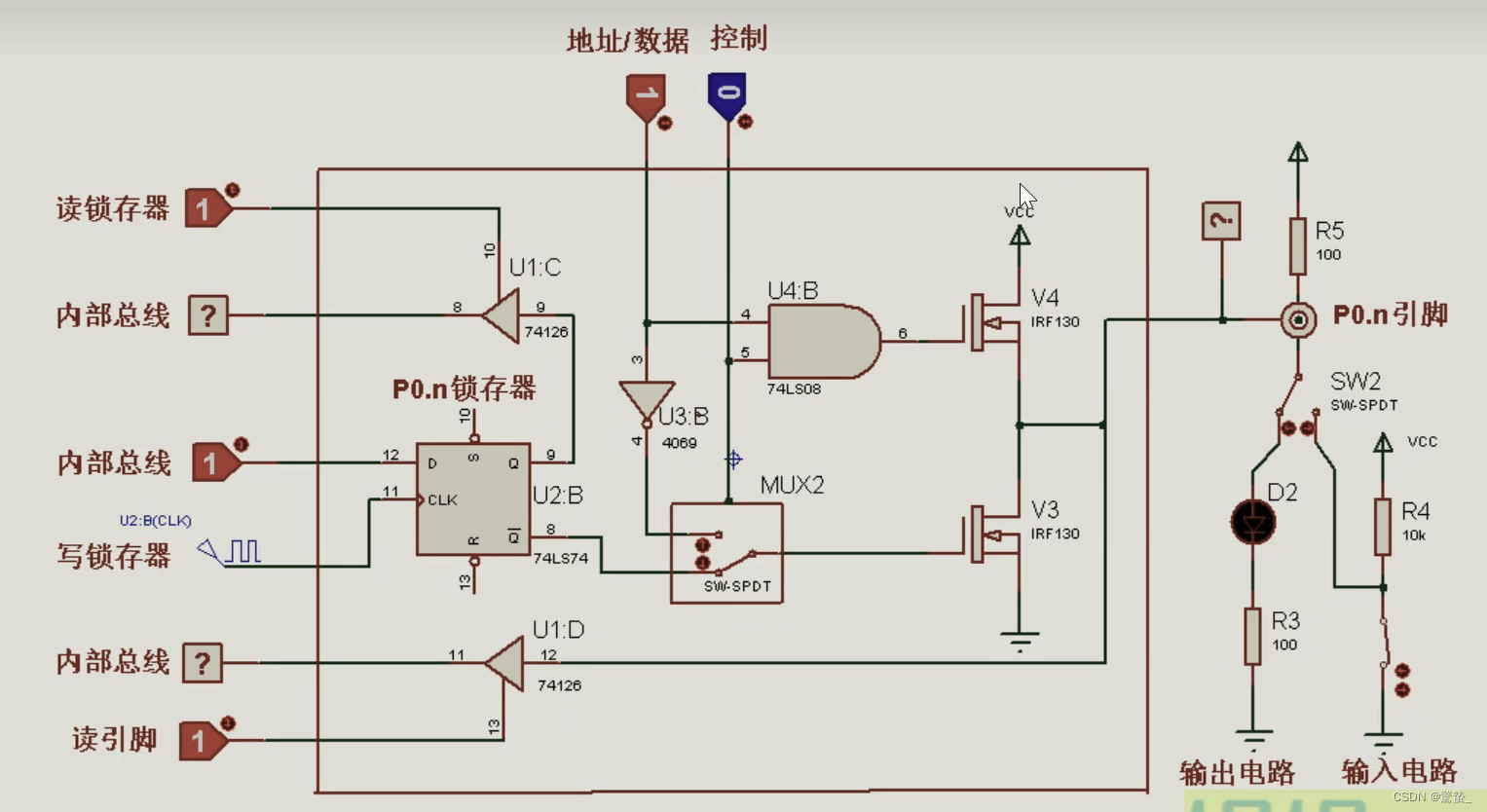

1.P0口

控制端置1时,P0口作为 地址和数据总线(低8位)

P0口的要点:

1、P0口具有通用IO口方式,可实现输出、读引脚(输入)和读锁存器三种功能;

2、P0口为准双向通用口,作为通用输入口时应先使P0.n→1,作为通用输出口时应先使第二输出端→1 ;

3、作为通用I/O口方式时,需要外接上拉电阻;

4、P0口具有地址/数据分时复用方式,可实现地址/数据输出、数据输入两种功能;

5、地址/数据分时复用方式时无需外接上拉电阻;

6、分时复用方式的数据输入时无需程序写1操作。

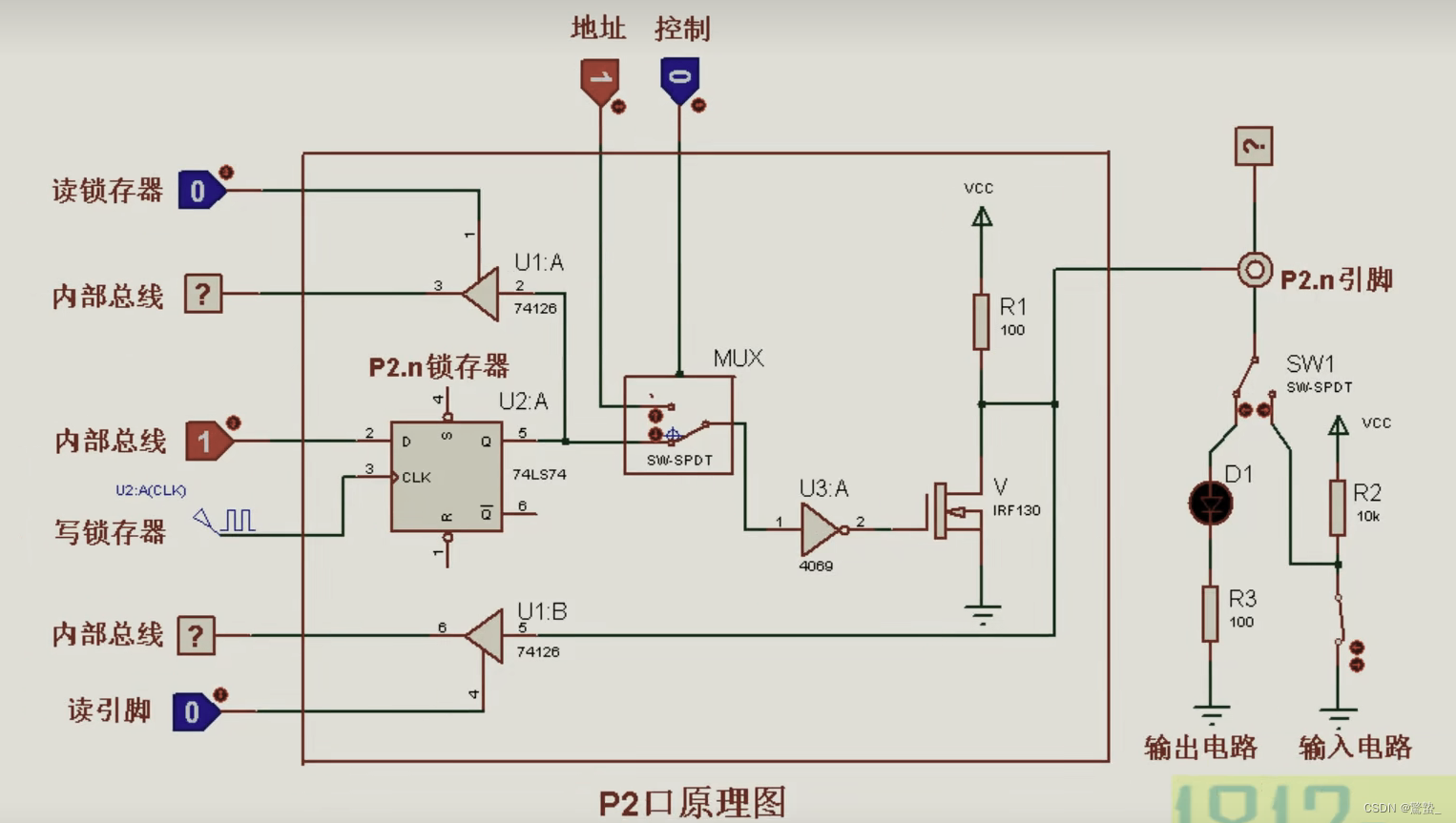

1.P2口

控制端置1时,P2口作为 地址和数据总线(高8位)

P2口的要点:

1、P2口具有通用I/O口方式,可实现输出、读引脚(输入)和读锁存器三种功能;

2、P2口为准双向通用口,作为通用输入口时应先使P2.n→1,作为通用输出口时应先使控制端→1;

3、作为通用I/O口方式时,无需外接上拉电阻;

4、P2口具有地址输出方式,可实现地址输出功能。

五、中断基本概念

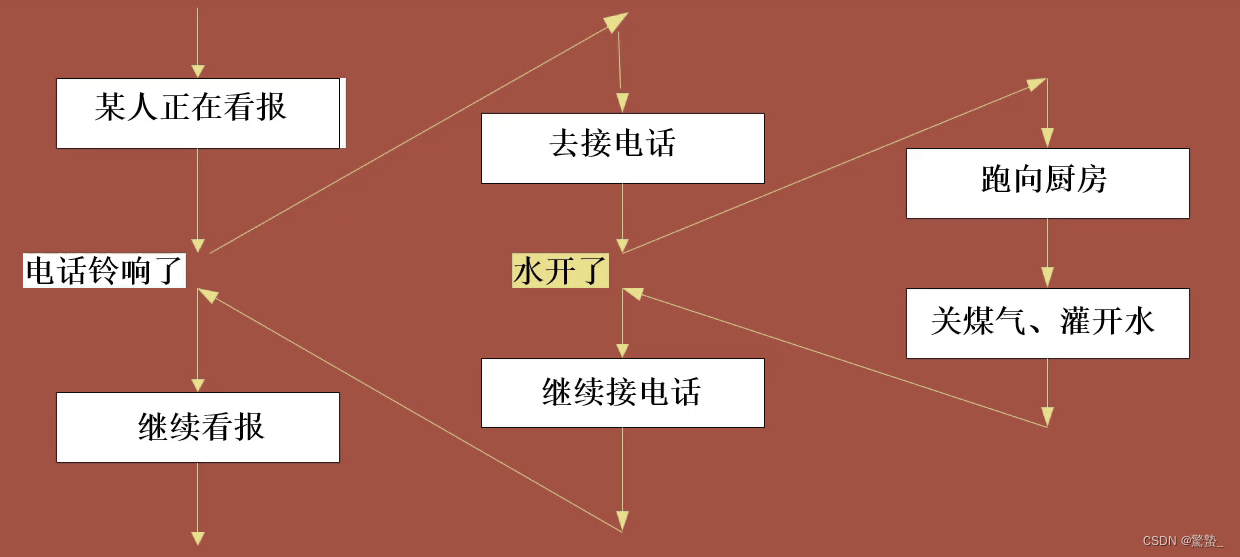

1.中断

中断系统是为使CPU具有对外界紧急事件的实时处理能力而设置的。

举例:用日常生活的中断现象

中断是指在突发事件到来时先中止当前正在进行的工作,转而去处理突发事件,待处理完成后,再返回到原先被中止的工作处,继续进行随后的工作。

51单片机的中断:

2.中断源

中断源数量和种类越多,MCU处理突发事件的能力就越强。

80C51单片机共有5种中断源。

外部中断(2个) —— 中断源信号由外部引脚P3.2和P3.3输入(低电平触发、下降沿触发【程序设定】)

定时器中断(2个)—— 定时的时候是对内部机器周期进行计数,不需要外部引脚;计数(频率测量)的时候,需要外部引脚P3.4和P3.5【可扩展】

串口中断(1个)—— 引脚P3.0和P3.1

- 中断事件出现后,系统将调用与该中断源相对应的中断函数进行中断处理

- 汇编语言中规定了5个特殊的ROM单元用于引导中断程序的调用,这些单元的地址称为中断向量。

- 汇编编程时,需要在此单元处放置一条指向中断程序入口地址的跳转语句,以便引导中断程序的执行。

- 对于C51语言,调用中断函数时不用中断向量,而要用到与中断源相应的中断号。

- 80C51的中断源、中断向量及中断号的对应关系如下表所示。

| 51单片机的中断源 | 中断源名称 | 中断向量 | 中断号 |

|---|---|---|---|

| P3.2 引脚的电平/脉冲状态 | INT0‾\overline{\text{INT0}}INT0 | 0003H | 0 |

| 定时/计数器0的溢出标志位状态 | T0 | 000BH | 1 |

| P3.3 引脚的电平/脉冲状态 | INT1‾\overline{\text{INT1}}INT1 | 0013H | 2 |

| 定时/计数器1的溢出标志位状态 | T1 | 001BH | 3 |

| 串口数据缓冲器的工作状态 | TX/RX | 0023H | 4 |

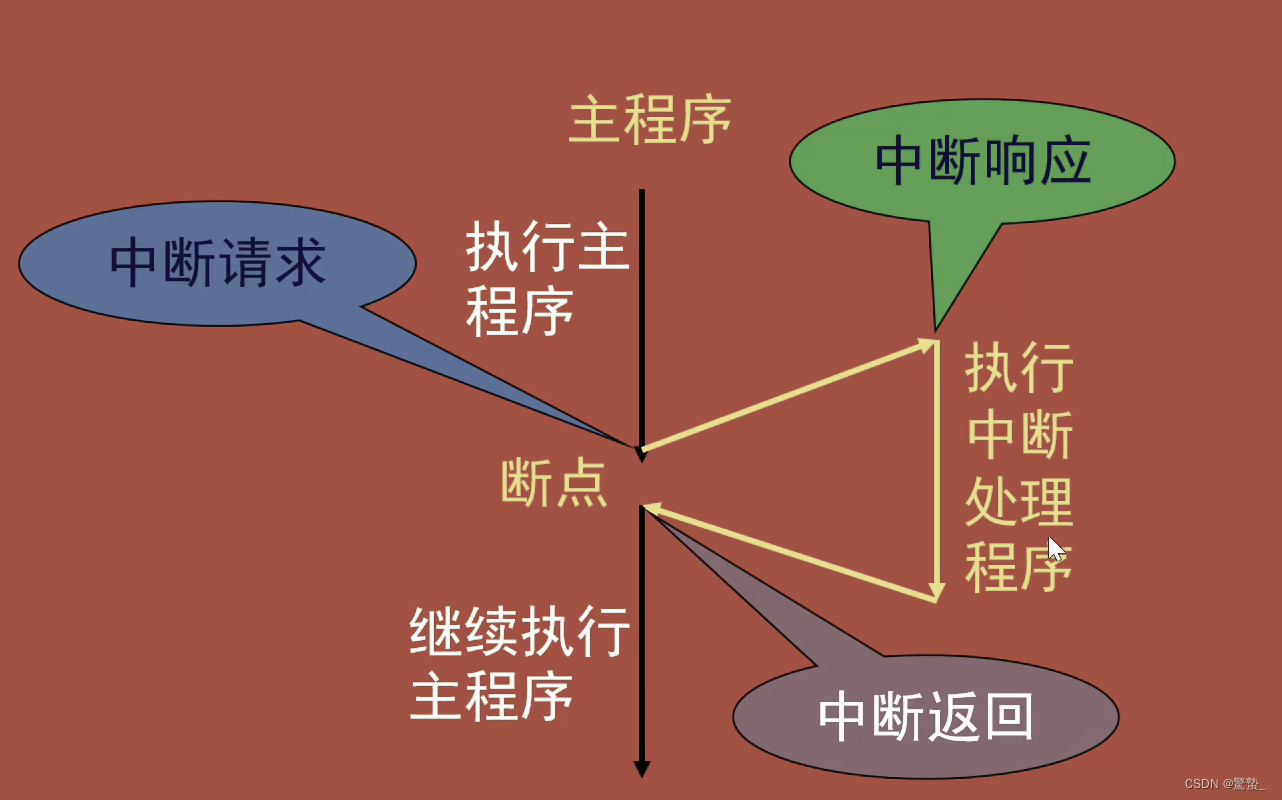

3.中断的几个概念

- 中断源:中断管理系统能够处理的突发事件;

- 中断请求:中断源向CPU提出的处理请求;

- 中断响应过程:由中断管理系统处理突发事件的过程;

- 中断函数:针对中断源和中断请求提供的服务函数;

- 中断嵌套:在中断服务过程中执行更高级别的中断服务。

4.中断实现的功能

- 分时操作

CPU可以使多个外设同时工作,并分时为各外设提供服务,从而大大提高了CPU的利用率和输入/输出的速度。 - 实时处理

当计算机用于实时控制时,请求CPU提供服务是随机发生的。有了中断系统,CPU就可以立即响应并加以处理。 - 故障处理

当计算机运行中出现如电源断电、存储器校验出错、运算溢出等错误时,CPU可及时转去执行故障处理程序,减小或消除故障产生的影响。

六、80C51中断的系统结构

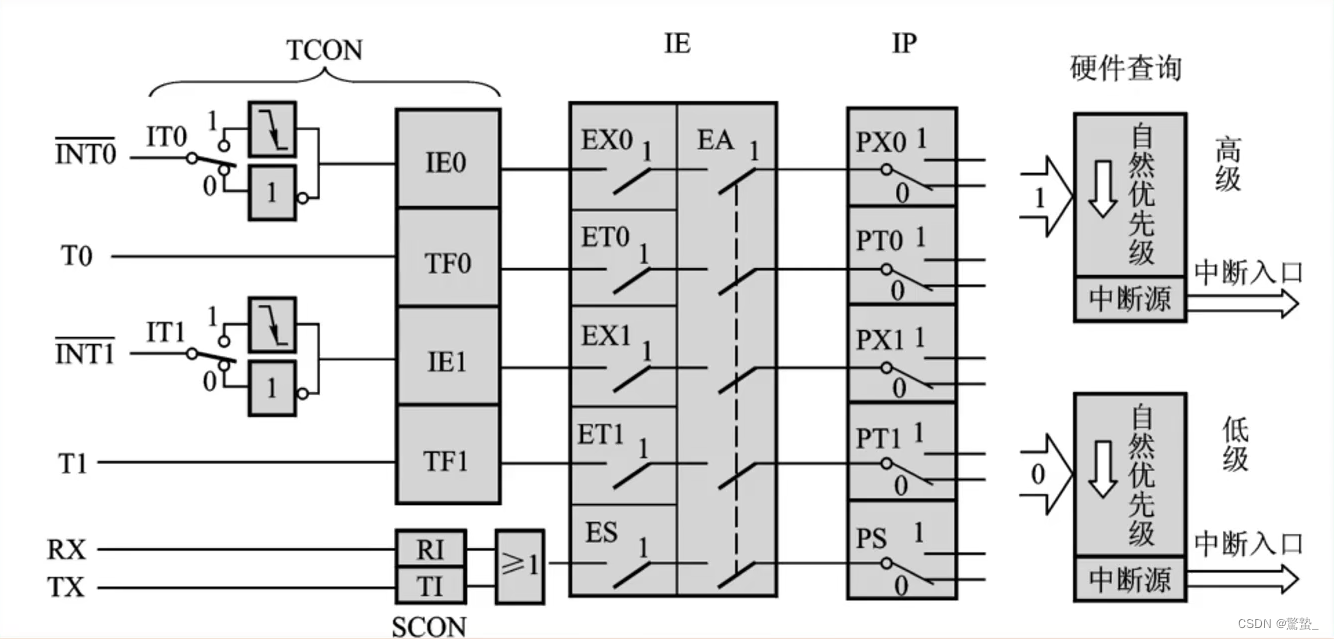

1.中断系统的结构

80C51系列单片机的中断系统有5个中断源,两个优先级,可实现二级中断服务嵌套。

中断信号分别沿5条水平路径由左向右进行传送。其中,TCON、SCON、IE、IP是相关SFR。

IT0、IT1 选1 是下降沿触发,选0是低电平触发【程序】。触发后IE0随之置1【硬件】。

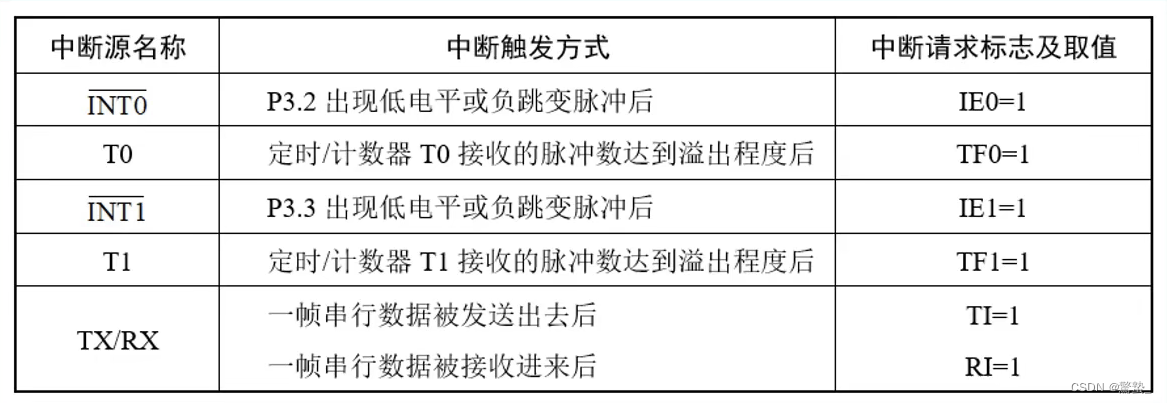

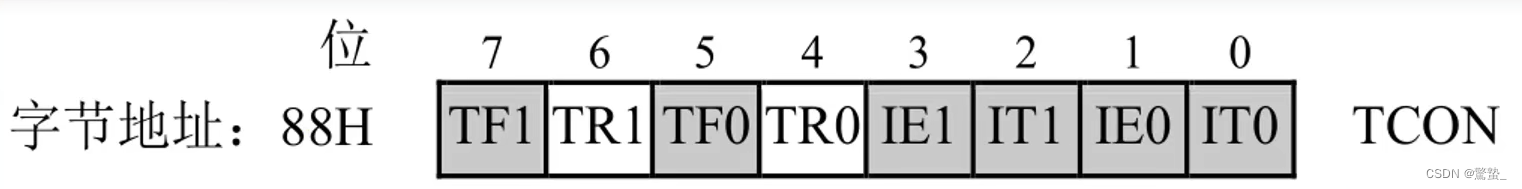

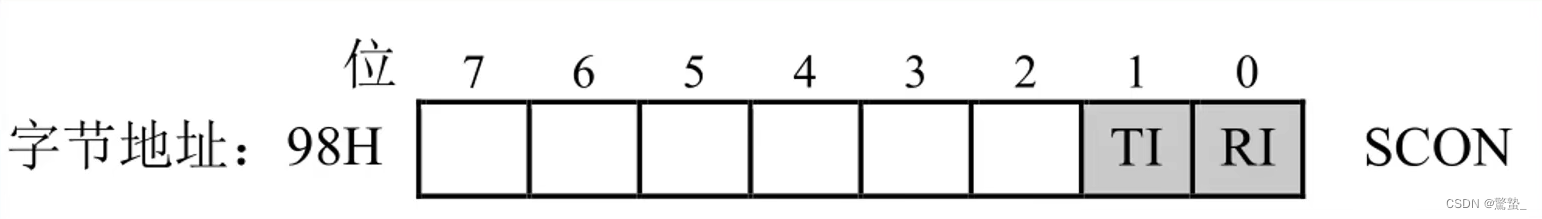

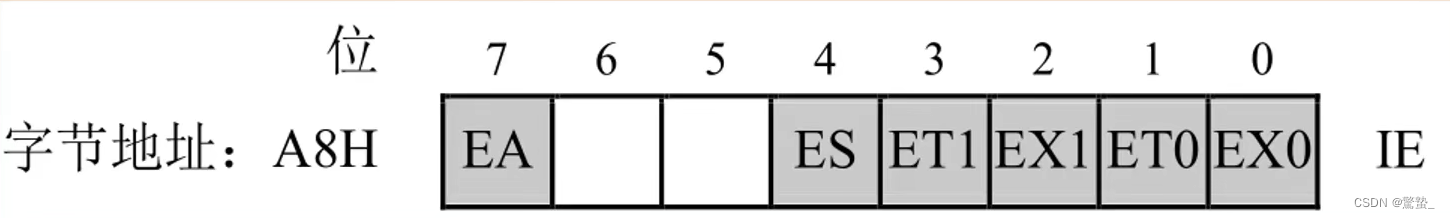

2.中断请求标志

TCON的中断标志

SCON的中断标志

中断的控制

- EX0(IE.0):外部INT0中断允许位。

- ET0(IE.1):定时/计数器T0中断允许位

- EX1(IE.2):外部INT1中断允许位。

- ET1(IE.3):定时/计数器T1中断允许位

- ES (IE.4):串行口中断允许位

- EA (IE.7):CPU 中断允许(总允许)位

中断优先级的控制

- PX0 (IP.0):外部中断INT0中断优先级设定位。

- PT0 (IP.1):定时/计数器 T0中断优先级设定位。

- PX1 (IP.2):外部中断INT1中断优先级设定位。

- PT1 (IP.3):定时/计数器T1中断优先级设定位。

- PS (IP.4):串行口中断优先级设定位。

3.中断的优先级(默认)

各中断源响应优先级 及 中断服务程序入口表

中断优先级处理有三条原则:

1、CPU同时接收到几个中断时,首先响应优先级别最高的中断请求。

2、正在进行的中断过程不能被新的同级或低优先级的中断请求所中断。

3、正在进行的低优先级中断服务,能被高优先级中断请求所中断。

⚠️注意:单片机复位时,IP初值为0 —— 默认所有中断源均为低级中断。

举例:

- 80C51单片机的INT0、INT1引脚分别输入 压力超限 及 温度超限 中断请求信号,定时器/计数器0作为 定时检测 的实时时钟,用户规定的中断优先权排队次序为 :

- 压力超限 → 温度超限 → 定时检测

- 要求确定IE、IP的内容,以实现上述要求

答案:

IE:1xx0 0111 (87H)

IP:xxx0 0101 (05H)

七、定时/计数器的结构及原理

定时/计数器是单片机系统一个重要的部件,其工作方式灵活、编程简单、使用方便,可用来实现定时控制、延时、频率测量、脉宽测量、信号发生、信号检测等。此外,定时/计数器还可作为串行通信中波特率信号发生器。

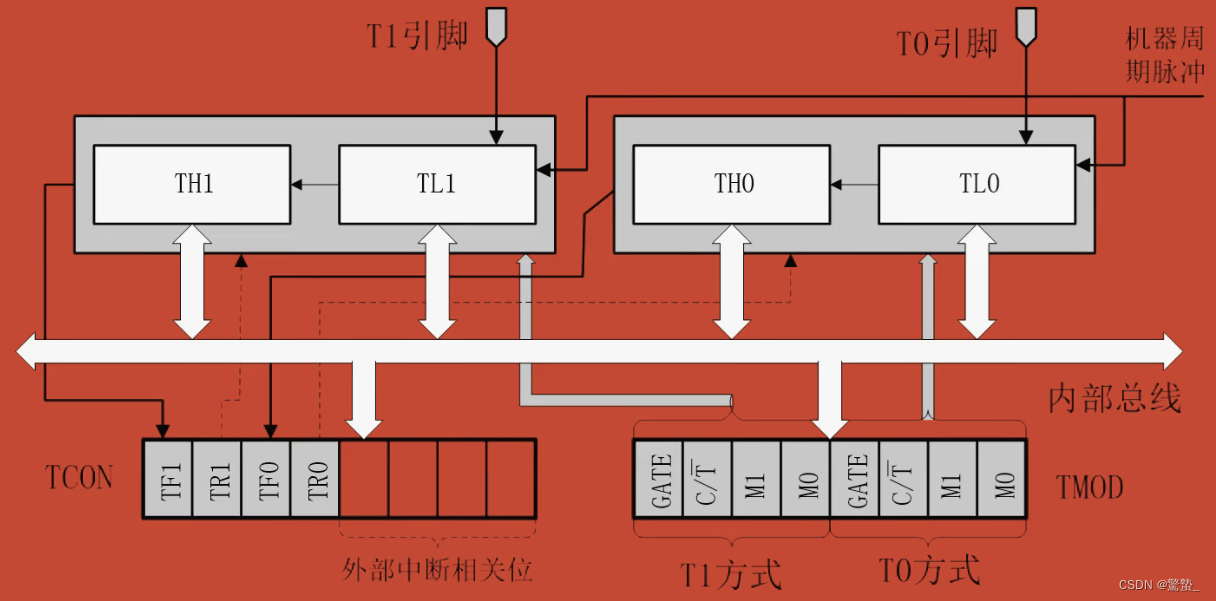

2.结构

C/T*位 置0 为定时功能;置1 为 计数功能;

- 定时器:对片内机器时钟(周期方波)进行计数

- 计数器:对Tx引脚输入的脉冲进行计数

2.工作原理

-

80C51内部两个16位的定时/计数器 T0 T1

注:单片机型号不同,内部定时器个数也不同 -

T0由两个8位的 SFR TH0 和 TL0 构成 T1由两个8位的 SFR TH1 和 TL1 构成

-

具有定时或事件计数的功能,可用于:1)内部定时控制 2)外部事件计数和检测等

-

定时/计数器的实质是:加一计数器

-

每个定时/计数器都可以由软件设置为

定时工作方式(C/T*)= 0

计数工作方式(C/T*)= 1 -

T0和T1受特殊功能寄存器TMOD和TCON控制

-

定时/计数器一旦启动(TRx=1),便可和CPU并行工作,对提高CPU工作效率和简化外围电路大有益处

3.工作方式之定时

- 定时方式时,定时器计数脉冲由51单片机的片内振荡器经12分频后产生的。

- 每经过一个机器周期,定时器(T0或T1)的数值加1,直至计数满产生溢出。

4.工作方式之计数

- 计数方式时,通过引脚P3.4 (T0)或 P3.5 (T1)对外部脉冲信号进行计数。

- 当输入脉冲信号产生由1至0的下降沿时,定时器的值加1,在每个机器周期,CPU采样引脚P3.4 (T0)和P3.5 (T1)的输入电平。若前一个机器周期采样值为高,下一个机器周期采样值为低,则计数器加1。

- 由于检测一个1至0的跳变需要2个机器周期,故最高计数频率为振荡频率的二十四分一。

- 虽然对输入信号的占空比无特殊要求,但为了确保某个电平在变化之前至少被采样-次,要求电平保持时间至少是一个完整的机器周期。

4.与定时/计数器相关的SFR

| SFR | 含义 |

|---|---|

| TH (Timer High) | 定时器/计数器0高字节(8Ch) |

| TL0 (Timer Low) | 定时器/计数器0低字节(8Ah) |

| TH1 | 定时器/计数器1高字节(8Dh) |

| TL1 | 定时器/计数器1低字节(8Bh) |

七、定时/计数器的工作方式

https://space.bilibili.com/483942191/channel/collectiondetail?sid=51090

标签:引脚,中断,51,计数器,单片机,地址,原理,定时 From: https://www.cnblogs.com/feng9exe/p/17613717.html