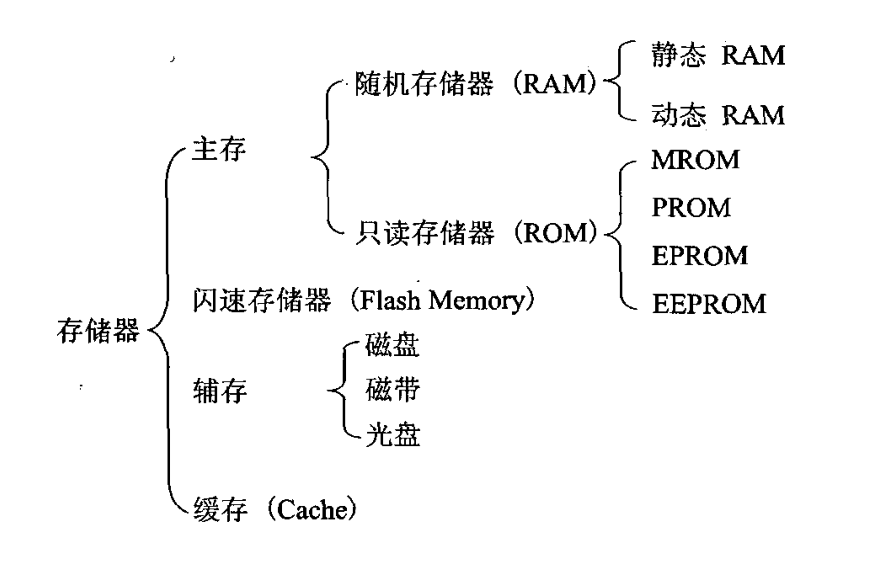

存储器概述

分类

存储器的分类如下:

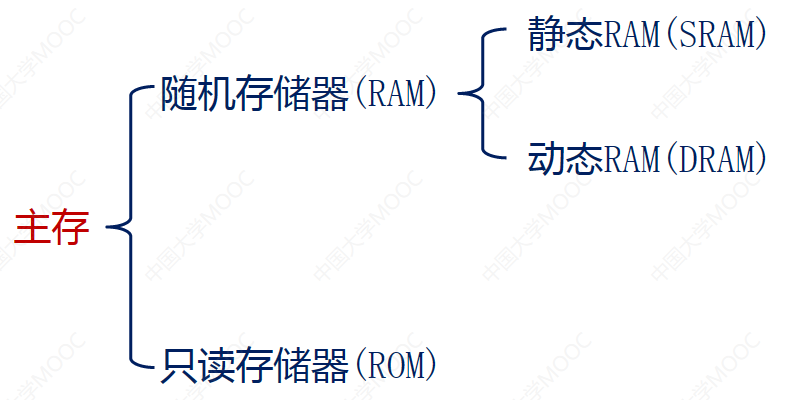

主存的分类:

主存分为随机存储器(RAM)和静态存储器(RAM),随机存储器又分为静态RAM和动态RAM

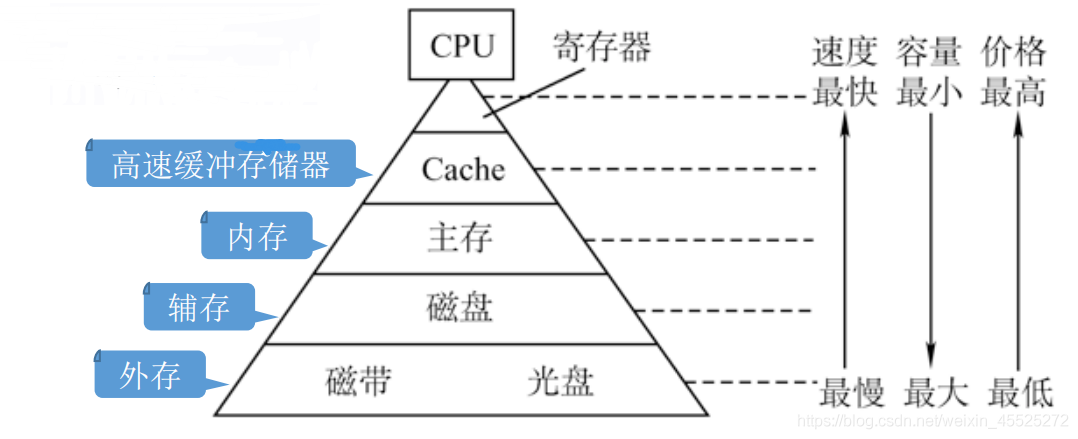

存储器的层次结构

金字塔结构

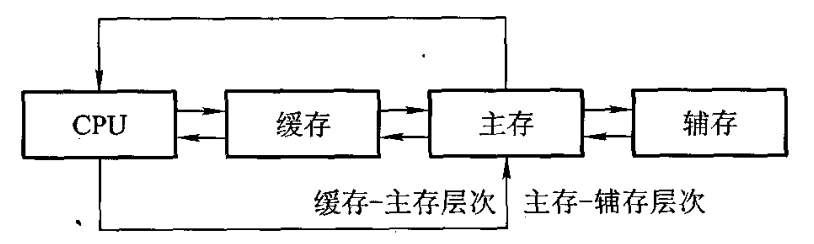

主存-辅存及主存-缓存结构

主存-辅存结构主要解决的问题是主存容量的问题,因为主存的容量小。

主存-缓存结构主要解决的是cpu速度与主存访问速度不同的问题,cpu处理速度快,而从主存中读写数据慢,我们添加一个高速缓存事先存在缓存中,这样可以提高速度

存储器的技术指标

存储容量:在一个存储器中可以容纳存储单元的个数 单位字或字节数

存取时间:从接收到读写指令开始到完成一次存取操作的时间 ns

存取周期:连续两次访问存储器的最小时间间隔 ns

存储器带宽:单位时间里存储器所取信息量 位/s, 字节/秒

存取周期略大于存取时间

静态存储器SRAM

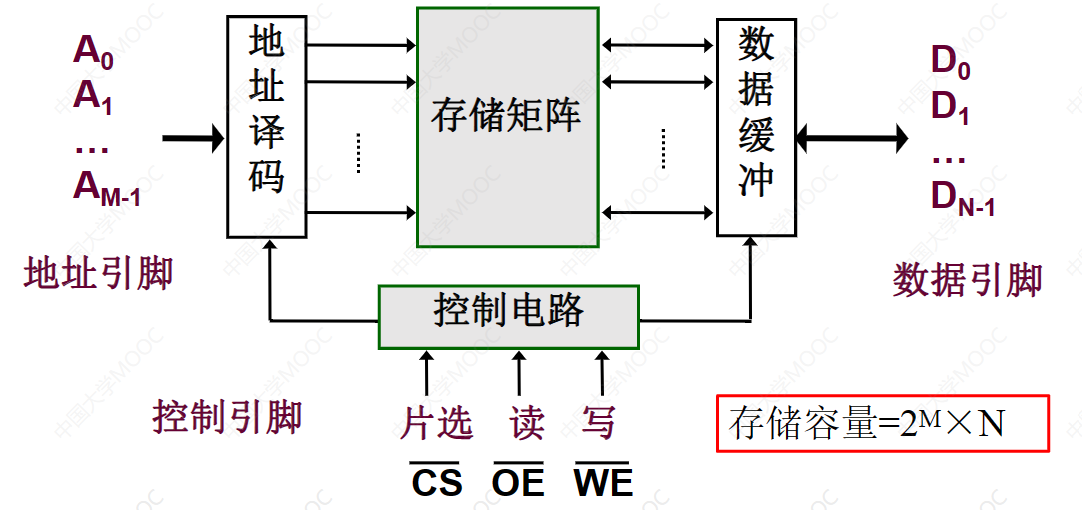

1、地址译码器:控制选择存储矩阵中的哪一个存储单元。地址线有M根,就有2^M个存储单元

2、存储矩阵:内包含若干存储单元

3、控制电路:控制电路是否工作、以及工作状态下是进行读操作还是进行写操作

4、存储容量=存储单元个数*存储字长(可能有人要问存储字长是什么?和机器字长的关系是什么呢?)

先说一下字长的概念:

(1)、存储字长:一个存储单元中二进制代码的位数

(2)、机器字长:cpu进行一次整数运算所能处理的二进制位数(和ALU的输入端位数直接相关,而ALU的数据来源又是寄存器和内部数据总线)

通常机器字长是存储字长的整数倍

(3)、指令字长:一条指令的总长度(可能会发生改变)

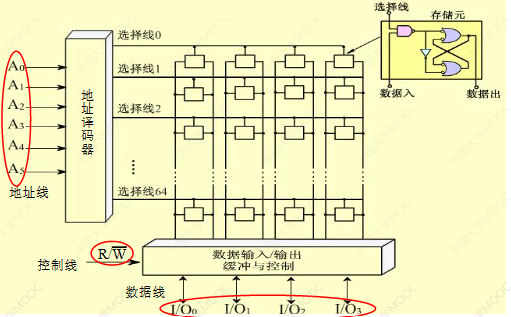

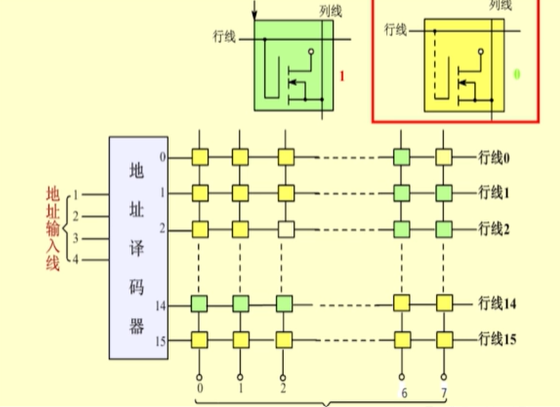

下面是基本的静态存储元阵列:

1个存储元用来存储一个二进制位的信息,对应为下图中的一个小方块

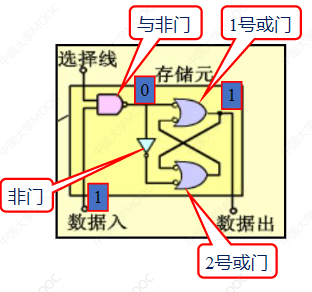

SRAM的记忆原理

SRAM是用一个锁存器(触发器)来作为存储单元的

我们可以看下图给选择线一个低电平使其工作,假设这时我们想要写入数据,我们给数据入一个低电平,这时通过第一个与非门的信号为低电平,通过1号或门的信号为高电平而通过二号或门的电信号为高电平,也会使通过1号或门的电信号为高电平,阻止数据出这样相互耦合的电路使信息保存稳定,只要不断电就能无限期保存

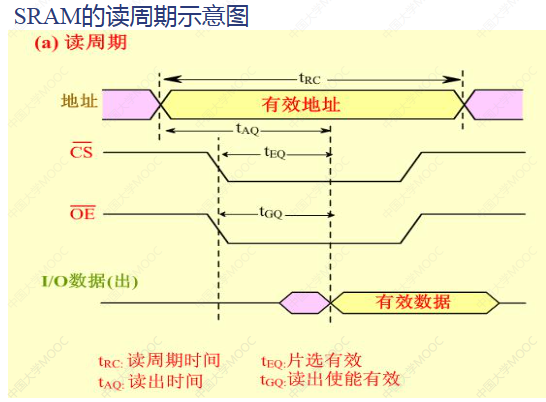

两种译码方式的RAM

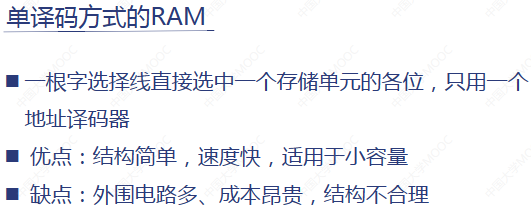

单译码方式的RAM

1、特点:只用一个译码器选中存储单元中的各位

2、优点:结构简单,存取速度快,适用于小容量

3、缺点:外围电路多、成本昂贵

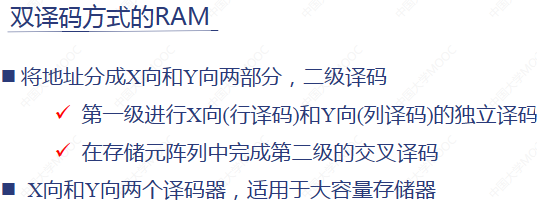

双译码方式的RAM

目前的SRAM多采用双译码方式,为了组织更大的存储量。

所谓双译码,就是采用而二级译码将地址分为两部分(我们用x向和y向表示),我们先对x、y分别译码,然后再在存储阵列中进行二次译码。

其实就是第一次译码确实x,y然后根据坐标再确定具体的位置

两种译码方式的比较

这里我们通过一个具体的例子来看

SRANM的读写周期

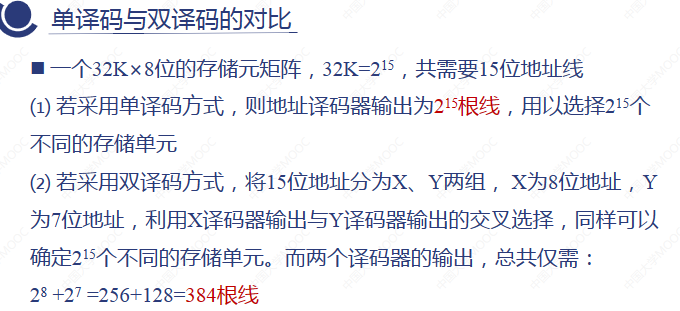

读周期

1、地址线先有效

2、待地址线选中存储单元后片选线和读出信号开始工作

3、等到片选线和读出信号都恢复高电平后地址线才恢复

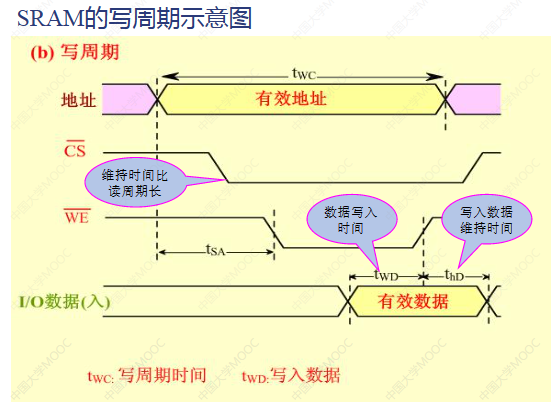

写周期

1、地址线先有效

2、然后片选线有效,

3、写命令有效

4、撤销写命令

5、片选线维持的时间也比读周期长

动态存储器DRAM

DRAM存储器的存储元有一个MOS晶体管和电容器组成,MOS晶体管的作用是作为开关,存储信息是通过电容器上的电荷量体现的

DRAM的读写过程

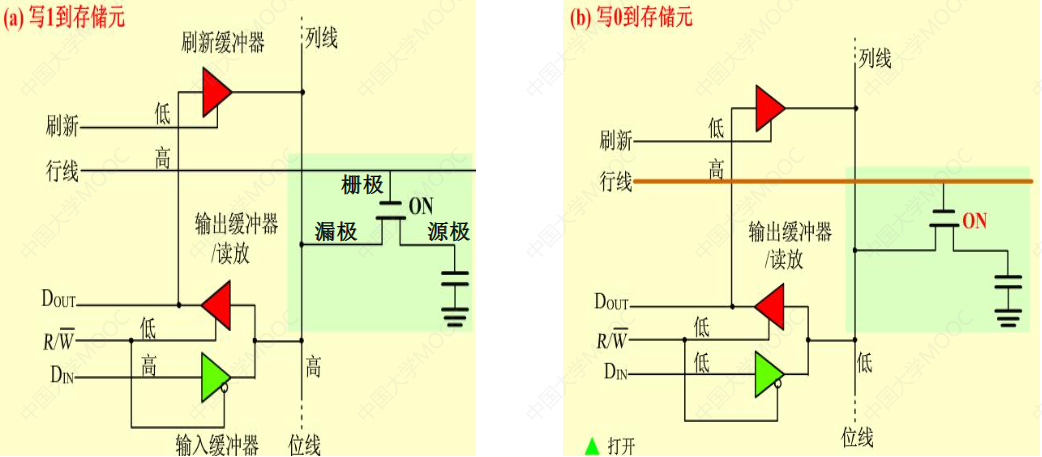

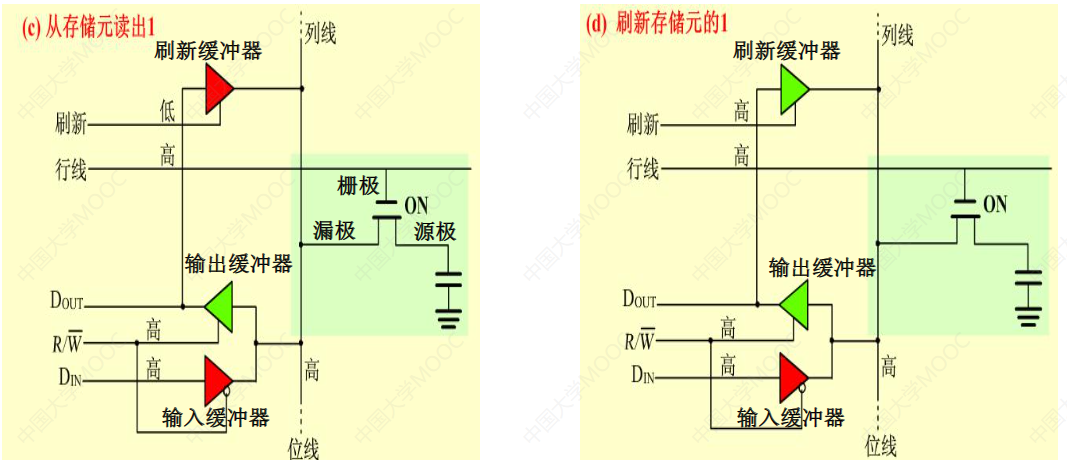

写0和写1

写1:输出缓冲器、刷新缓冲器关闭、输入缓冲器打开,输入数据Din = 1送到存储元位线上,行线为高,MOS管被打开,这样电容就充电,表示存储了1

写0:输出缓冲器、刷新缓冲器关闭、输入缓冲器打开,输入数据Din = 0送到存储元位线上,行线为低,MOS管被打开,这样电容就放电,表示存储了0

读出过程

读1:输入缓冲器、刷新缓冲器关闭、输出缓冲器打开,行线为高,MOS管打开,电容上存储的1被送进Dout

刷新:输入缓冲器关闭、刷新缓冲器打开、输出缓冲器打开,行线为高,MOS管打开,读出数据Dout经过刷新缓冲器被送到位线上,经MOS管写入电容上。

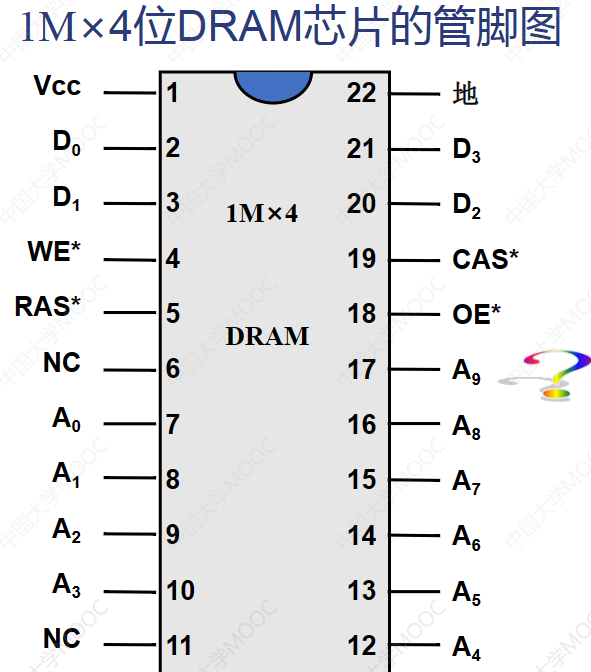

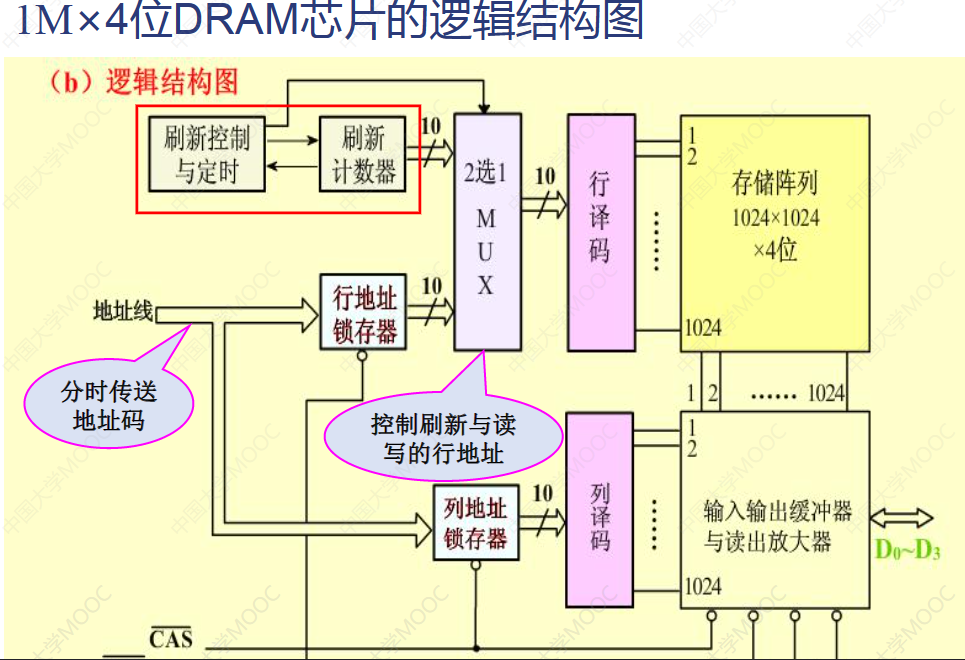

DRAM的逻辑结构

1、两个电源线Vcc、两个地线,还有一个空脚线NC

2、地址线只有10根而我们是1M的存储器,这里是不是很奇怪?因为这里我们用的是分时传送见下

1、与SRAM不同我们增加了行地址锁存器和列地址锁存器,因为我们DRAM存储器的容量很大,地址线的宽度要相应增加,这会导致芯片引脚数增加,所以为了避免引脚数太多,这里我们选择的是分时传送,地址线的总宽度是10位,先送A0A9,由RAS打入行锁存器,再送A10A19,有CAS打入列锁存器

2、与SRAM不同我们增加了刷新计数器和控制电路。DRAM读出之后必须要刷新,未读写的存储元也要定期刷新,并且要按行刷新,刷新操作是与读写操作交替进行的,所以这里用了二选一数据选择器来提供刷新和读写操作

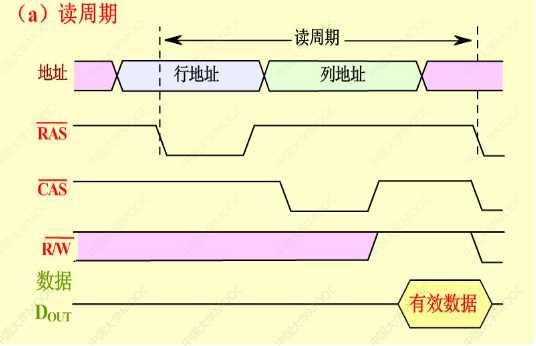

DRAM的读写周期

DRAM的刷新

1、刷新操作和读操作类似只是不向外输出

2、按行定期刷新

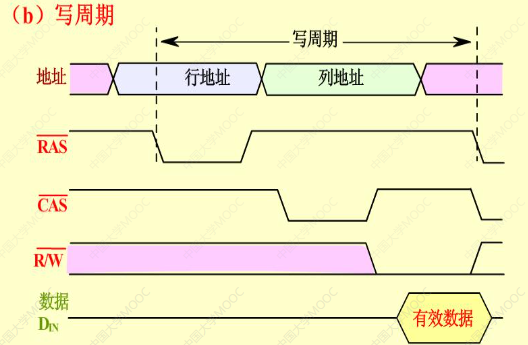

3、刷新方式有两种,集中式和分布式

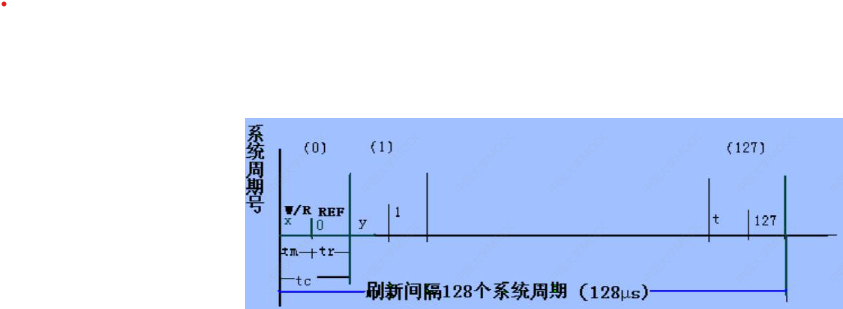

集中式刷新

DRAM所有行在每一个刷新周期中都被集中刷新,对正常的读写周期不会产生影响

但是死时间时间过长

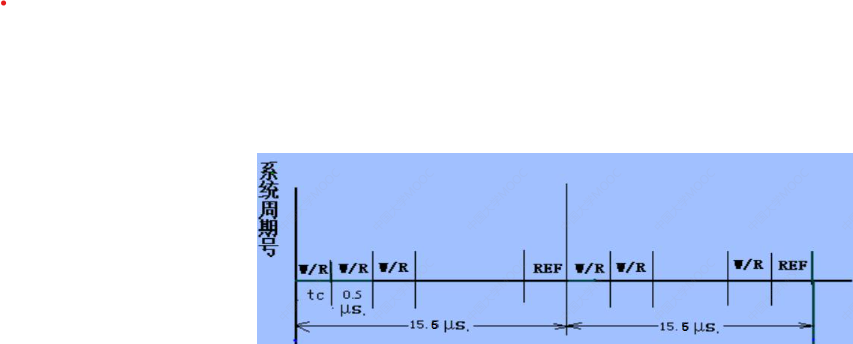

分散式刷新

1

将每一行的刷新分散到每个存取周期中

增长了存取周期

刷新过于频繁

2

两毫米内分散地把128行刷新一次,没有死时间

DRAM和SRAM的比较

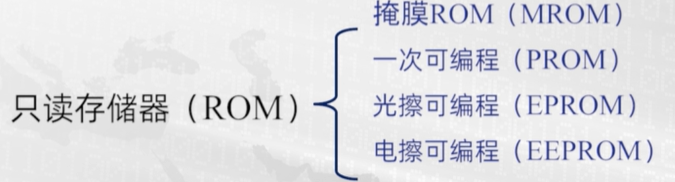

ROM

ROM分类

ROM分为掩膜ROM、一次可编程ROM、光擦可编程ROM、电擦可编程ROM

MROM

1、存储内容固定的ROM、由掩膜工艺一次性制成

2、一旦制成无法改变

3、下图中绿色表示存储1,黄色代表存储0,在出厂时就已经确定

PROM

PROM只能进行一次性的写入,出场时全为1或0,可根据自己的需要修改,但修改是不可逆的

EPROM

1、可进行多次编程

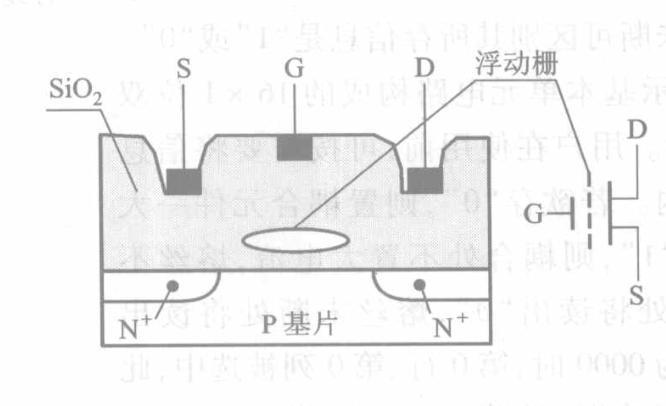

2、悬空的没有引出线称为浮空栅,G为控制栅

3、存储信息是根据浮空栅上有没有电子来确定的,浮空栅上有电子,存储信息为0,浮空栅上没有电子存储信息为1

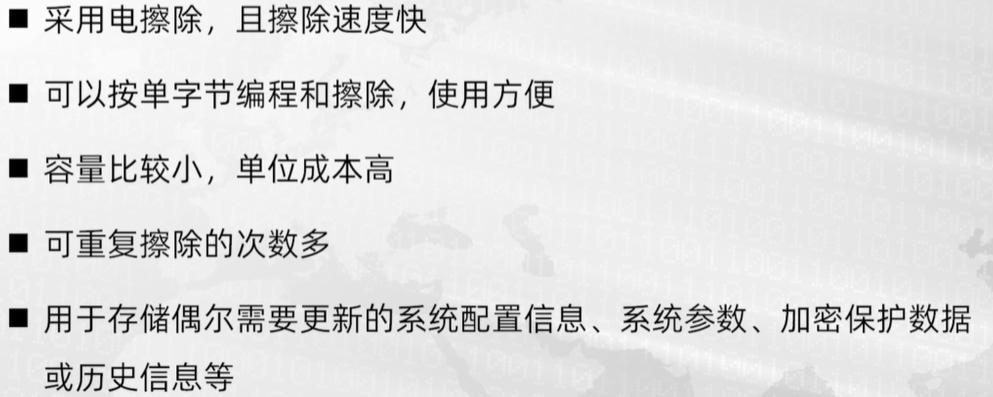

EEPROM

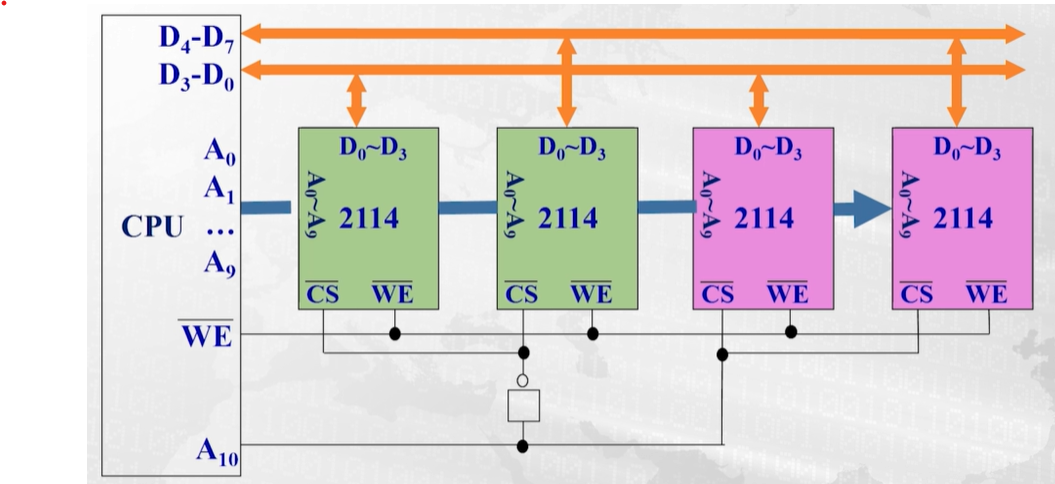

存储器容量扩展

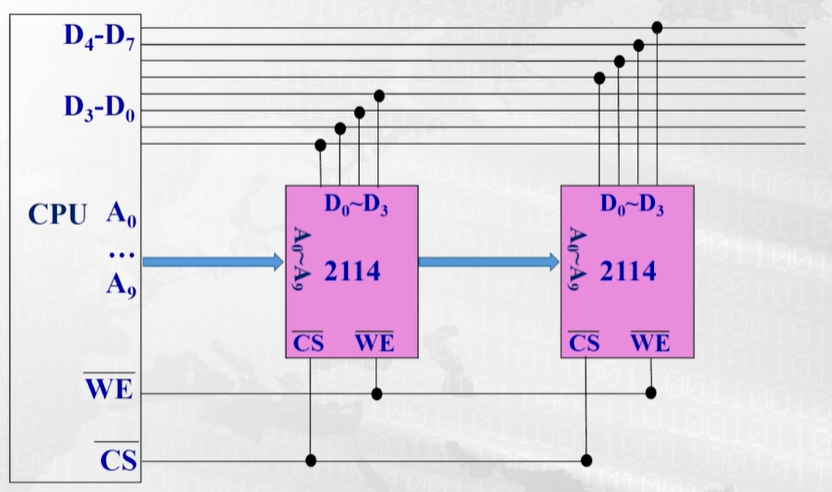

位扩展

只加长存储单元的字长,不增加存储单元的数量

数据线单独链接,地址线还有片选线、读写控制线连接在一起

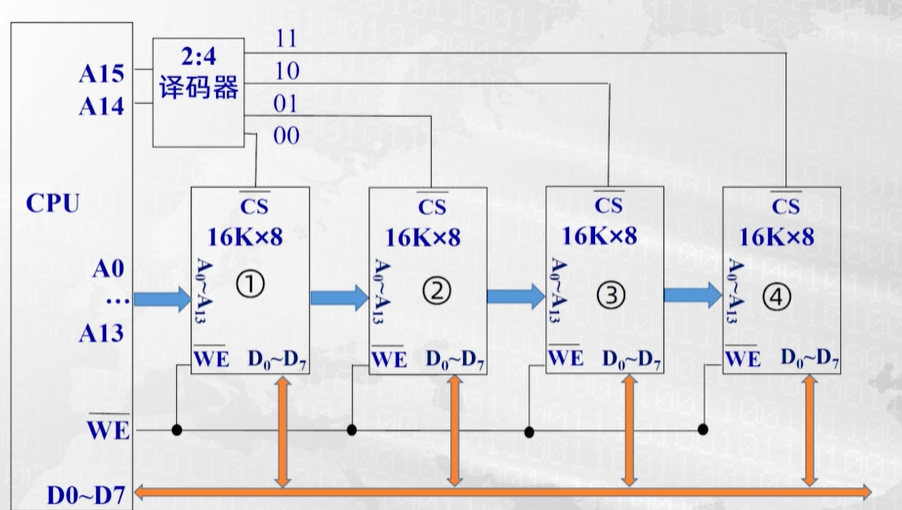

字扩展

仅在字数方向扩展,位数不变

eg4片16K8位芯片扩展成64K8位芯片

字位同时扩展