纲要

- OD门

- 传输门

- 三态门

1.OD门

i. 概念

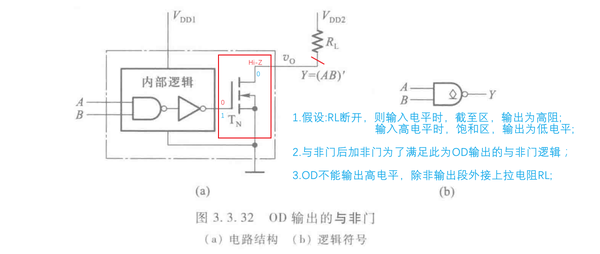

在CMOS电路中为了满足输出电平变换,吸收大负载电流以及实现线与连接等需要,需要将输出级电路结构改为漏极开路输出的MOS管,构成漏极开路输出(Open-Drain Output)门电路,简称OD门。

ii.电路原理

iii.应用

a.输出电平变换

如上图所示,可实现VDD1->VDD2的电平转换;

b.吸收大负载电流

略;

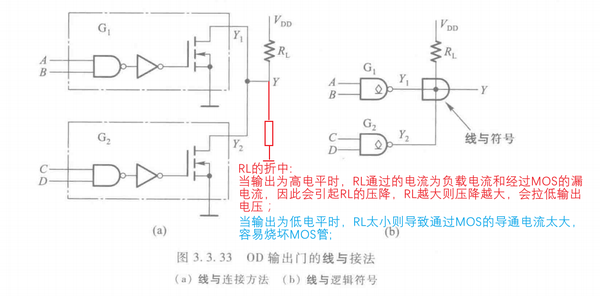

c.实现线与连接

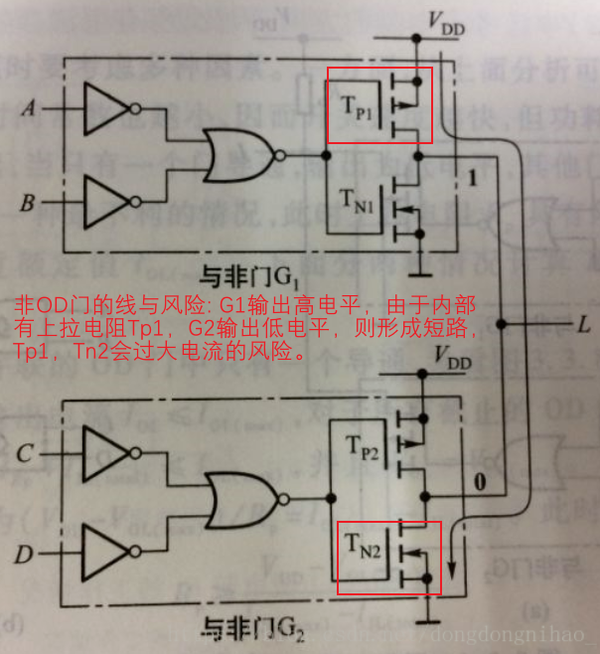

非OD门线与风险:

OD门线与:

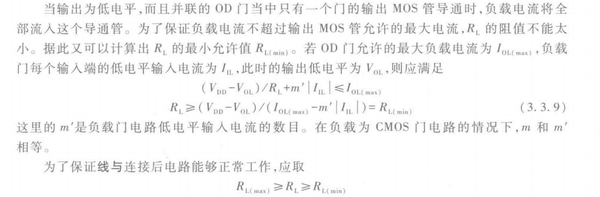

iv.外接电阻计算(了解)

最大值:

最小值:

2.传输门

i.概念

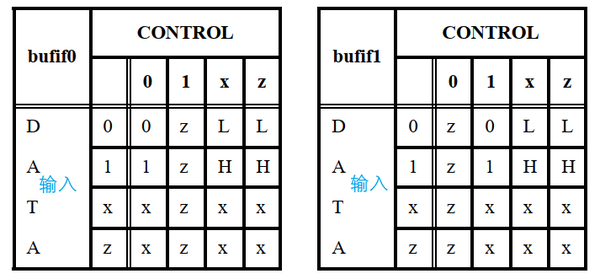

可当作模拟开关,用来传输连续的模拟电压信号;在Verilog门级描述中,类似于:bufif0/bufif1的作用;

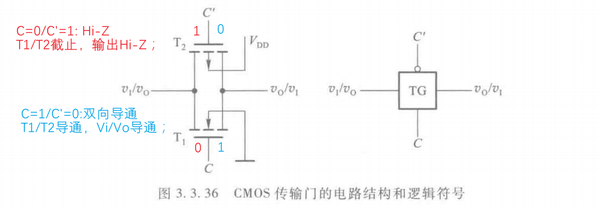

ii.电路原理

iii.应用:

a..和其它逻辑门配合可组成异或门之类的基本逻辑单元;

b.用作模拟电路的开关,用来传输连续的模拟电路信号;

3.三态门

i.概念

三态门输出电路除了有高低电平两个状态之外,还有第三个状态--Hi-Z高阻态;

ii.电路原理

iii.应用

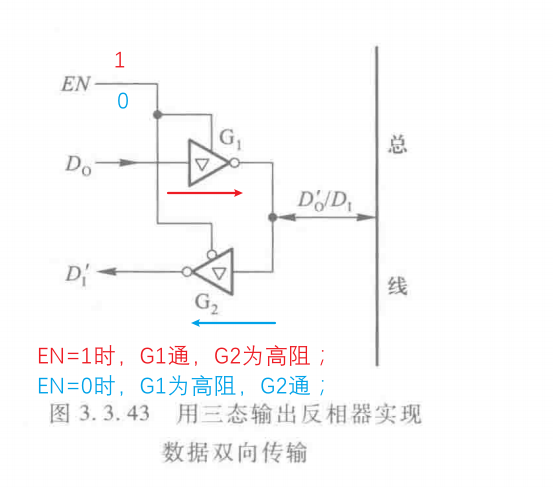

a.双向传输

在verilog我们使用inout的端口时,常常会使用这样的语句:assing out = en ? out_tmp : 1'bz;其含义是当en=1时,输出接口输出具体电平out_tmp,en=0时则当作输入接口使用,赋值为Hi-Z态,允许外部信号的拉低或者拉高;

电路结构如下图:

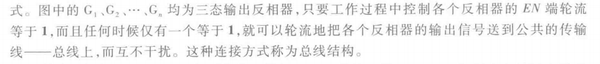

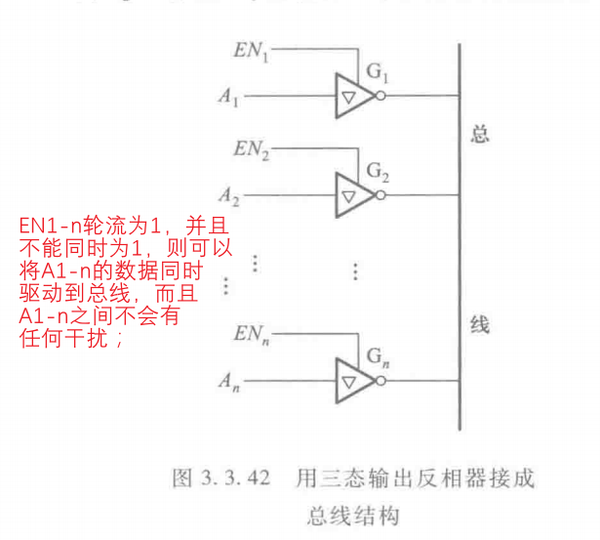

b.总线结构

电路结构:

标签:输出,OD,电平,传输,电路,三态,浅析,CMOS

From: https://www.cnblogs.com/amxiang/p/16644071.html

标签:输出,OD,电平,传输,电路,三态,浅析,CMOS

From: https://www.cnblogs.com/amxiang/p/16644071.html