一、AXI总线概述

在Xilinx系列FPGA及其有关IP核中,经常见到AXI总线接口,AXI总线又分为三种:

AXI-Lite,AXI-Full以及AXI-Stream,其中AXI-Lite和AXI-Full都是基于memory map的形式实现数据传输(即包括地址总线),而AXI-Stream是以数据流的形式传输,无地址。

其中AXI-Lite是AXI-Full的简化版,适合小批量的数据传输,常用来进行命令的传输,IP核的初始化等。

AXI-Full则适用于大批量,高性能的数据传输。

文章将对AXI-Full和AXI-Lite进行一个简单介绍,如果需要更进一步了解可以去arm官网下载手册阅读:https://www.arm.com/architecture/system-architectures/amba/amba-specifications

二、AXI总线通道

CH1 时钟和复位(Global signals)

|

信号 |

方向 |

描述 |

|

ACLK |

时钟源 |

全局时钟信号,上升沿有效 |

|

ARESETn |

复位源 |

全局复位,低有效,(只有在ACLK上升沿拉低才有效) |

CH2 写地址通道(Write address channel signals)

|

信号 |

方向 |

描述 |

|

AWID |

M -> S |

写地址ID,用来识别一组写地址信号 |

|

AWADDR |

M -> S |

写地址,给出一次突发传输的首地址,(余下地址由Slave端自己计算,每次传输地址不能超过4KB) |

|

AWLEN |

M -> S |

突发长度,一次突发传输中的长度,该信息决定了与地址相关的数据个数。在AXI3中只支持1-16个传输长度的突发(Burst_Length = AxLEN[3:0] + 1),在AXI4的INCR突发类型下,允许1-256个长度的突发,对于其他的传输类型依然保持1-16次突发传输(Burst_Length=AxLEN[7:0]+1)。 AXI突发事件有如下规则:

|

|

AWSIZE |

M -> S |

突发大小,给出每次传输的字节数,支持1、2、4、8、16、32、64、128 |

|

AWBURST |

M -> S |

突发类型,突发类型和突发大小决定slave端地址的计算。 0b00 FIXED:地址不变,常用于加载或清空FIFO 0b01 INCR:地址递增,增加的大小取决于AxSIZE的值 0b10 WRAP:回环突发,与INCR类似,但会在增加到特定的地址后回到低地址。传输的起始地址必须和每次传输的大小对齐;传输的长度只能是2、4、8、16。回环的边界=AxSIZE*AxLEN,如果在一次传输中地址超过了边界,就会进行回环;第一次传输的地址可以高于回环地址。 0b11 Reserved |

|

AWLOCK |

M -> S |

AXI4不支持,AXI3必须支持 |

|

AWCACHE |

M -> S |

内存类型,表明一次传输是怎么通过系统的。AXI3与AXI4编码不同。 |

|

AWPROT |

M -> S |

保护类型,传输的特权级别、安全等级,是指令传输还是数据传输。 AWPROT[0] 0:unprivileged access 1:privileged access AWPROT[1] 0:secure access 1:non-secure access AWPROT[2] 0:data access; 1:instruction access |

|

AWQOS |

M -> S |

服务质量,只在AXI4中有 |

|

AWREGION |

M -> S |

区域标识,允许一个物理接口用于多个逻辑接口,只在AXI4中有 |

|

AWUSER |

M -> S |

用户在写的过程中自定义的信号, |

|

AWVALID |

M -> S |

有效信号,表明Master准备发送写地址或信息了 |

|

AWREADY |

S -> M |

就绪,表明Slave准备好接收发送的信息了。 |

CH3 写数据通道(Write data channel signals)

|

信号 |

方向 |

描述 |

|

WID |

M -> S |

写ID标签,只在AXI3中有 |

|

WDATA |

M -> S |

写数据 |

|

WSTRB |

M -> S |

表明哪个字节通道写入数据。WSTRB[n:0]表明哪一个通道有效,WSTRB[n]对应WDATA[8n+7:8n],当数据有效时,WSTRB必须为高,WVALID为低时,可以为任意值。 |

|

WLAST |

M -> S |

表明该次突发传输中的最后一次传输 |

|

WUSER |

M -> S |

用户在写数据过程中自定义的信号 |

|

WVALID |

M -> S |

有效信号,表明此次写有效 |

|

WREADY |

S -> M |

就绪,表明Slave准备好接收数据了。 |

CH4 写响应通道(Write response channel signals)

|

信号 |

方向 |

描述 |

|

BID |

S -> M |

响应ID标签, |

|

BRESP |

S -> M |

写响应,表明写传输的状态 OKAY:成功 EXOKAY:表明单独的一次进程成功 SLVERR:Slave error DECERR:Decode error |

|

BUSER |

S -> M |

用户自定义信号,只在AXI4中有 |

|

BVALID |

S -> M |

写响应有效,在一次突发传输的最后拉高一次 |

|

BREADY |

M -> S |

Master能接收到写响应,与BVALID状态有关 |

CH5 读地址通道(Read address channel signals)

|

信号 |

方向 |

描述 |

|

ARID |

M -> S |

读地址ID |

|

ARADDR |

M -> S |

读地址,给出一次突发读取传输的首地址 |

|

ARLEN |

M -> S |

突发长度,一次突发传输中的长度,该信息决定了与地址相关的数据个数。在AXI3中只支持1-16个传输长度的突发(Burst_Length = AxLEN[3:0] + 1),在AXI4的INCR突发类型下,允许1-256个长度的突发,对于其他的传输类型依然保持1-16次突发传输(Burst_Length=AxLEN[7:0]+1)。 AXI突发事件有如下规则:

|

|

ARSIZE |

M -> S |

突发大小,给出每次传输的字节数,支持1、2、4、8、16、32、64、128 |

|

ARBURST |

M -> S |

突发类型,突发类型和突发大小决定slave端地址的计算。 0b00 FIXED:地址不变,常用于加载或清空FIFO 0b01 INCR:地址递增,增加的大小取决于AxSIZE的值 0b10 WRAP:回环突发,与INCR类似,但会在增加到特定的地址后回到低地址。传输的起始地址必须和每次传输的大小对齐;传输的长度只能是2、4、8、16。回环的边界=AxSIZE*AxLEN,如果在一次传输中地址超过了边界,就会进行回环;第一次传输的地址可以高于回环地址。 0b11 Reserved |

|

ARLOCK |

M -> S |

AXI4不支持,AXI3必须支持 |

|

ARCACHE |

M -> S |

内存类型,表明一次传输是怎么通过系统的。AXI3与AXI4编码不同。 |

|

ARPROT |

M -> S |

保护类型,传输的特权级别、安全等级,是指令传输还是数据传输。 AWPROT[0] 0:unprivileged access 1:privileged access AWPROT[1] 0:secure access 1:non-secure access AWPROT[2] 0:data access; 1:instruction access |

|

ARQOS |

M -> S |

服务质量,只在AXI4中有 |

|

ARREGION |

M -> S |

区域标识,允许一个物理接口用于多个逻辑接口,只在AXI4中有 |

|

ARUSER |

M -> S |

用户在写的过程中自定义的信号, |

|

ARVALID |

M -> S |

有效信号,表明Master准备发送写地址或信息了 |

|

ARREADY |

S -> M |

就绪,表明Slave准备好接收发送的信息了。 |

CH6 读数据通道(Read data channel signals)

|

信号 |

方向 |

描述 |

|

RID |

S -> M |

读ID标签,只在AXI3中有 |

|

RDATA |

S -> M |

读数据 |

|

RRESP |

S -> M |

读响应,表明写传输的状态 OKAY:成功 EXOKAY:表明单独的一次进程成功 SLVERR:Slave error DECERR:Decode error。 |

|

RLAST |

S -> M |

表明该次突发传输中的最后一次传输 |

|

RUSER |

S -> M |

用户在写数据过程中自定义的信号 |

|

RVALID |

S -> M |

有效信号,表明该通道需要读取数据 |

|

RREADY |

M -> S |

就绪,表明Master准备好接收数据了。 |

AXI总线的握手机制

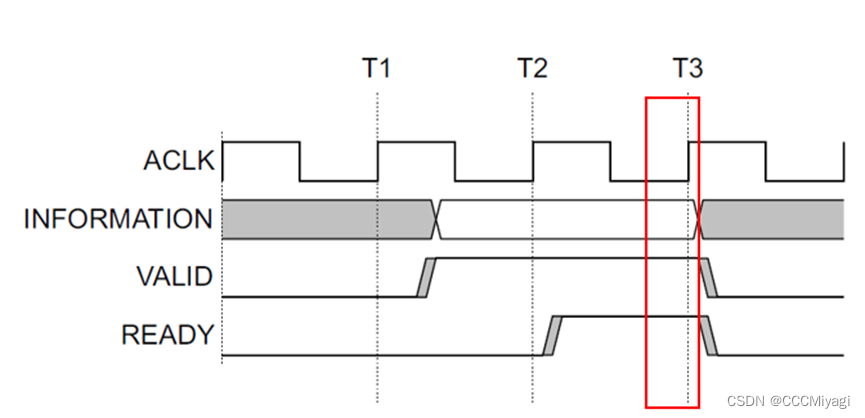

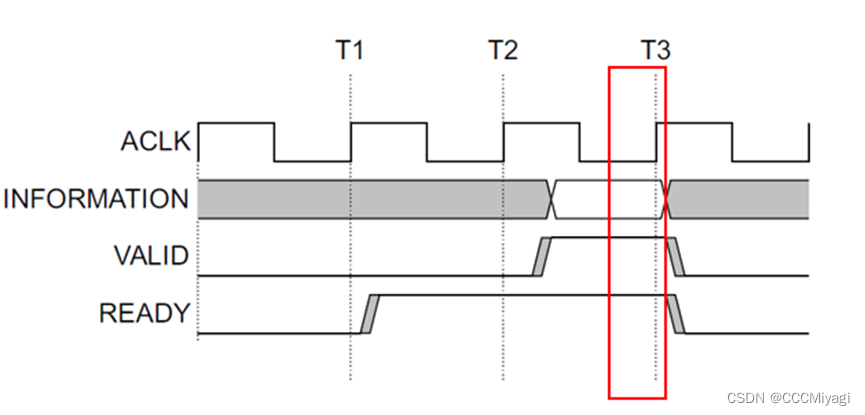

AXI总线的五个通道都使用的是相同的VALID和READY握手,发送端发送的VALID信号表明此时发送出去的信息有效,接收端发出的READY信号表明此时接收端已经准备好了接收信息,该握手机制存在三种情况:

发送端准备好了信息,发送VALID信号,此时接收端还未准备好接收,如果在下一个时钟周期接收端准备好了,就会把READY拉高。此时VALID和READY都为高,完成一次传输。

接收端处于准备接收的状态,READY为高,一旦发送端准备好了信息,发送VALID信号,此时接收端在时钟上升沿直接接收,完成一次传输。

发送端准备好了信息,发送VALID信号,此时接收端也准备好接收,READY为高,完成一次传输。

VALID信号和READY信号的拉高不分先后,只要同时为高,就完成了一次握手,

标签:access,总线,介绍,突发,传输,地址,信号,AXI From: https://www.cnblogs.com/amxiang/p/16873343.html