这里给出一些我看过的参考文档,相信这些博主的内容已经让您对GT高速收发器有了初步了解

https://blog.csdn.net/lum250/article/details/119952822

(特别详细的CSDN教程,分析了英文文档,并且把每一个勾选的内容都陈述了)主讲IP

https://zhuanlan.zhihu.com/p/46052855

(对GT接口,在结构上进行了描述,绘出了结构图。说明了Loop回环的作用)

https://blog.csdn.net/qq_40147893/article/details/109380458?

(讲了example文件是什么的blog)

在本文中,我将首先对GT高速收发器进行概括,接着设计IP核并对example文件和信号进行分析。主要参考资料来源于赛灵思官网IP核:UserGuide:ug476_7Series_Transceivers_2.pdf

1. 什么是GT高速收发器?

- 它是集成在FPGA芯片内部的固定电路,因此我们只需要关心该固定电路与FPGA的逻辑部分接口时序即可

- 它是串行收发器,发送出去只有1bit数据,而接收端也是1bit线。但FPGA与该器件的接口数据是多bit的,因此该收发器同时也是一个高速并串转换器。

- 它是高速收发器,一般线速率可达Gbps。GT分为不同系列,在不同的系列中有不同的速度

2. GT高速收发器的结构

(1)整体结构

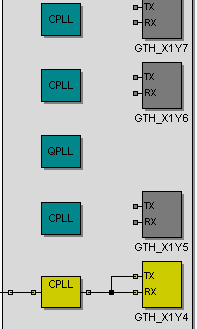

如下图所示,GT的基本单位为Quad,每个Quad包含四个通道(Channel),四个对应的CPLL,以及一个QPLL。

图中我们开启了GTH_X1Y4(Q1的通道1),那么可以看出对应的CPLL和Channel就建立了连接。CPLL只能给对应的通道提供时钟,而QPLL可以同时给一个Quad中的四个Channel同时提供时钟。

那CPLL和QPLL的时钟是从哪来的?答案是外部时钟REFCLK。具体REFCLK是如何突破重重险阻,按照GT要求的复杂规则供给给CPLL和QPLL的,将在下一篇有关时钟的文章中讲到。

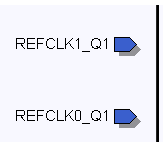

值得注意的是,每个Quad都有对应的REFCLK.比如Q1的参考时钟就是REFCLK1_Q1和REFCLK0_Q1;Q2的就是REFCLK1_Q2和REFCLK0_Q2。

而GT有一个特性:就是每个参考时钟可以和自己相邻的两个Q同时提供时钟。例如我们现在有Q1Q2Q3Q4,那么Q2的参考时钟REFCLK1_Q2可以同时给Q1Q2Q3提供时钟;Q1的参考时钟因为排在第一位,而且不存在Q0,所以只能给Q1和Q2提供时钟。

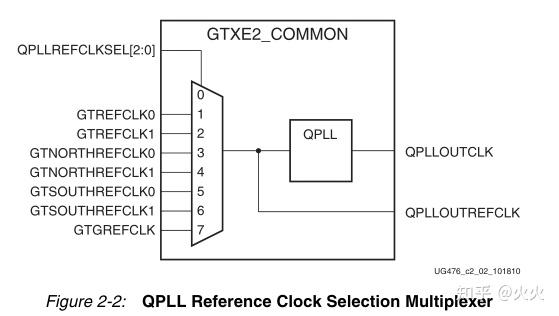

如下图所示:假如现在是Q2,QPLL的输入可以是GTREFCLK0/1(自身的参考时钟);可以是GTNORTHREFCLK0/1(自身北方的,即Q3的参考时钟);可以是GTSOUTHREFCLK0/1(自身南方的,即Q1的参考时钟);也可以是GTGREFCLK(FPGA内部逻辑产生的参考时钟。此输入仅用于内部测试目的)

这样做的好处是:(1)节省了时钟源个数,节省了走线(2)节省了外部引脚个数,假如我们使用三个GT收发器Q1Q2Q3,则只给中间的Q2

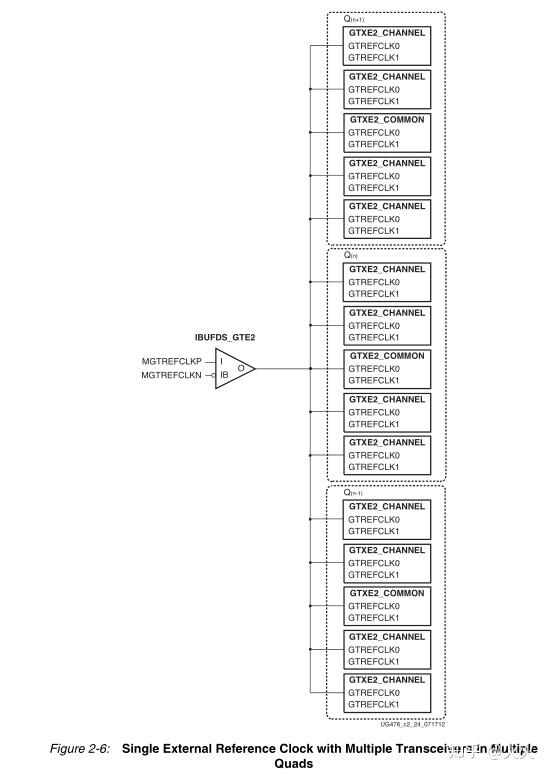

下图中的MGTREFCLKP/N是外部参考时钟输入,同GTREFCLK1_Q1等。在这里是差分时钟输入,经过原语IBUFDS_GTE2之后变成单端时钟对CPLL和QPLL提供参考时钟。

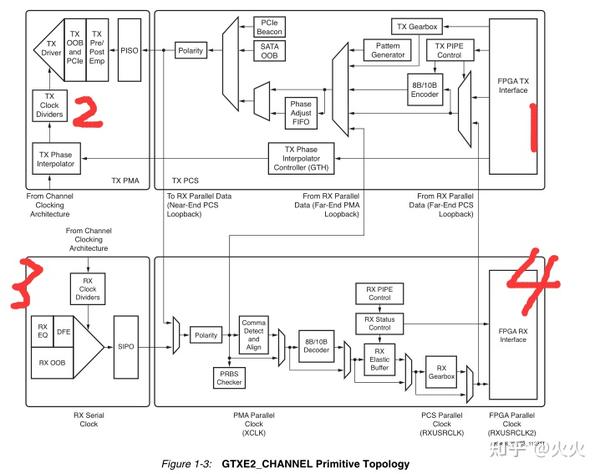

(2)具体每个CHANNEL的结构

如下图所示:从收发流程来看可以分为四部分:

- FPGA与TX CHANNEL的接口

- TX CHANNEL与外部管脚

- RX CHANNEL与外部管脚

- FPGA与RX CHANNEL的接口

而在仿真过程中,我们也只需要关心这四部分信号即可,接下来创建IP核观察

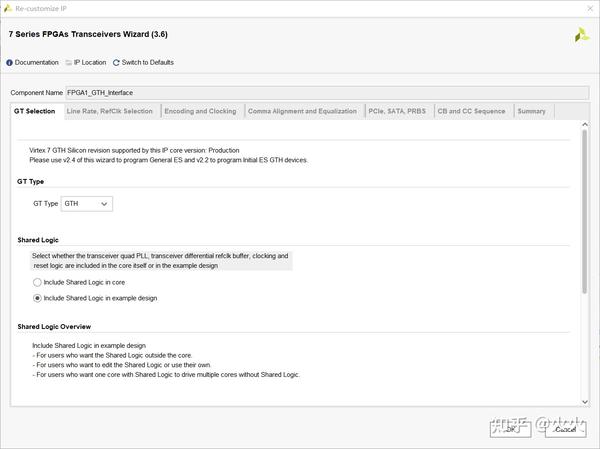

3. GT高速收发器IP核创建

第一页:

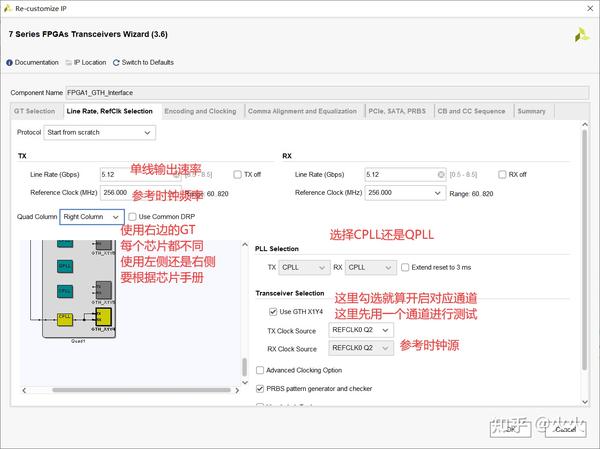

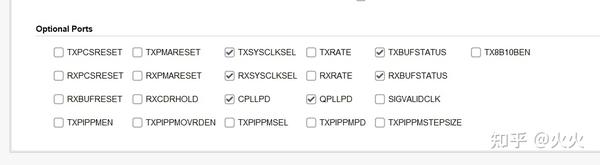

第二页:

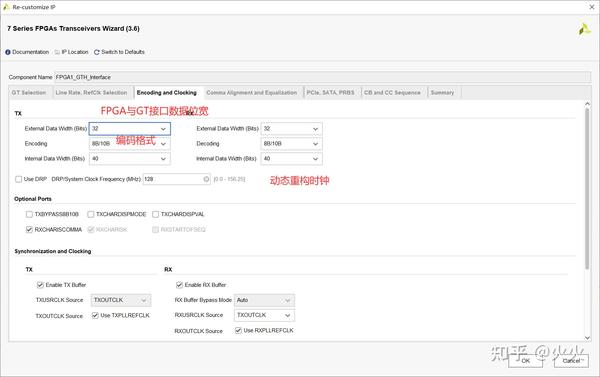

第三页:

第四页:

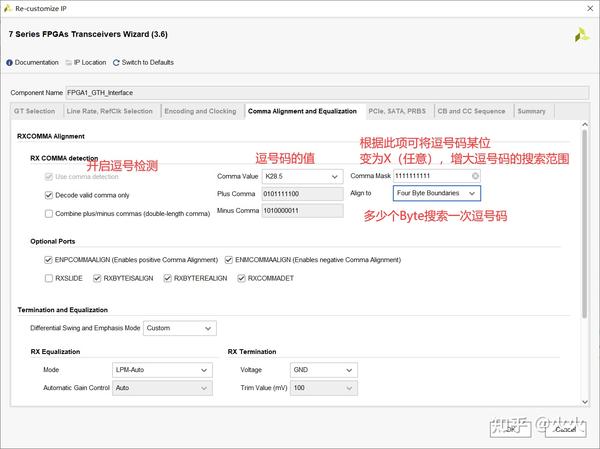

有关逗号码:

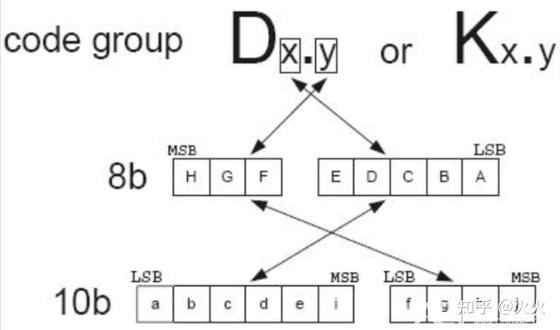

首先8B/10B编码是把一个8bit数通过某种编码变成10bit数,并且得出的10bit数中的0和1的个数更平衡,以此减少直流分量。

8B/10B编码是由高3位的3B/4B编码加上5B/6B编码组成的,而K28.5就是由5(101)和28(11100)组成,即10111100,十六进制则是BC。经过编码表变成10bit数。

那么为什么要使用逗号码?

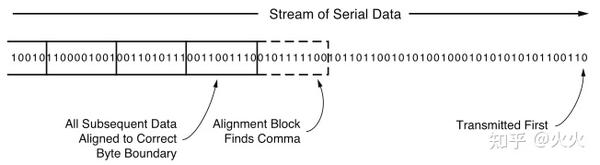

如下所示,串行收发器接收到一个一个的1bit数据,就像汉字一样,接收到一个一个的汉字。我们需要逗号把汉字隔开才能明白句子的意思,而数据也一样。

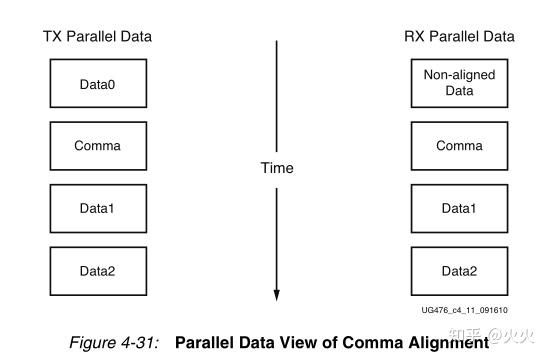

如下图所示,左边为发送端的并行数据,右边为接受端的并行数据。当接收到逗号码之后才开始接收Data1,有点类似于开始符。

发送端和接收端与FPGA的接口除之前定义的32bit数之外,还有4个1bit组成的4bit CHARISK数据。

TXCHARISK端口用于指示TXDATA上的数据是K个字符还是常规数据。8B/10B编码器检查接收到的TXDATA字节,以匹配任何K字符,如果对应的TXCHARISK位驱动为高。简单来说,当TXCHARISK拉高,编码器就把该数据编码为逗号,否则编码为普通数据。

当接收检测到逗号码的时候,对应RXCHARISK会拉高。来辅助接收端把数据进行对齐,当勾选了IP核中的RXSLIDE,就需要手动产生RXCHARISK。

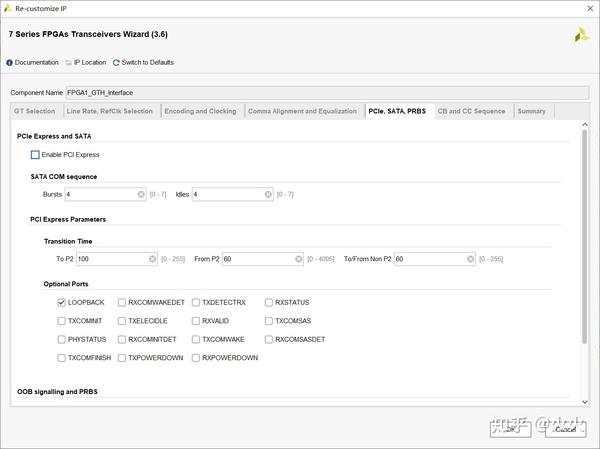

第五页:

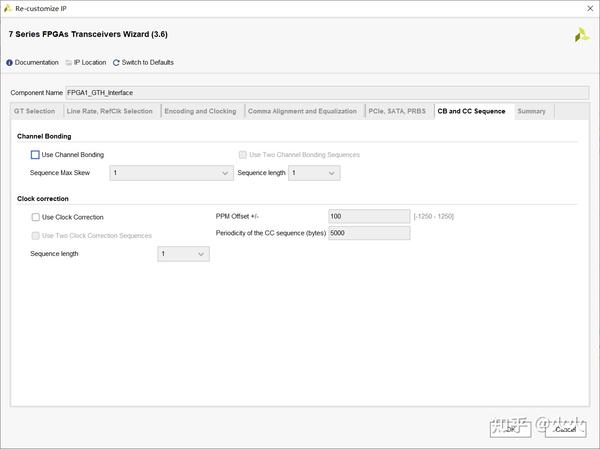

第六页:

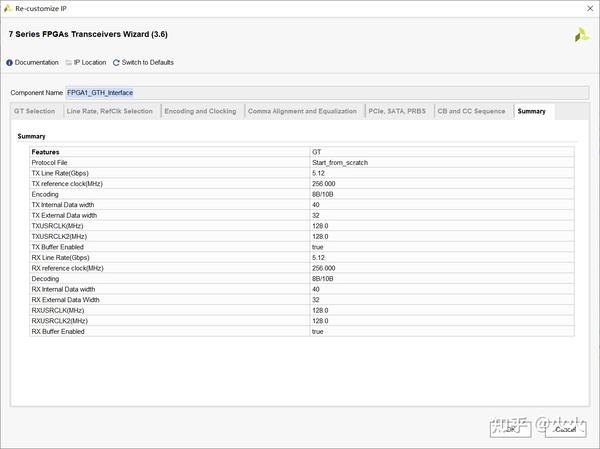

第七页

4. IP核产生的example文件

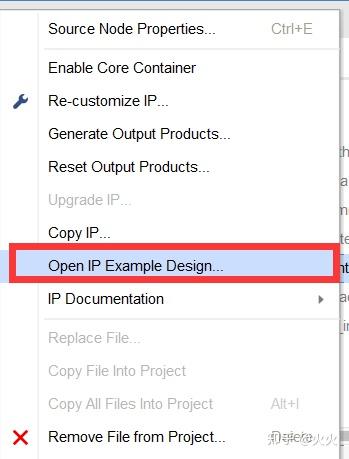

在IP核界面右键点击Open IP Example Design生成自带的自发自收例程

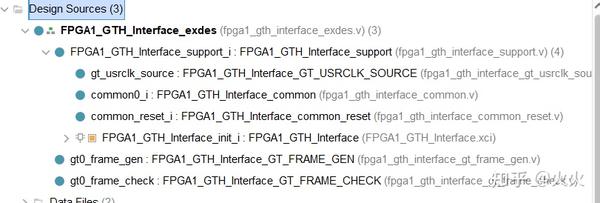

(1)FPGA1_GTH_Interface_exdes.v为整体工程的TOP文件

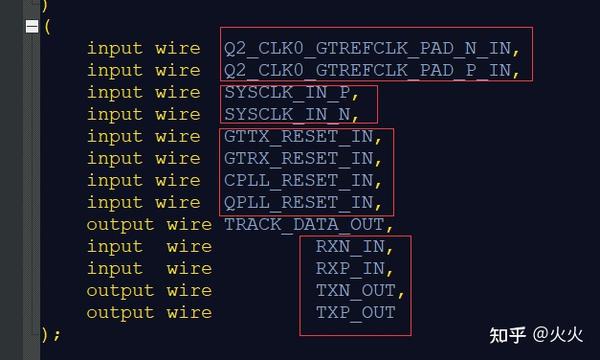

输入输出端口分别为:

Q2_CLK0_GTREFCLK_PAD_N/P_IN:外部差分输入参考时钟

SYSCLK_IN_P/N:系统时钟

TXP/N_OUT:发送1bit差分输出

RXP/N_IN:接收1bit差分输入

以及GT发送接收,CPLL和QPLL的复位

(2)FPGA1_GTH_Interface_support.v

该文件主要例化了GT高速收发器的IP核,并对时钟进行了配置

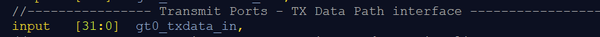

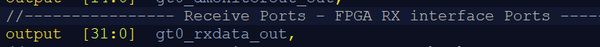

例如FPGA与GT的接口:32bit的待发送数据gt0_txdata_in:

32bit的接收数据gt0_rxdata_out

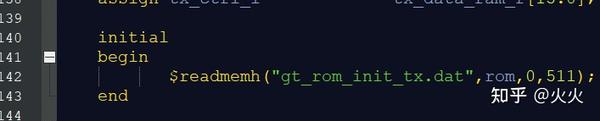

(3)FPGA1_GTH_Interface_GT_FRAME_GEN.v

该文件用于产生发送数据的来源,本质上是从ROM中读取数据。

(4)FPGA1_GTH_Interface_GT_FRAME_CHECK.v

该文件用于接收到数据后,与文件中的数据源进行比对,并且记录下错误的数据个数。

(5)FPGA1_GTH_Interface_TB.v

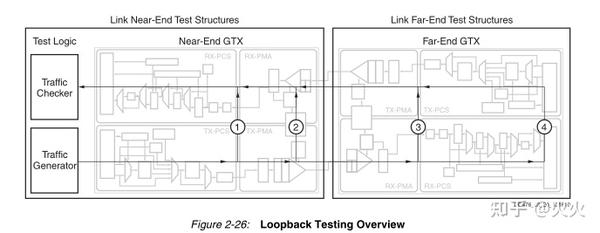

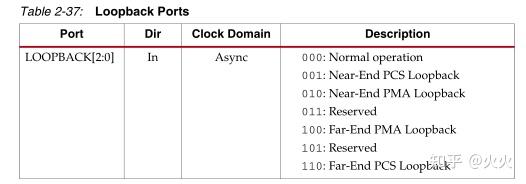

在说此文件之前,我想说一声LOOPBACK的问题。从手册中得知收发器有专门的回环模式进行测试,即进行自发自收,如下图所示有四个通道。

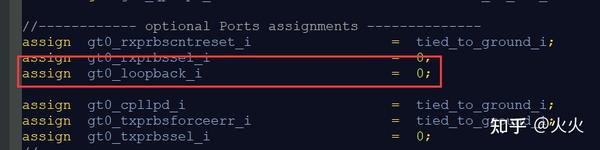

那么我们测试的时候怎么看工程中选择哪种路径呢?即搜索LOOPBACK变量

在TOP文件中我们发现,LOOPBACL居然设置的是0,即Normal 模式,并没有进行回环测试(如下图)。那么本例是如何实现的呢?

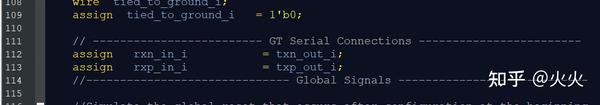

观察TB文件111行,这里是直接在仿真中把发送端和接收端用线连在一起实现回环测试

(6)观察Modelsim仿真结果

生成IP Example之后,我们不需要进行任何代码的修改,直接点击Run Simulation即可开始仿真。

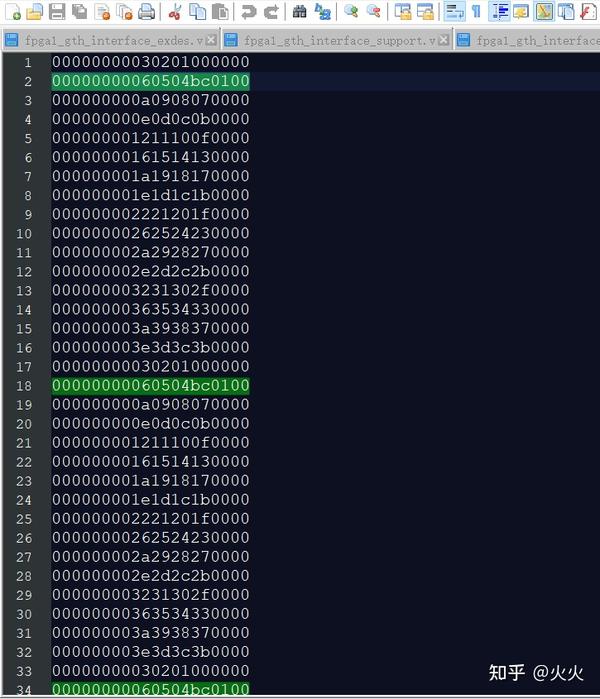

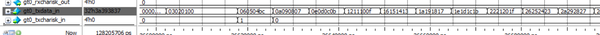

已知本例的功能是自发自收,因此我们需要关注的信号只有四个:

FPGA1_GTH_Interface_support.v中的:

gt0_txdata_in,gt0_txcharisk_in; gt0_rxcharisk_out ;gt0_rxdata_out

发送端:

自从gt0_txcharisk_in变为0001开始,第一个发送数据为060504bc,后续依次为0a090807,0e0d0c0b……

接收端:

可以看出自从gt0_rxcharisk_out变为0001开始,接收数据依次为060504bc,0a090807,0e0d0c0b……和发送端一致。说明测试成功!

总结:

GT高速收发器的IP Example已经具有相当完备的功能。后续操作只需要对该模板进行修改即可,若想要发送自己想要的序列,只需要改动FPGA1_GTH_Interface_GT_FRAME_GEN.v文件即可。

若想要改变接受序列及后续操作,只需要改FPGA1_GTH_Interface_GT_FRAME_CHECK.v文件即可。

有关时钟相关内容将在下一篇笔记在叙述

强烈建议学习过程中,阅读完各种各样的博客,有了大致概念之后就开始阅读User Guide。

标签:GT,GTH,IP,VIVADO,收发器,Q2,时钟

From: https://www.cnblogs.com/amxiang/p/16847222.html

标签:GT,GTH,IP,VIVADO,收发器,Q2,时钟

From: https://www.cnblogs.com/amxiang/p/16847222.html