[FAQ] 各种逻辑输出类型(推挽、开漏、三态)之间有何差异? - 逻辑论坛 - 逻辑 - E2E™ 设计支持

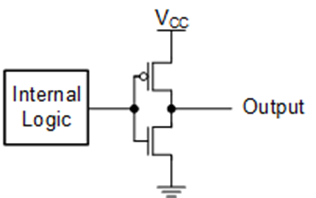

推挽输出

推挽输出可在高电平状态下拉出电流或在低电平状态下灌入电流。在现代 CMOS 器件中,推挽输出的最常见配置如下所示:

|

输出状态 |

正驱动器 (pFET) |

负驱动器 (nFET) |

|

高电平 |

导通 |

关断 |

|

低电平 |

关断 |

导通 |

当输出处于高电平状态时:

P 沟道 MOSFET 导通,并从 VCC 向输出端拉出电流。

N 沟道 MOSFET 关断,不允许电流流向 GND。

当输出处于低电平状态时:

P 沟道 MOSFET 关断,不允许电流从 VCC 流出。

N 沟道 MOSFET 导通,并从输出端向 GND 灌入电流。

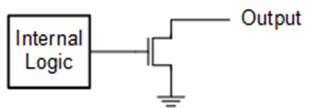

开漏输出

开漏输出只能在低电平状态下灌入电流。在现代 CMOS 器件中,开漏输出的最常见配置如下所示:

|

输出状态 |

负驱动器 (nFET) |

|

高阻态 |

关断 |

|

低电平 |

导通 |

当输出处于高阻态时,N 沟道 MOSFET 关断,不允许任何电流流动。

当输出处于低电平状态时,N 沟道 MOSFET 导通并从输出端向 GND 灌入电流。

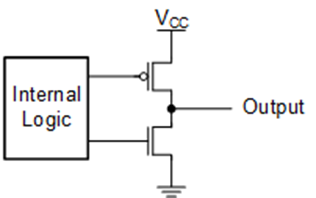

三态输出

三态输出可处于三种状态之一:驱动高电平、驱动低电平或不驱动(高阻抗)。三态输出的最常见配置如下所示:

|

输出状态 |

正驱动器 (pFET) |

负驱动器 (nFET) |

|

高电平 |

导通 |

关断 |

|

低电平 |

关断 |

导通 |

|

高阻态 |

关断 |

关断 |

当输出处于高电平状态时:

P 沟道 MOSFET 导通,并从 VCC 向输出端拉出电流。

N 沟道 MOSFET 关断,不允许电流流向 GND。

当输出处于低电平状态时:

P 沟道 MOSFET 关断,不允许电流从 VCC 流出。

N 沟道 MOSFET 导通,并从输出端向 GND 灌入电流。

当输出处于高阻态时:

P 沟道 MOSFET 关断,不允许电流从 VCC 流出。

N 沟道 MOSFET 关断,不允许电流流向 GND。

标签:输出,MOSFET,推挽,沟道,FAQ,有何,低电平,导通,关断 From: https://www.cnblogs.com/zp11/p/18605440