第三章 组合逻辑电路

概述

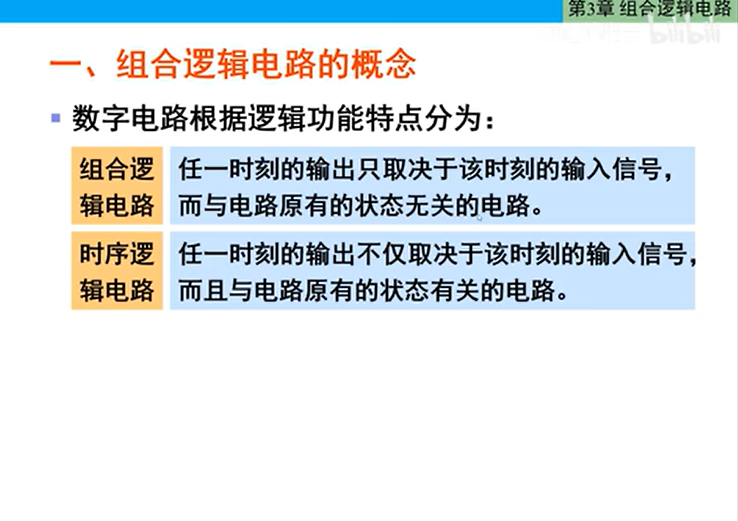

一,组合逻辑电路的概念

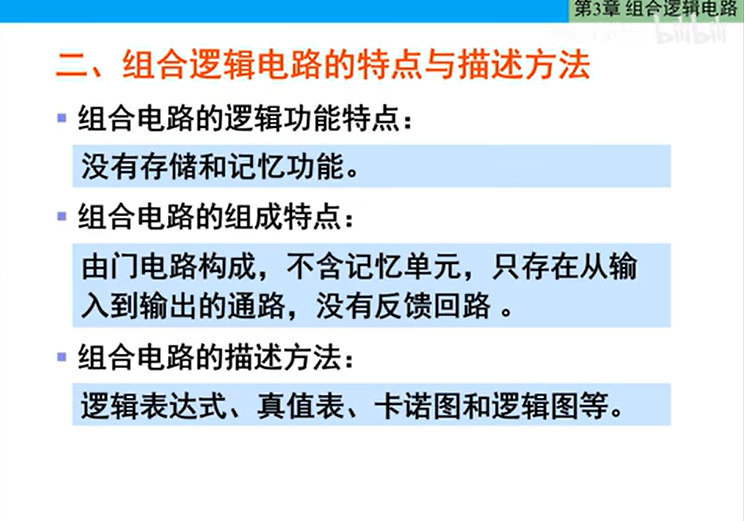

二,组合逻辑电路的特点与描述方法

3.1 组合电路的分析和设计

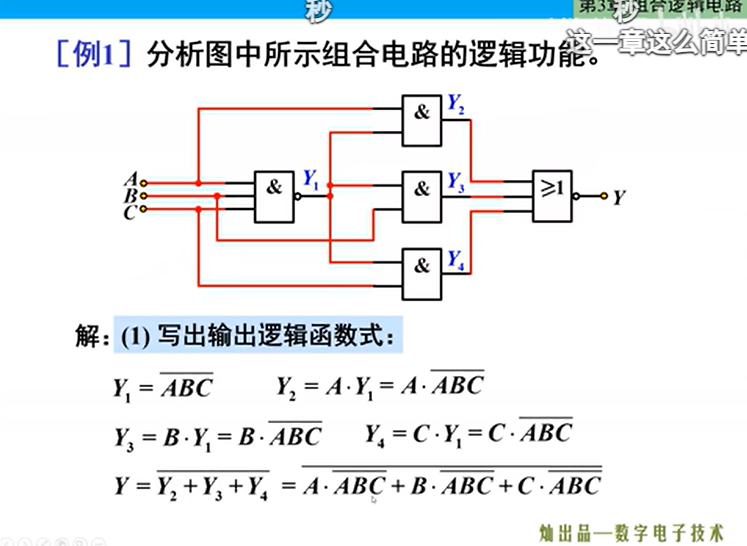

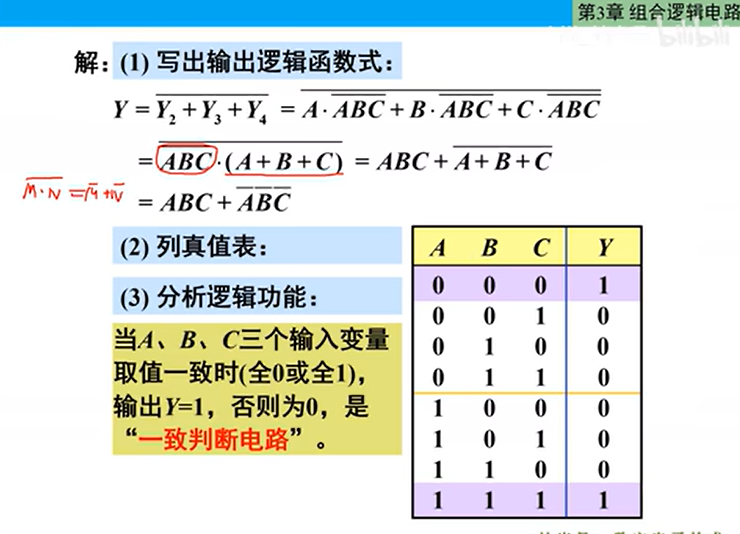

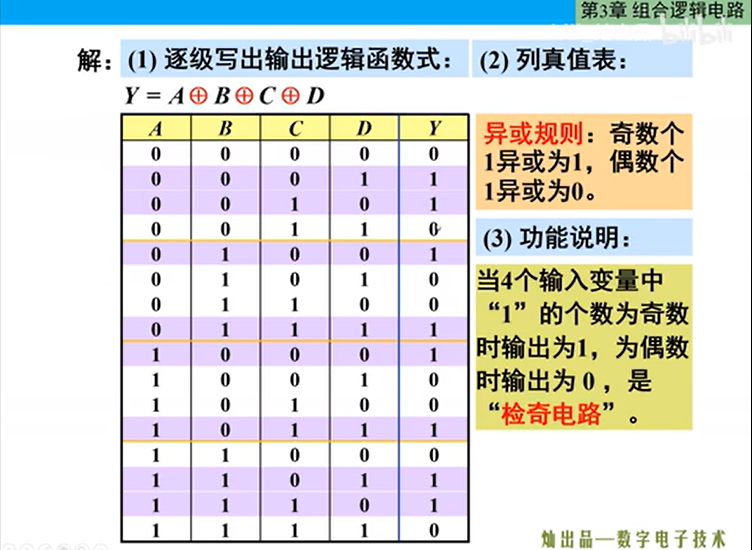

3.1.1 组合逻辑电路的分析

思路:根据给定的逻辑电路,找输入输出逻辑关系。确定功能

步骤:逻辑图——表达式——化简/变换

——真值表——功能说明

i

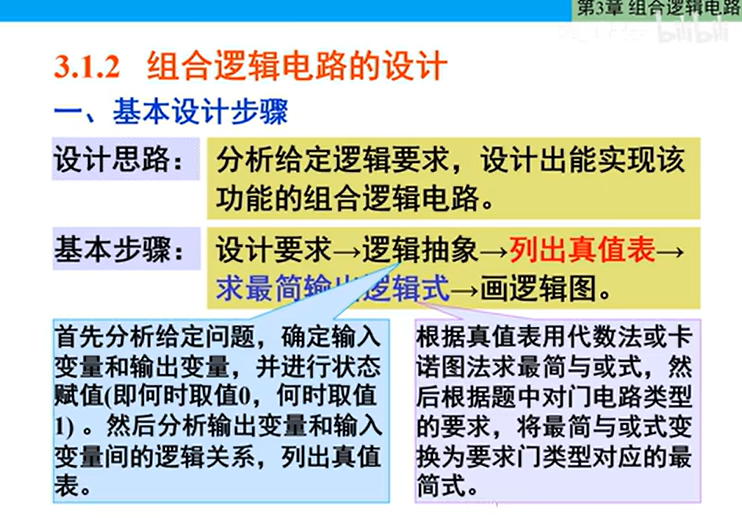

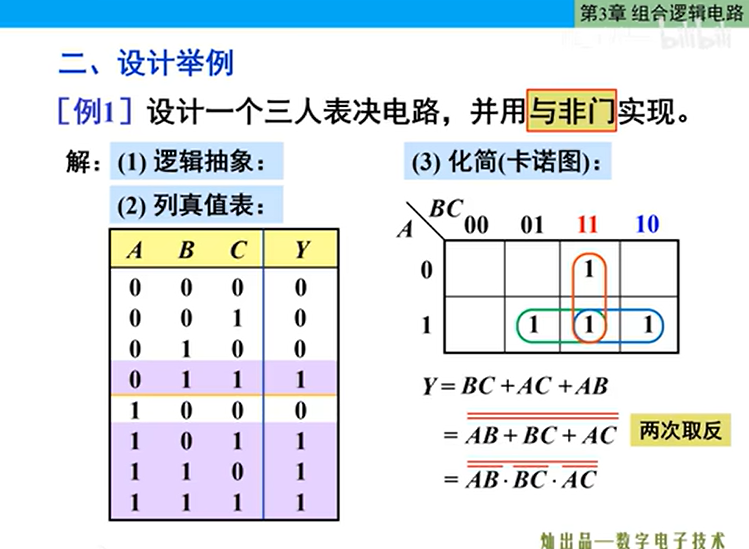

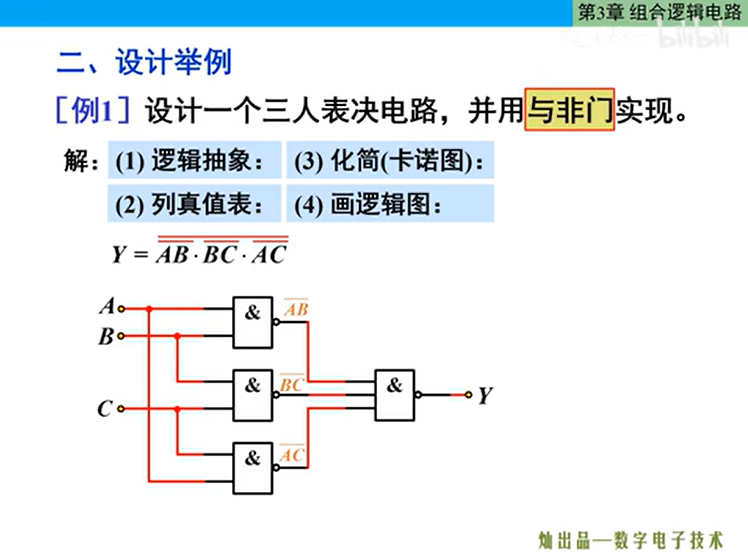

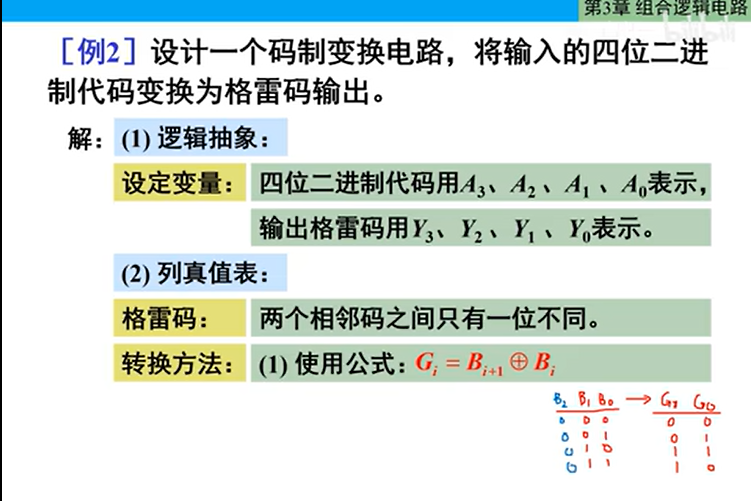

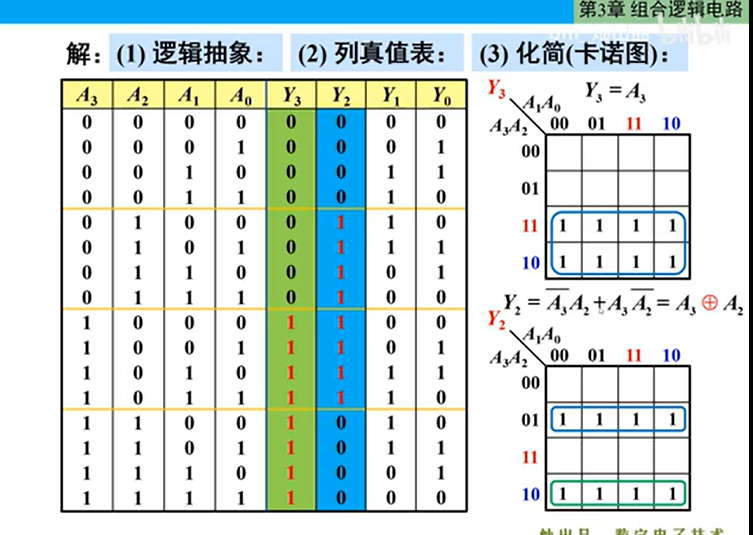

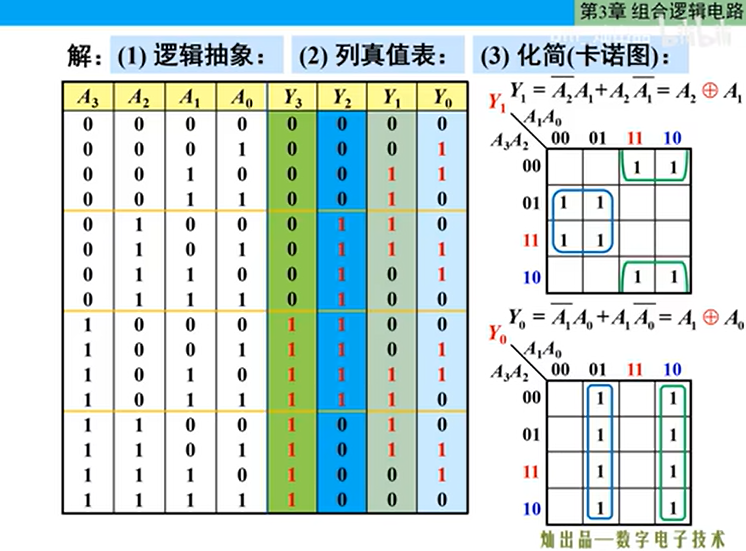

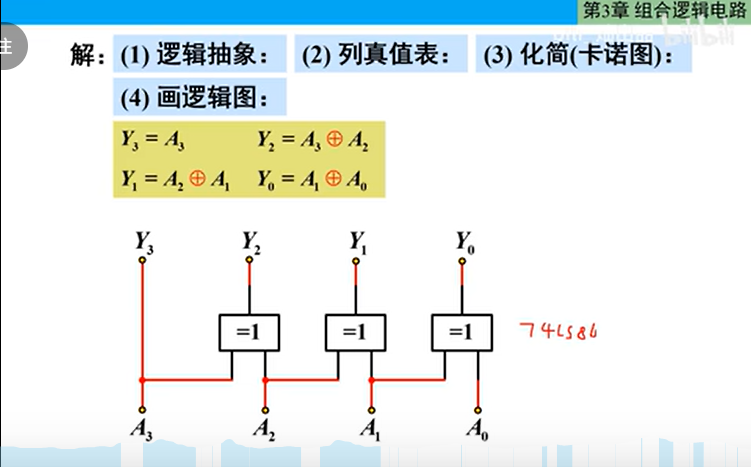

3.1.2 组合逻辑电路的设计

1,基本设计步骤

设计要求-逻辑抽象-列出真值表-求最简-画逻辑图

(2)使用卡诺图

3.2加法器和数值比较器

3.2.1 半加器和全加器

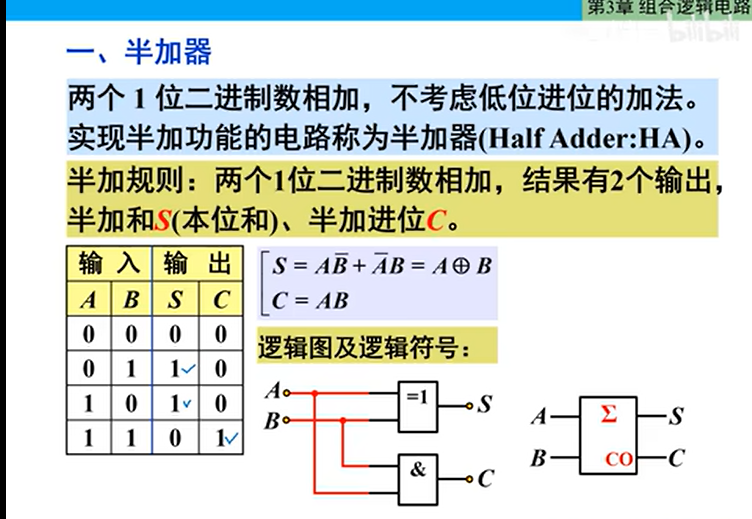

1,半加器

两个1位二进制数相加,不考虑低位进位的加法,实现半加功能的电路称为半加器。

半加规则:两个1位二进制数相加,结果有两个输出,变加和S,半加进位C。

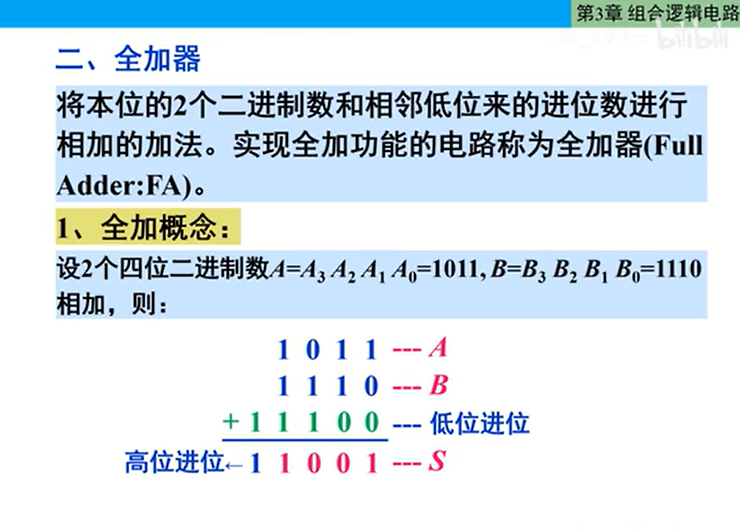

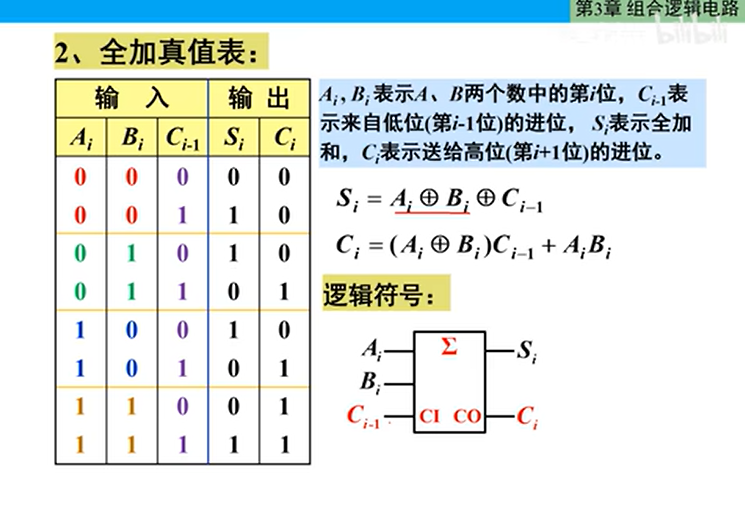

2,全加器

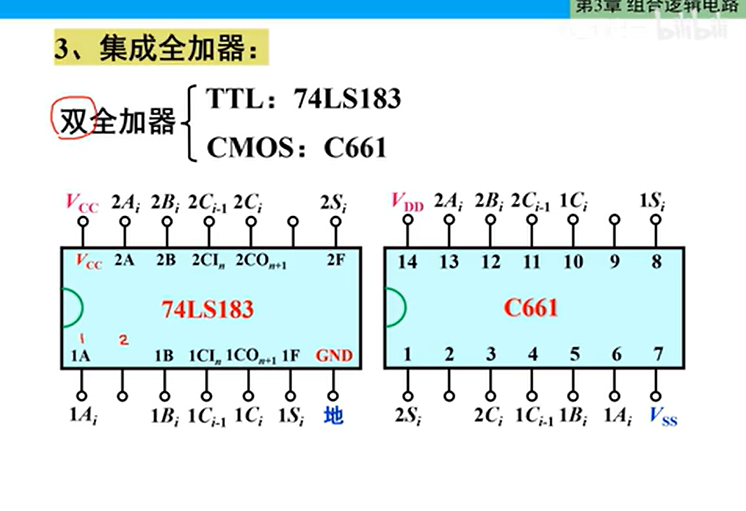

3,集成全加器:

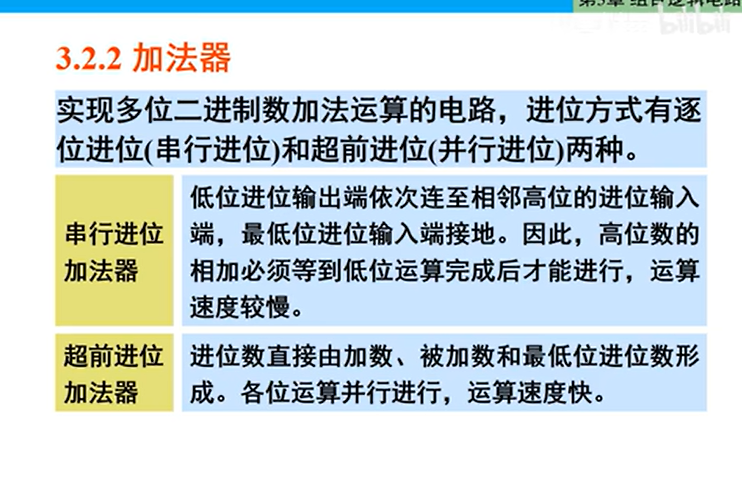

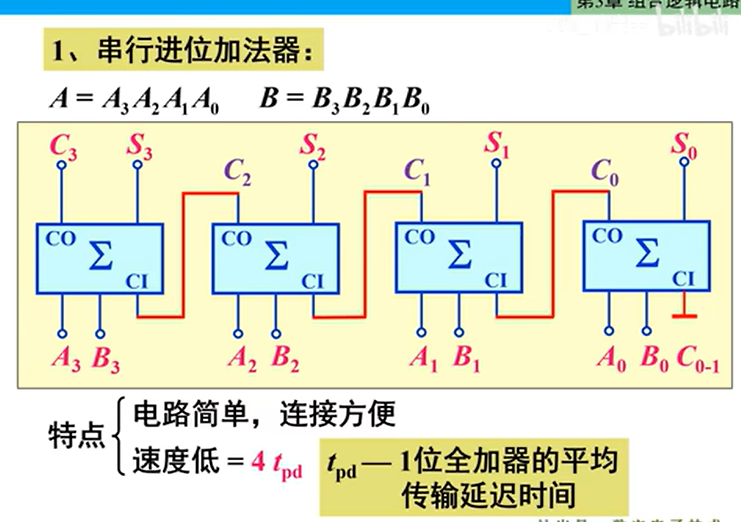

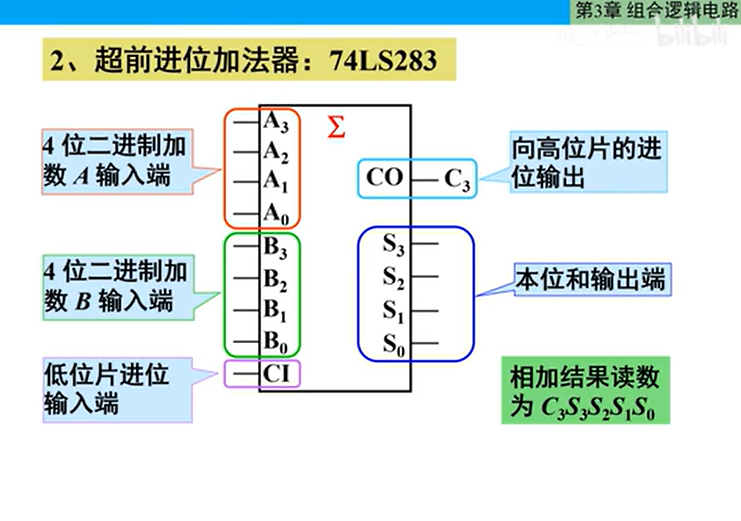

3.2.2 加法器

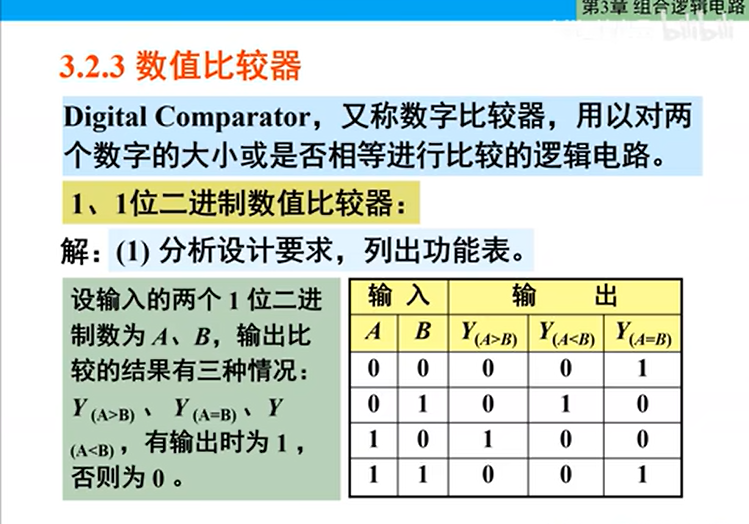

3.2.3 数值比较器

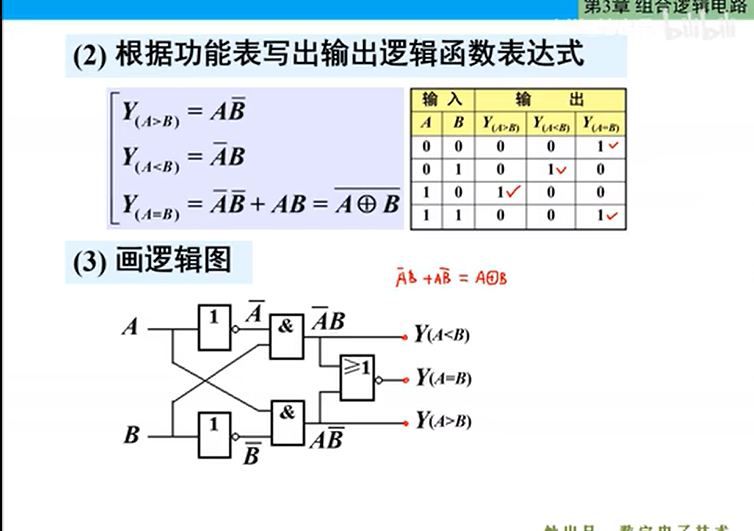

1,1位二进制数值比较器:

(1)列出功能表

(2)写出逻辑函数表达式

(3)画逻辑图

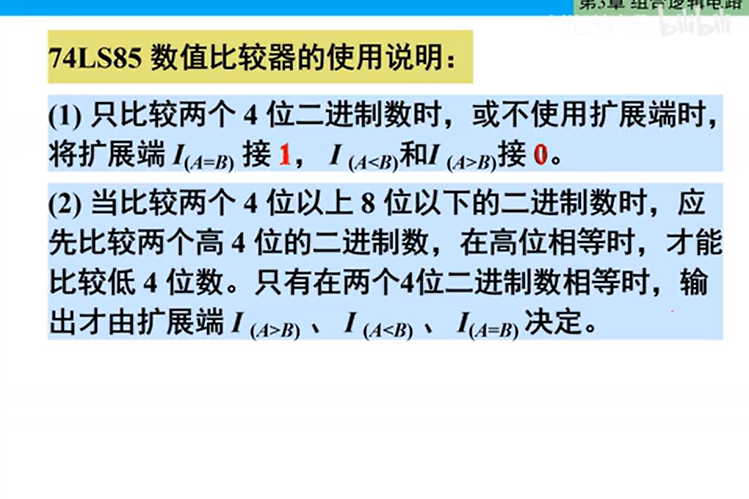

2,多位数值比较器

原理:从最高位开始逐渐向低位进行比较

3.3 编码器和译码器

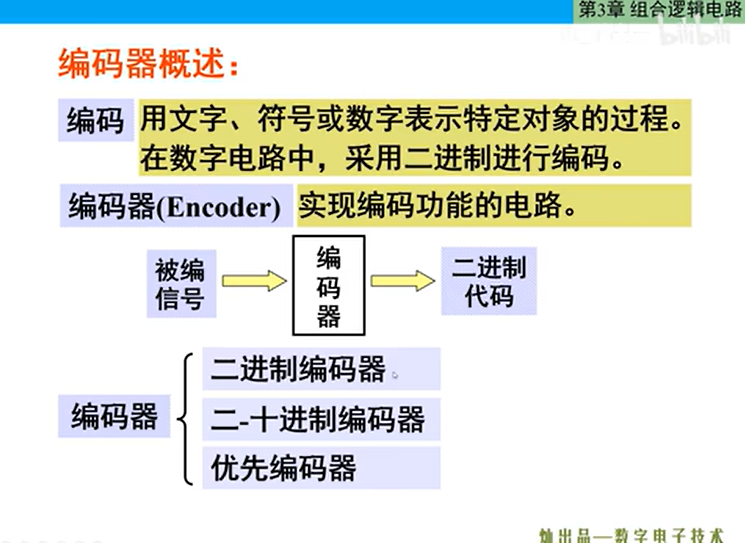

编码器概述:

3.3.1 二进制编码器

将N=2^n个输入信号转换成n为二进制代码的逻辑电路

3.3.2 二-十进制编码器

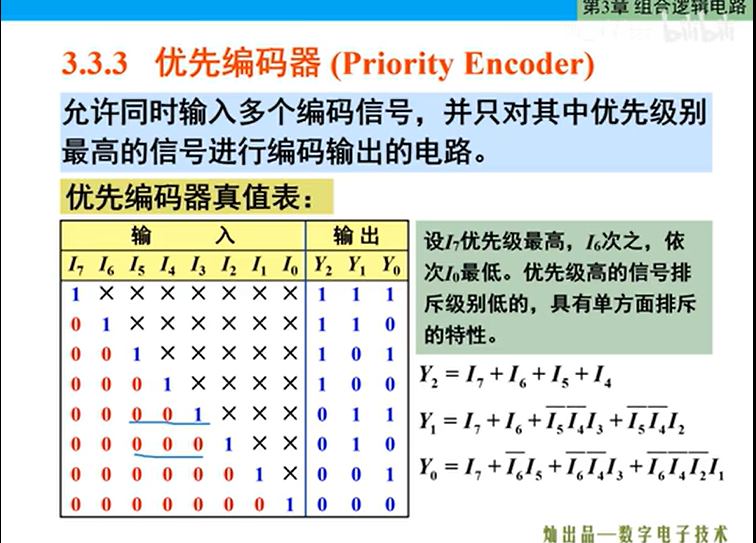

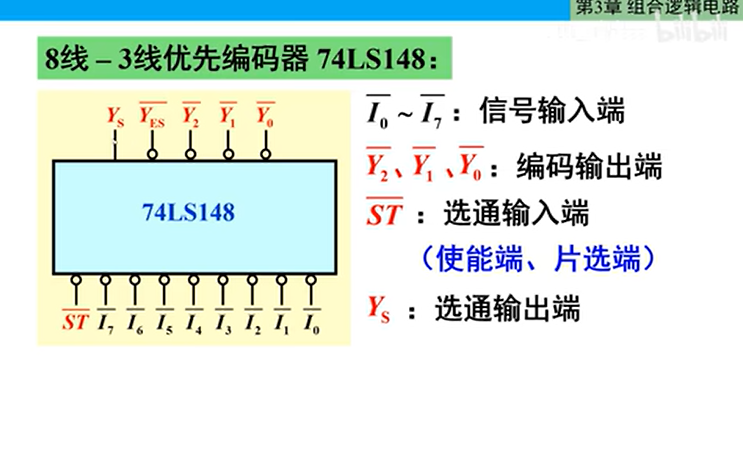

3.3.3 优先编码器

允许同时输入多个编码信号,并只对其中优先级别最高的信号进行编码输出的电路

加非好代表低电平有效

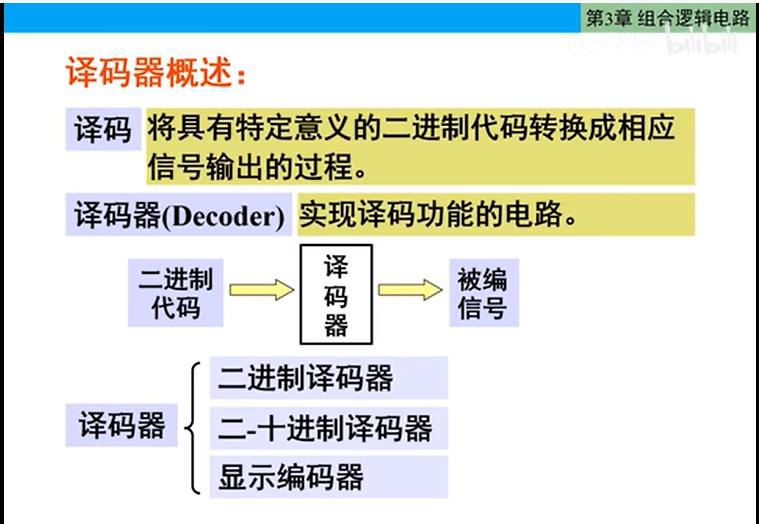

译码器概述

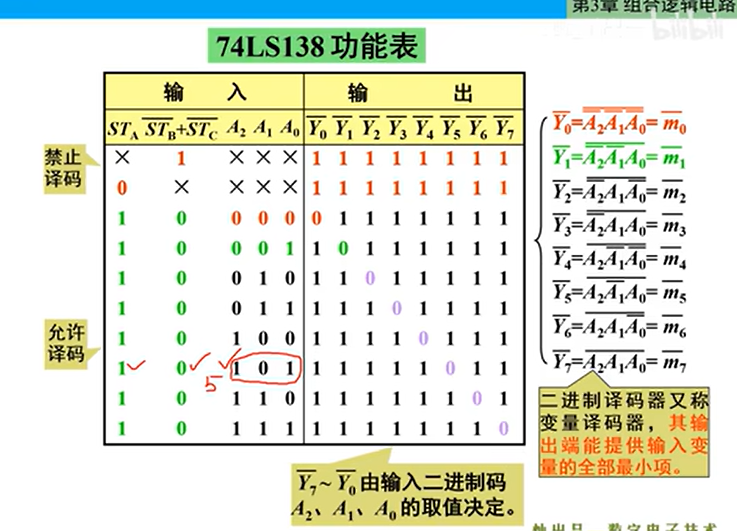

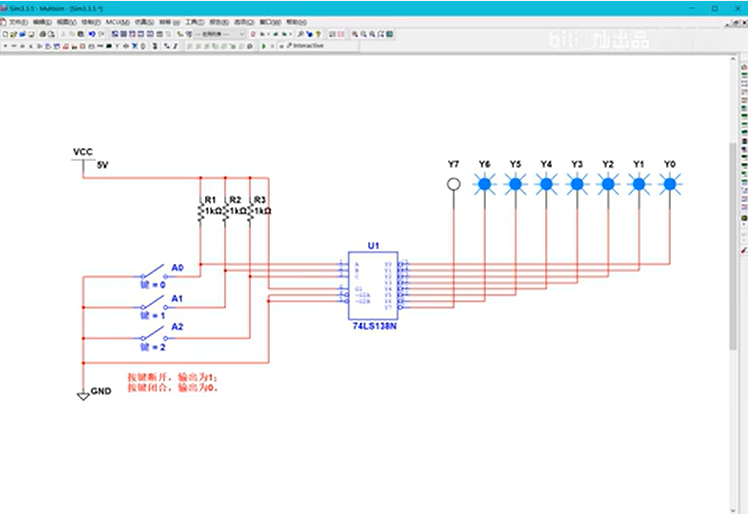

3.3.4二进制译码器

3.3.4二进制译码器

将输入二进制代码的各种组合按其愿意转换成对应信号输出的逻辑电路

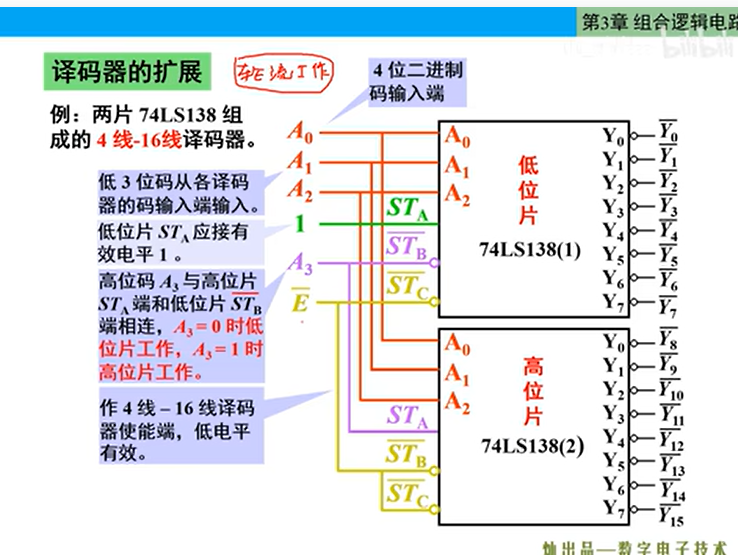

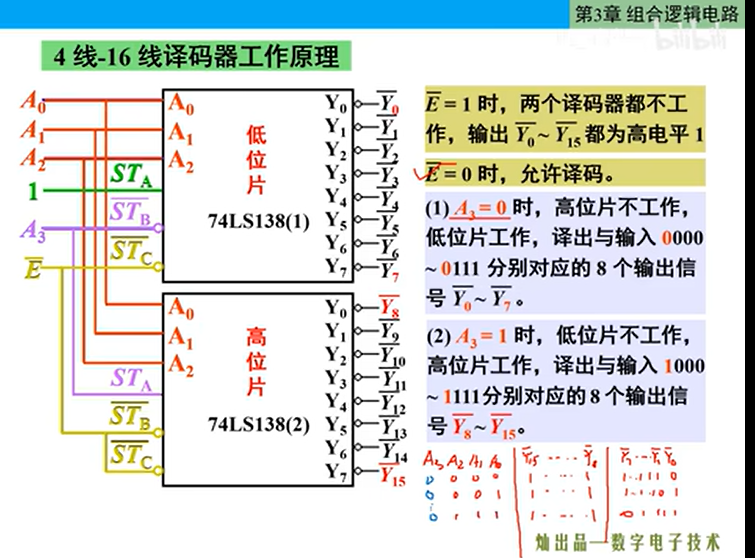

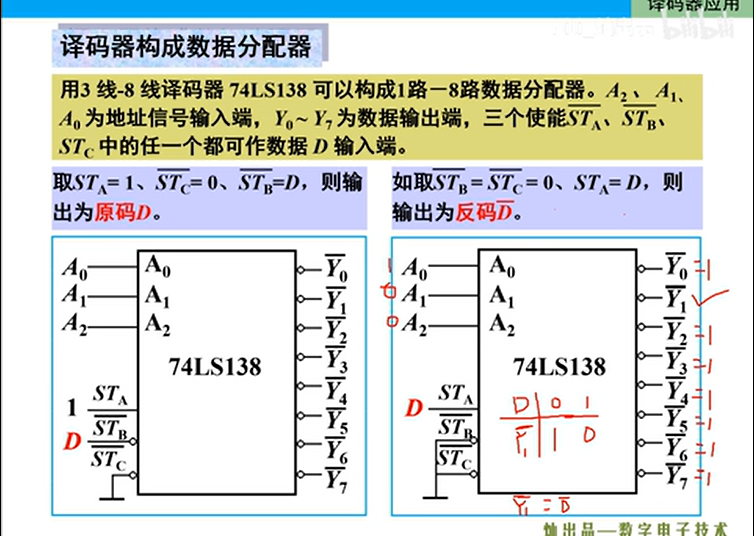

译码器的扩展

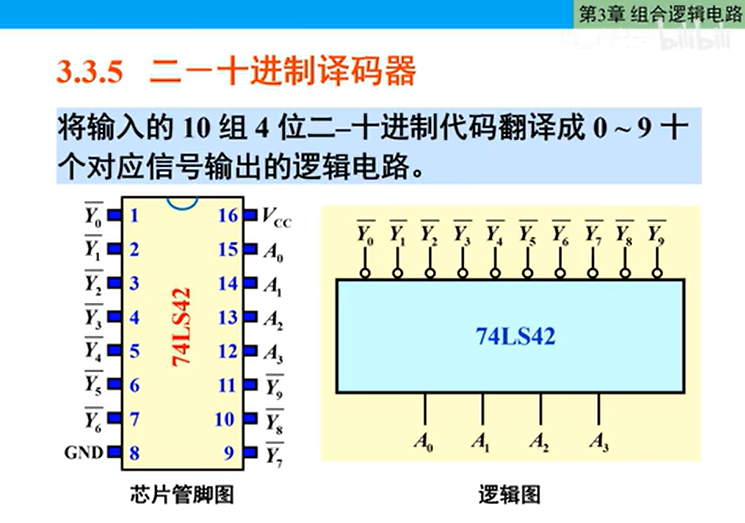

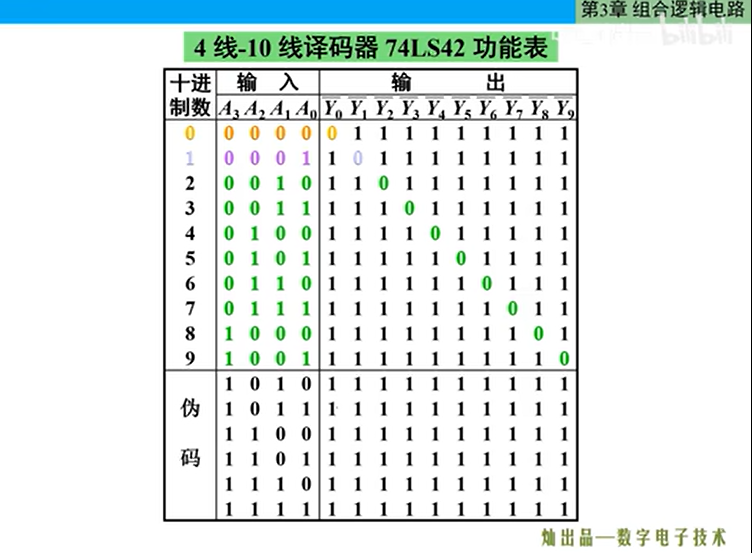

3.3.5 二-十进制译码器

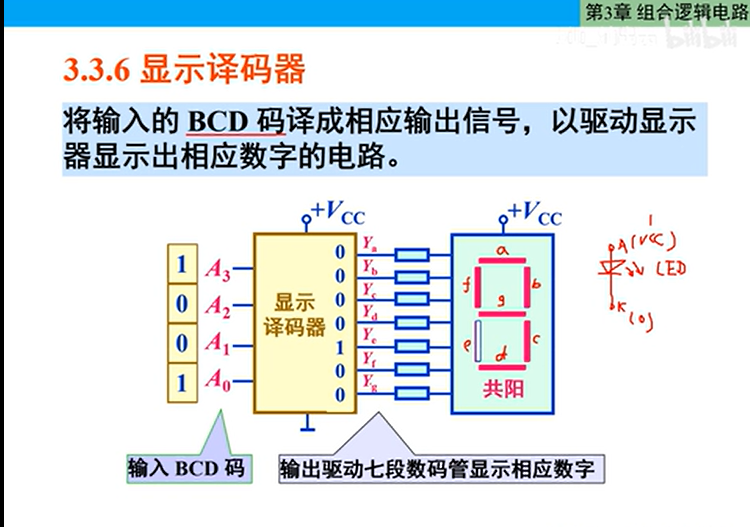

3.3.6 显示译码器

将输入的BCD码译成相应的输出信号,以驱动显示器显示相应数字的电路

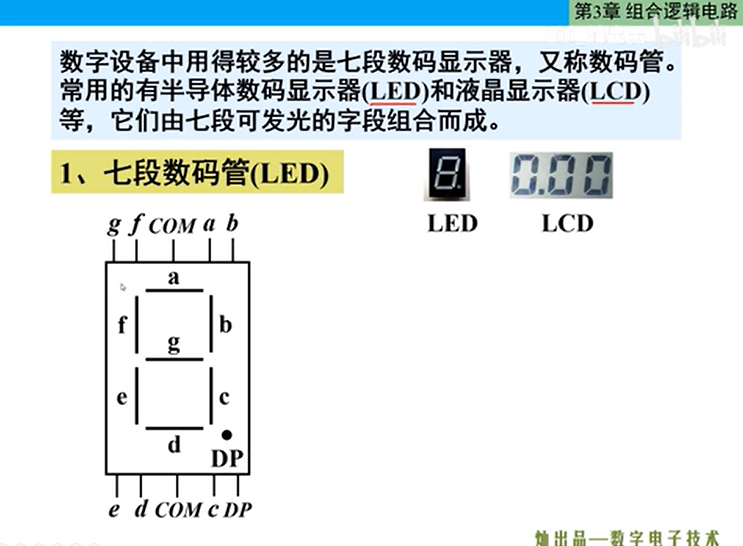

常用的是七段数码显示器

1,七段数码管(LED)

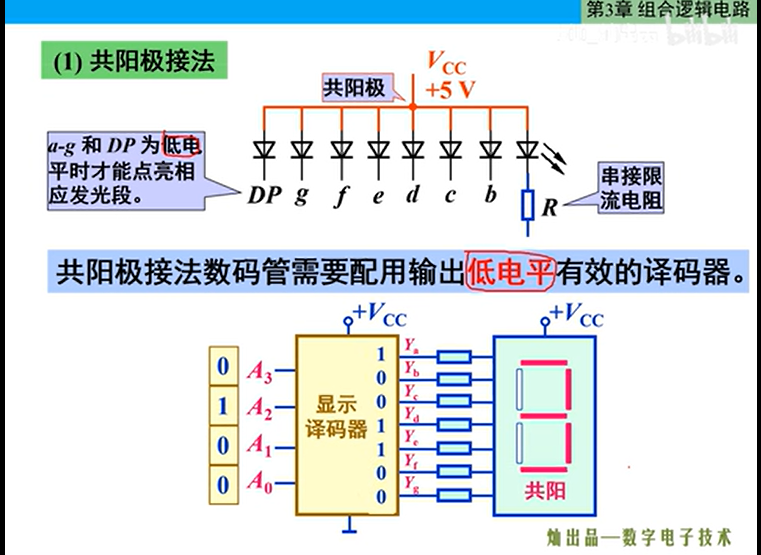

(1)共阳极接法

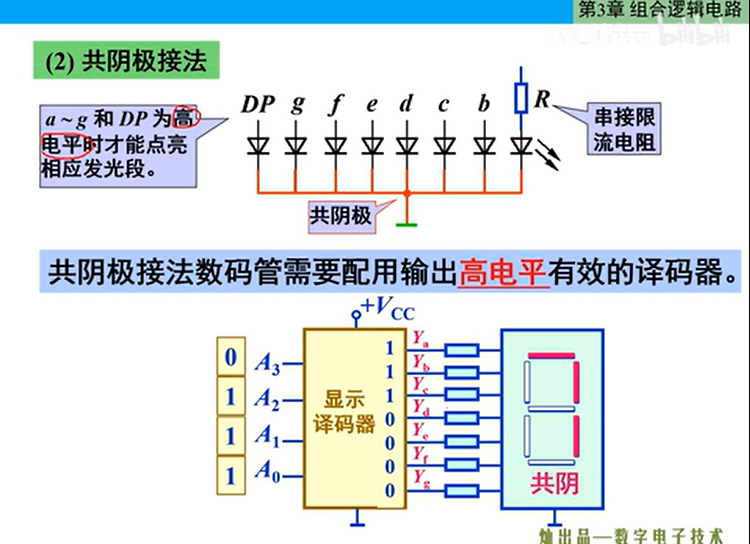

(2)共阴极接法

2,集成译码器

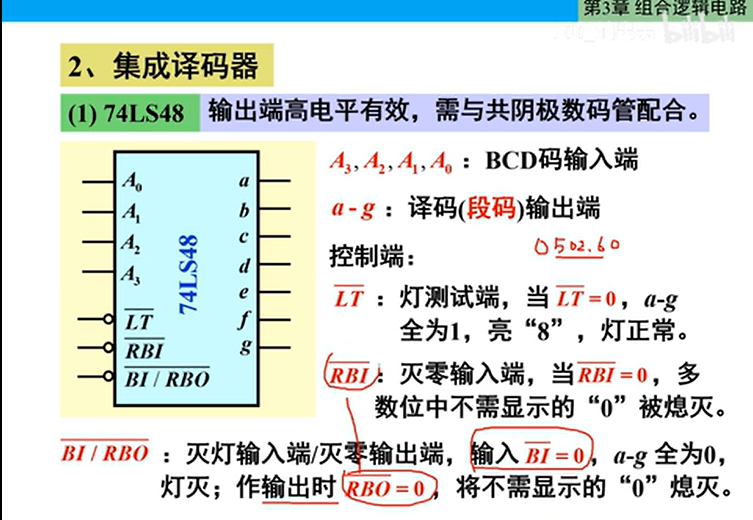

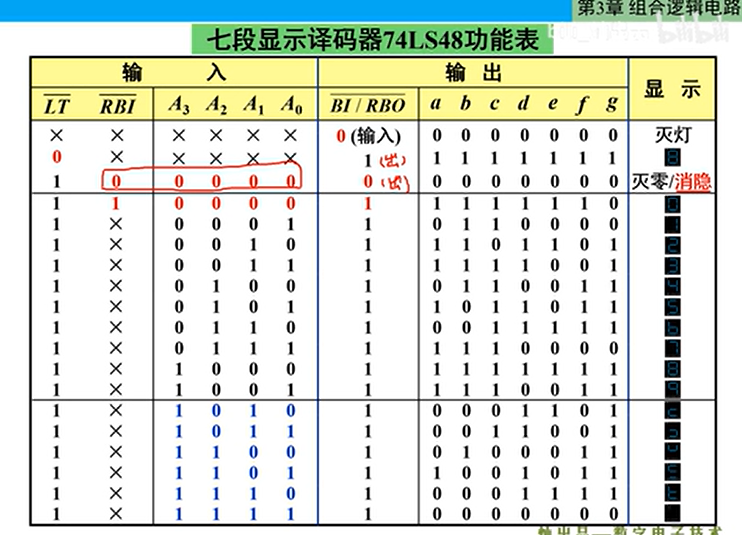

(1)74LS48

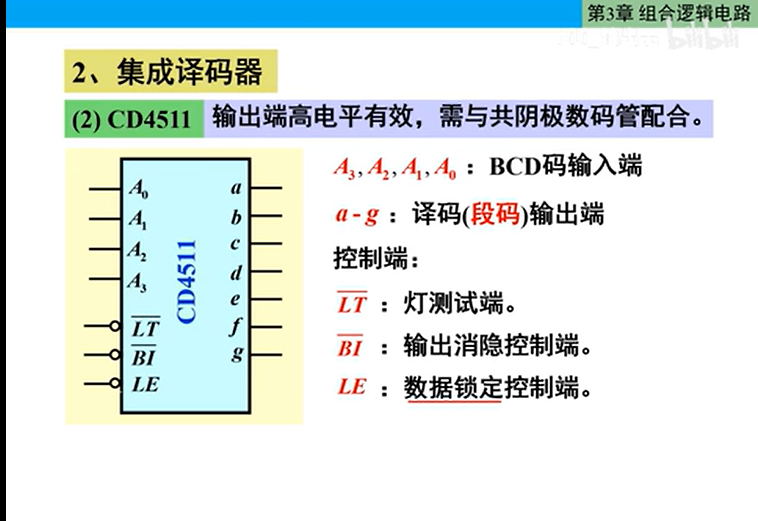

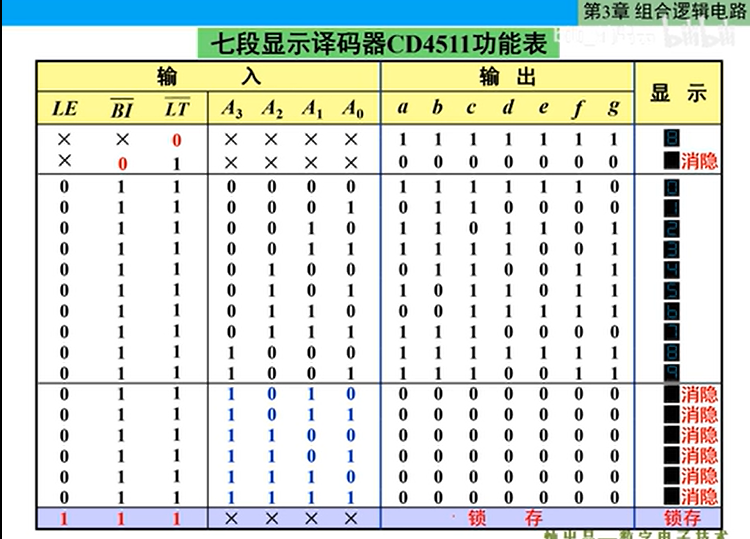

(2)CD4511

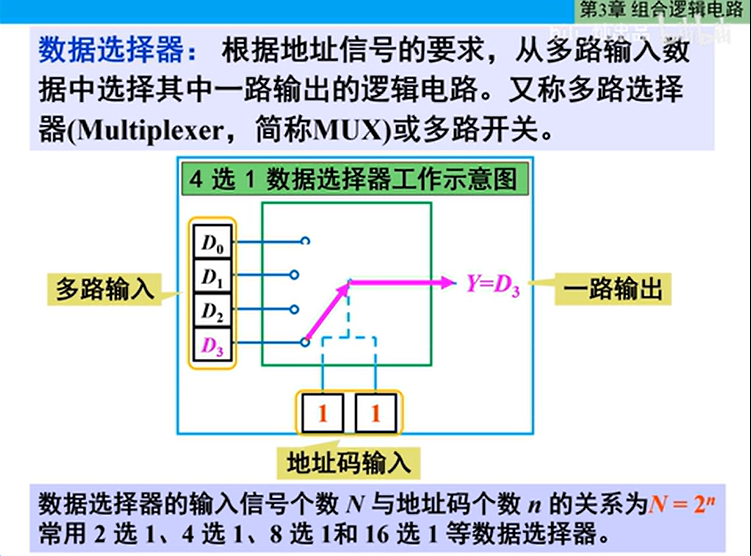

3.4 数据选择器和分配器

数据选择器:

3.4.1 数据选择器

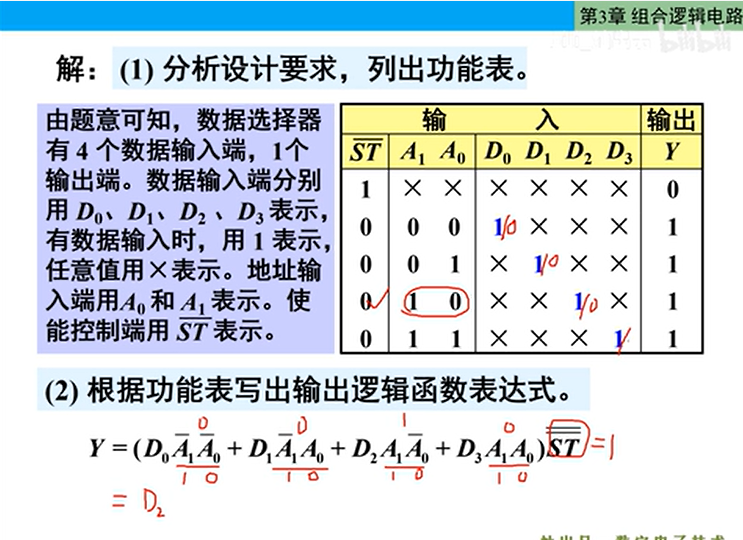

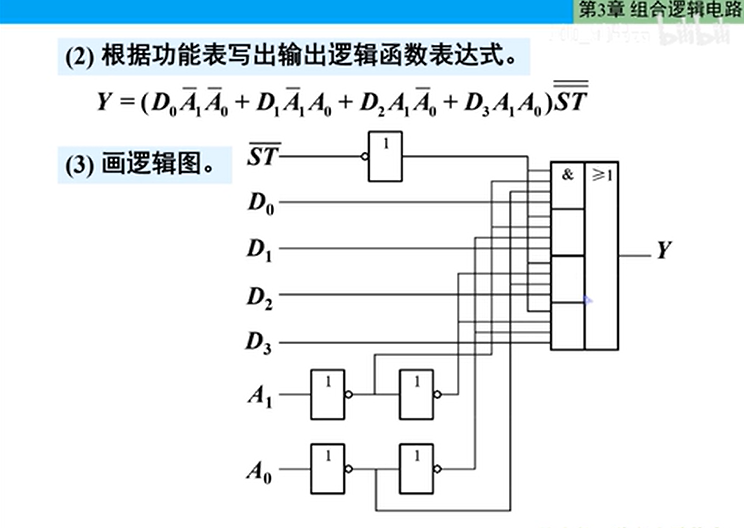

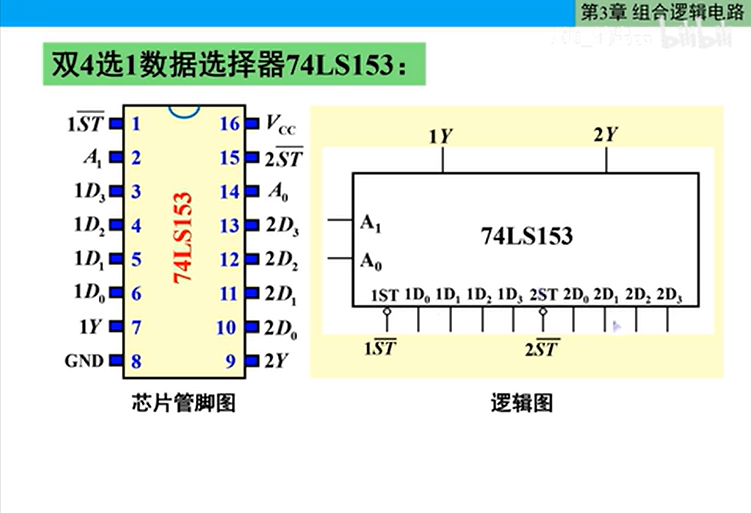

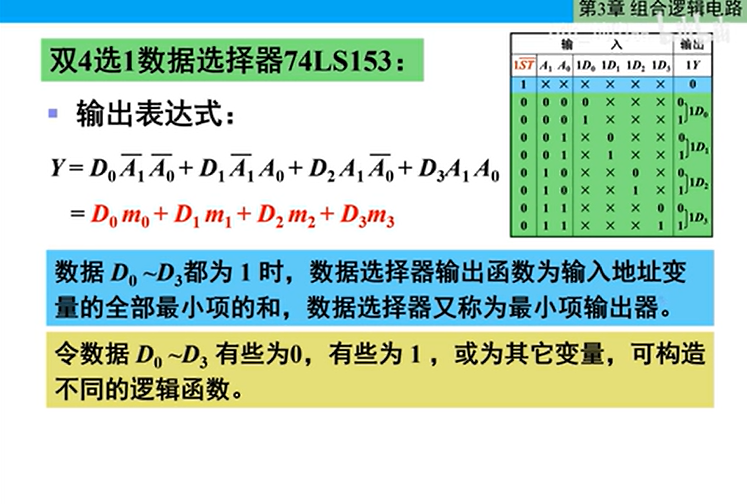

1,四选一数据选择器

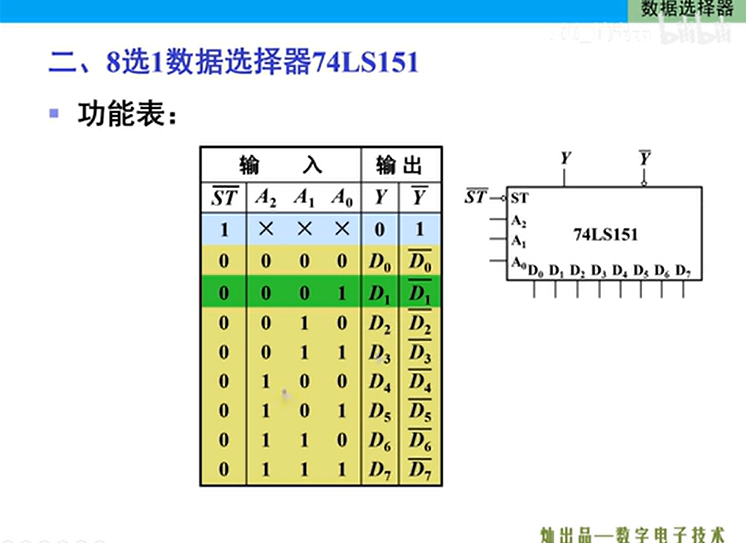

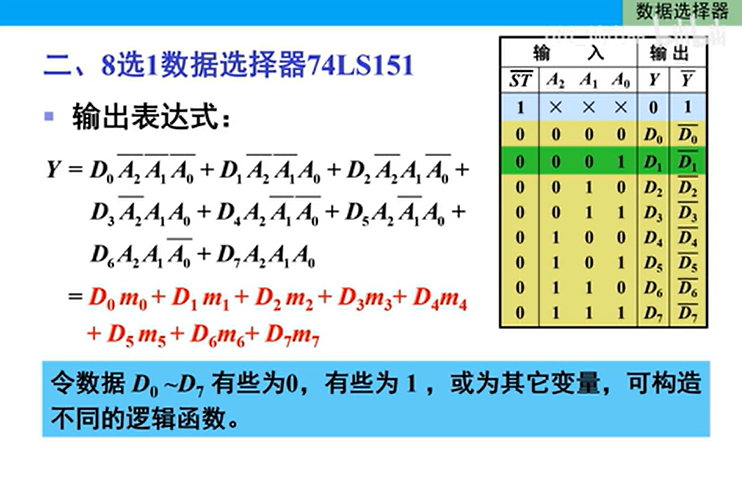

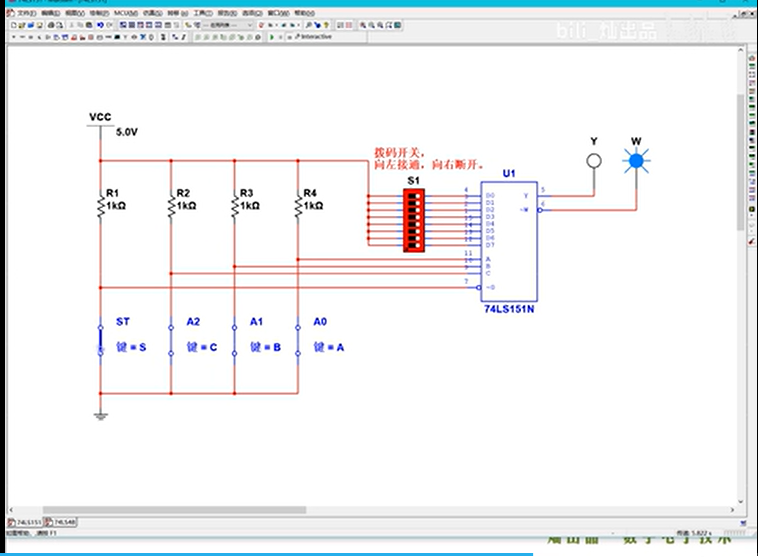

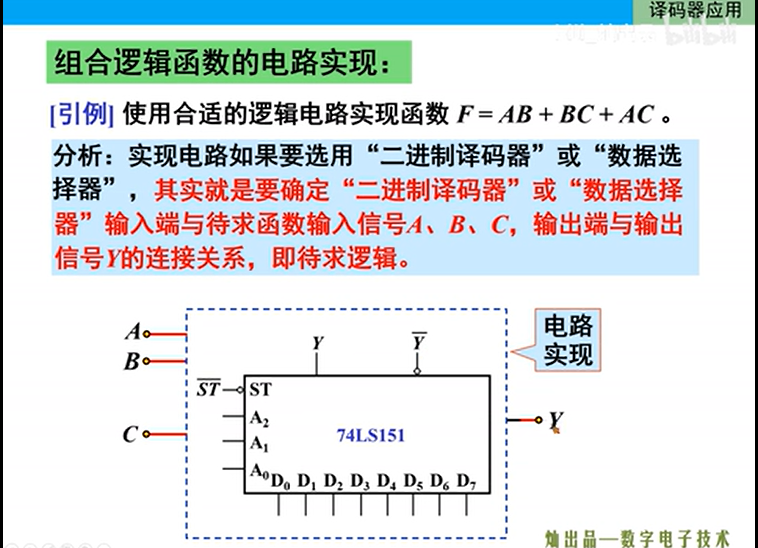

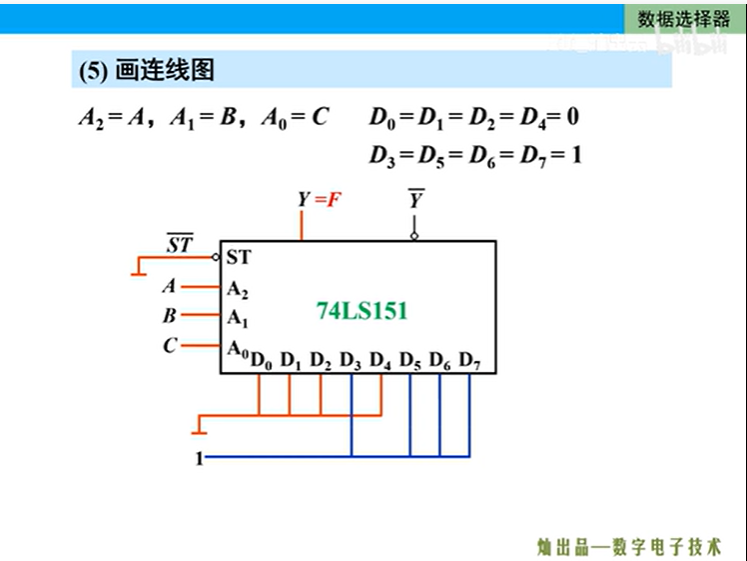

二,八选一数据选择器74LS151

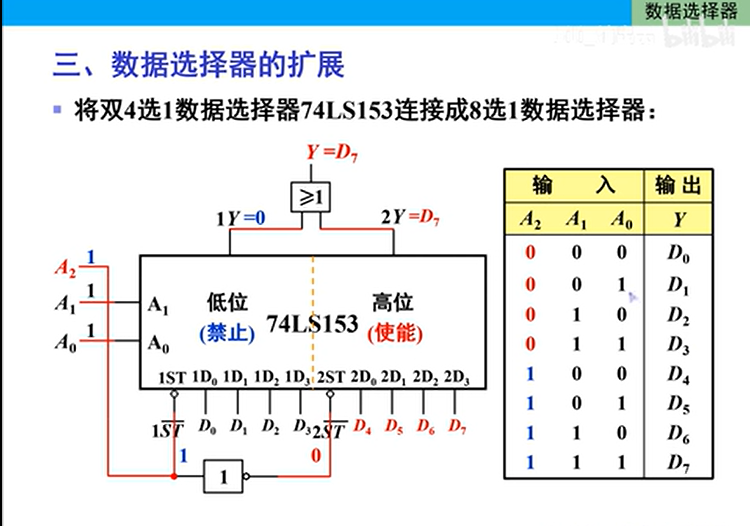

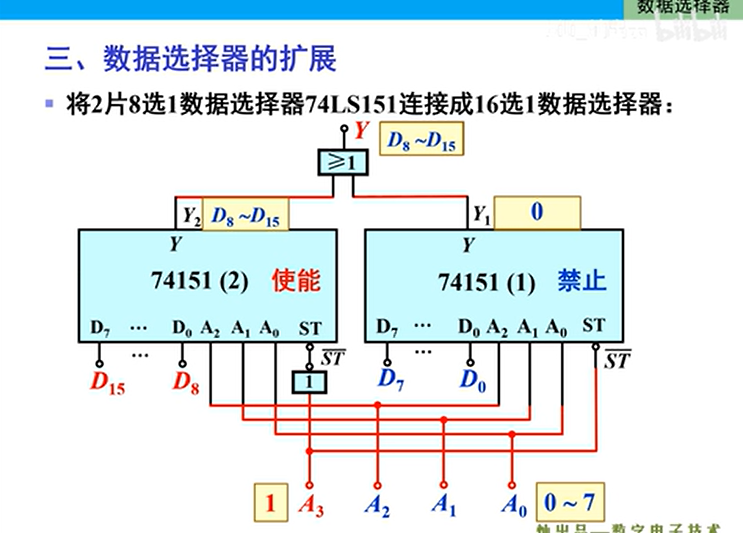

三,数据选择器的扩展

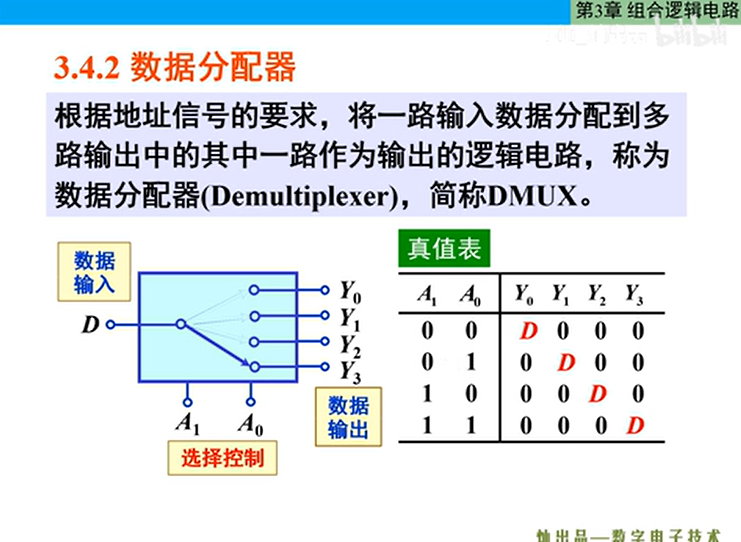

3.4.2 数据分配器

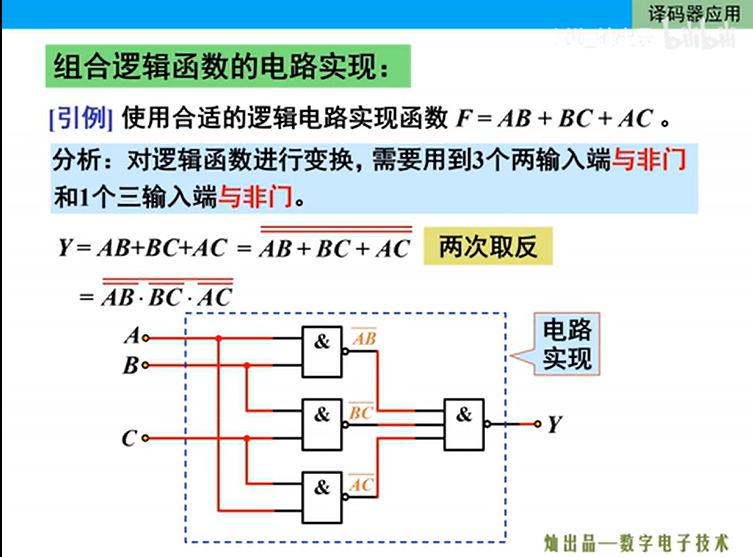

3.5 用中规模集成电路实现逻辑函数

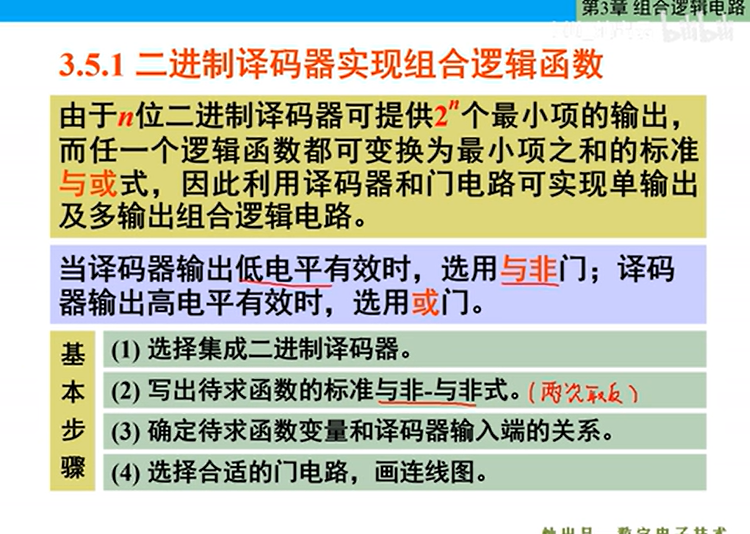

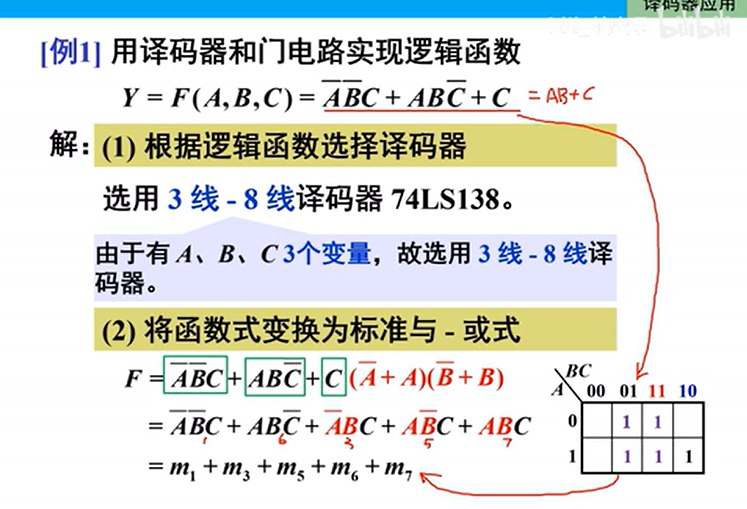

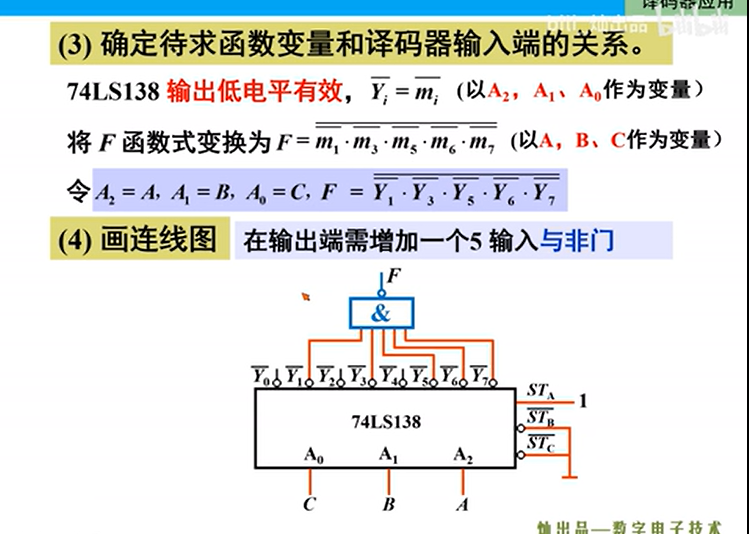

3.5.1 二进制译码器实现组合逻辑函数

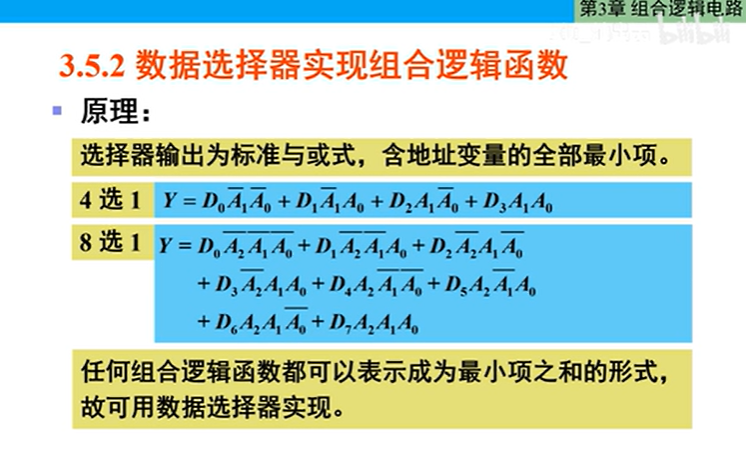

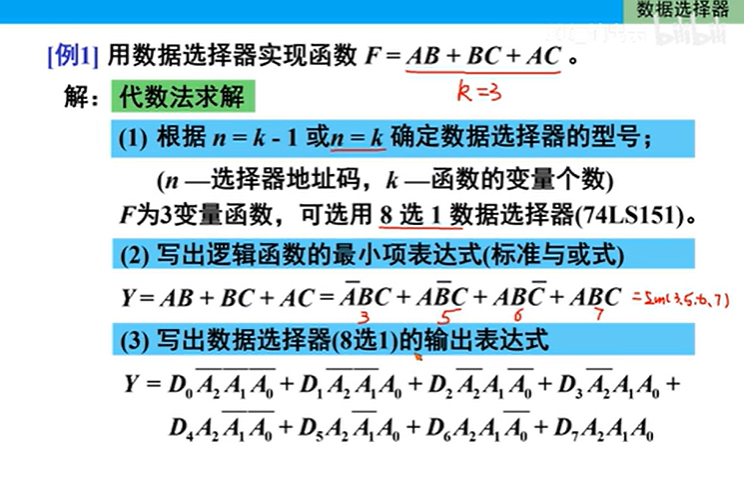

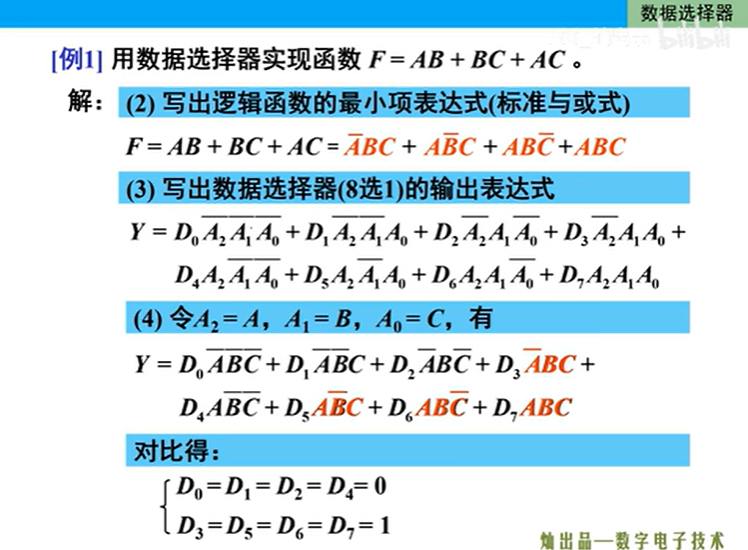

3.5.2 数据选择器实现组合逻辑函数

步骤:

1,根据n=k-1或n=k确定数据选择器型号

2,写出函数的标准与或式和选择器输出信号表达式

3,对照比较,确定选择器各个输入变量的表达式

4,根据采用的数据选择器和求出的表达式画出连线图

1,公式法

2,图形法

标签:第三章,组合,二进制,译码器,逻辑电路,3.3,选择器 From: https://www.cnblogs.com/tyjd/p/18599762