Synopsys Timing Constraints and Optimization User Guide学习笔记

一、综合时序简介

目录静态时序分析Static Timing Analysis

静态时序分析是一种通过在worst-case下检查所有路径时序违例来验证设计时序的方法,其考虑的时通过每个逻辑元件的最差可能延迟,而非逻辑操作。

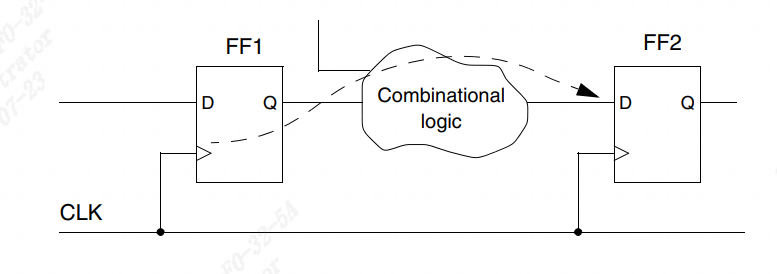

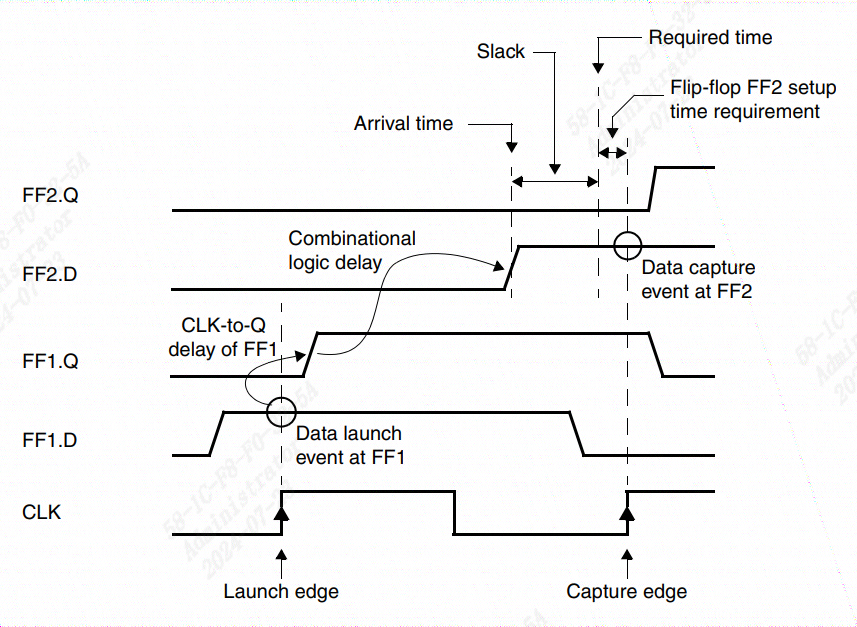

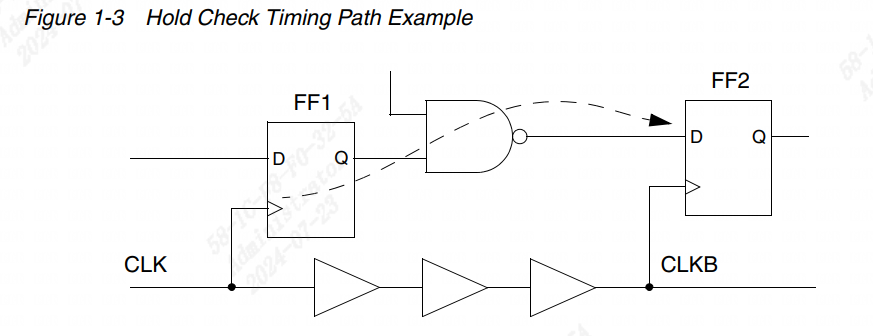

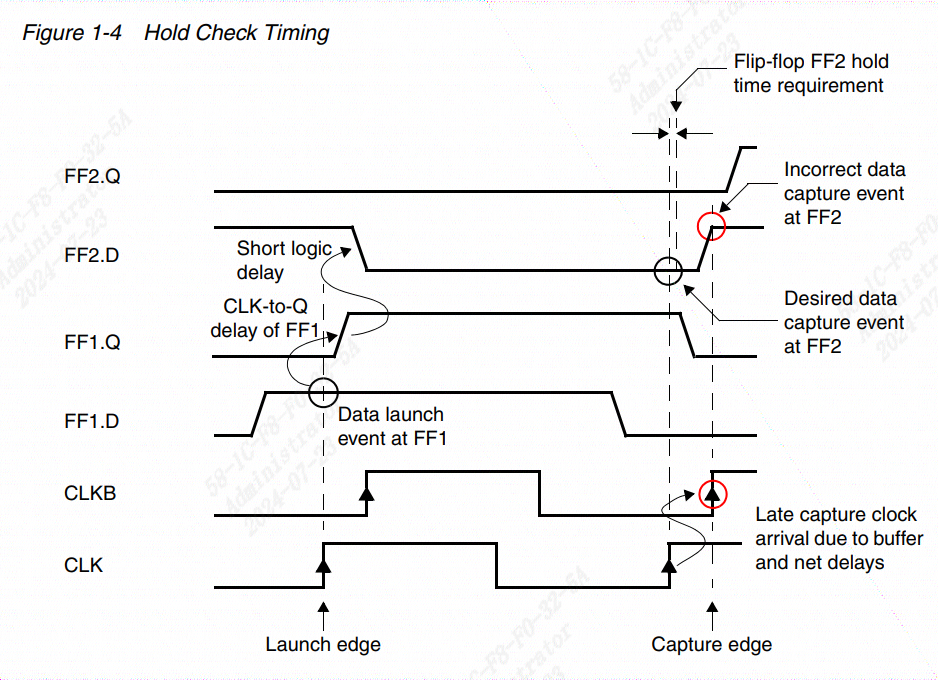

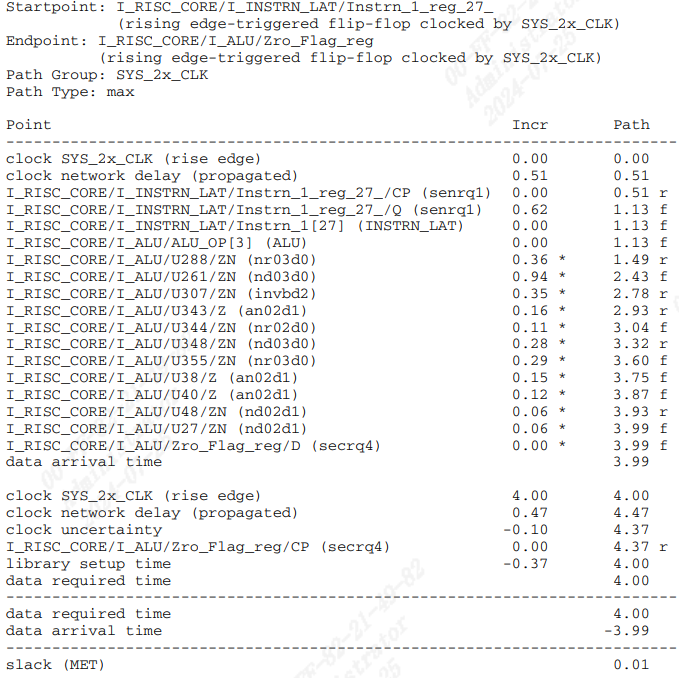

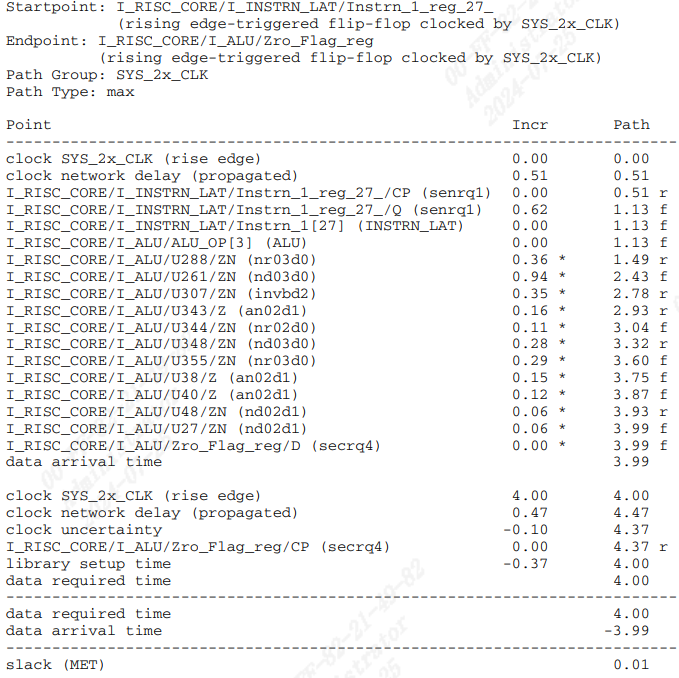

图2显示了图1电路的时序路径。建立时间的检查是最常见的,要求时间required time减去到达时间arrival time的Slack需要为正。另外还有保持时间的检查,需要保证在下一个时钟来临前,数据保持足够的时间。保持时间违例通常发生在组合逻辑非常短,而发射端到捕获端的时钟延迟非常长的情况下。下面就是一个例子

在这个电路中,组合逻辑只有一个与非门,但是 发射端到捕获端的时钟经过了3个buffer,并且甚至可能会因为过长的布线而导致较大的RC延迟。因此捕获CLKB到FF2的时间延迟要远大于发射CLK到FF1的时间延迟。

从上面的时序图可以看到,setup时间很容易满足,但是FF2更新的时间早于CLKB的捕获时间,因此不满足hold时间。修复办法是缩短时钟延迟或增加数据延迟。

默认的话,综合实现工具不会去修复hold违例,只着重修复setup违例。若想让工具修复hold违例,可使用set_fix_hold 命令,该命令会将fix_hold属性作用到特定时钟来修复hold违例。

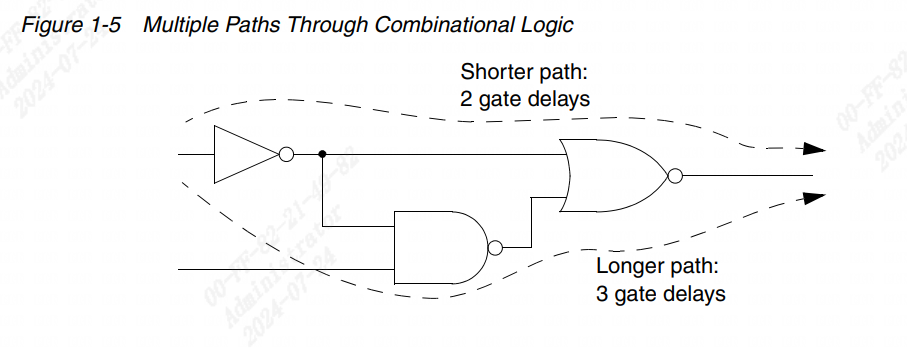

不同类型时序检查考虑不同的最差情况。如对于setup,考虑最长最慢的组合逻辑数据延迟和最早的捕获边沿,hold相反。如图1-5,对于同一块组合逻辑,setup考虑下面的3个门延迟,而hold考虑上面的2个门延迟。

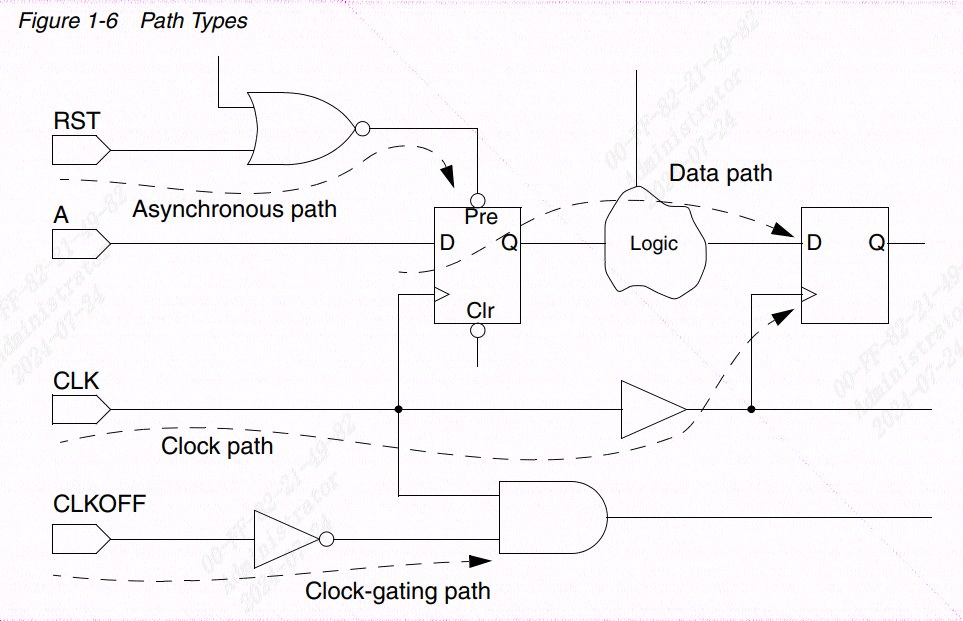

工具检查时序时,有以下几种类型的路径,图1-6:

- 时钟路径(对于setup/hold检查,考虑的路径从时钟输入端口或cell引脚开始,经过buffer或反相器,到达时序元件的时钟端。)

- 门控时钟路径(对于setup/hold检查,考虑从输入端口到门控时钟元件。)

- 异步路径(对于recovery/removal检查,考虑从输入端口到时序元件的异步复位置位引脚。)

- 数据到数据检查(使用

set_data_check命令指定的一种自定义时序检查,指定了数据信号之间的建立和保持时间。)

工具可以对时序元件输入端的异步复位置位检查,恢复时间recovery检查的是时钟边沿到达前异步控制信号是否有足够时间,类似setup time。去除时间removal检查的是在时钟有效沿来临之后复位信号还需要保持的时间。通过设置enable_recovery_removal_arcs命令使检查生效。

时钟门控检查是一种对时钟门控单元的控制输入的建立时间和保持时间的检查。这种类型的检查可检测削波时钟边沿或杂散时钟脉冲的出现。用于指定时钟门控检查的命令是set_clock_gating_check。

时序路径Timing Paths

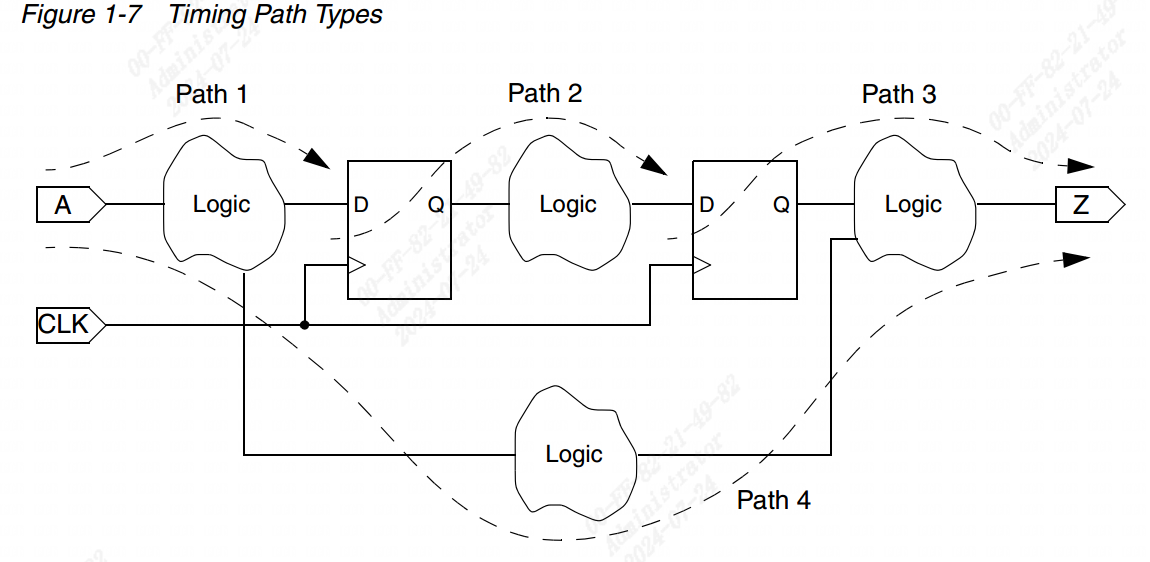

时序路径都有一个起点和终点。路径的起点是时序元件的时钟引脚或设计的输入端口。有效时钟沿到达起点时会发射数据。由于外部源也可能会发射数据,因此输入端口也可以被视为起点。路径的终点是时序元件的的数据输入引脚或设计的输出端口。有效时钟沿到达捕获端的的时钟输入端时,会捕获数据。由于外部可能会捕获输出端口的数据,因此输出端口可以被视为终点。

如图1-7,每条路径都从数据发射端开始,通过一些组合逻辑,并在数据捕获端结束。

设计中的每条路径都有相关的时序裕量。裕量是一个时间值,可以是正、零或负。具有最差裕量的单一路径称为关键路径。

可以把路径分组。比如分成输入到寄存器,寄存器到寄存器,寄存器到输出这三组,因为他们需要不同种类的时序约束。默认情况下,设计使用的每个时钟只有一个路径组。

在DC/ICC/PT使用 report_timing可查看时序报告。默认情况下,报告的是setup最差的一条路径。

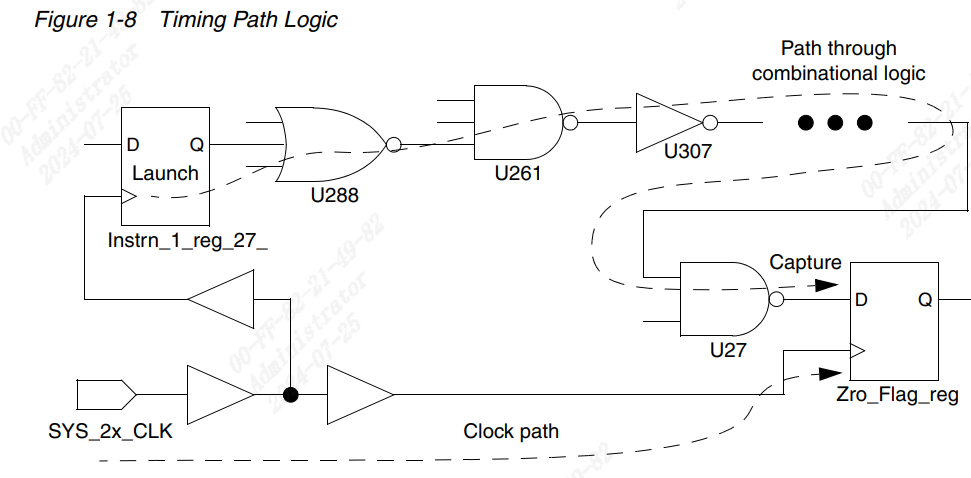

图1-8是一个例子。

其对应的报告如下,报告开头给出路径起点、路径终点、路径组名、路径类型。其中,路径类型max表示最大延迟或setup检查,min代表最小延迟或hold检查。

Incr列的星号(*)表示SDF反标的网络延迟值。Path列中的字母r和f表示路径中该点的信号转换方向,上升或下降。

该路径从发射时钟沿开始,到捕获设备的数据输入结束。表中显示的数据到达时间是从发射时钟沿的源到数据到达端点所经过的时间,其中考虑到了路径上最长的可能延迟。然后计算所需到达时间。表中显示的数据所需时间是路径端点处数据的最晚允许到达时间,其中考虑到标称捕获时钟边沿、时钟网络延迟、时钟不确定性、时钟路径上尽可能少的延迟,以及捕获端setup时间要求。所需时间可能根据CRPR( clock reconvergence pessimism removal )进行调整。

报告末尾显示的Slack就是所需时间减去到达时间,也就是说数据到达时间必须先于所需的时间才能符合时序要求。

时钟Clocks

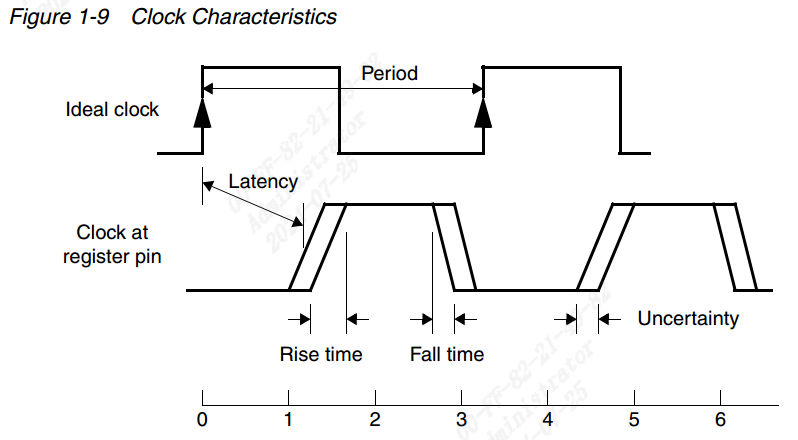

进行时序分析是,要指定时钟周期,并且可能需要转换时间、波形、延迟latency、不确定性uncertainty(频率偏差 jitter)、相对偏差relative skew(相位偏差)以及其它特性。如图1-9。

如果设计中使用了多个时钟,则必须指定这些时钟之间的时序关系,以便分析工具可以检查由一个时钟发射并由另一个时钟捕获的路径的时序。默认情况下,该工具假设在路径起点发射数据后,路径终点处下一个时钟沿应该捕获路径末端的数据。任何违反此基本假设的情况都必须指定为时序异常。时序异常的一些示例包括假路径、多周期路径以及显式最小延迟路径和最大延迟路径。

- A false path is a path that physically exists in the design but never propagates data from the startpoint to the endpoint due to the logic configuration, expected data sequence, or operating mode.

- A multicycle path is a path designed to take more than one clock cycle from launch to

capture. - A minimum-delay path or maximum-delay path is a path that must meet a delay constraint that you specify explicitly as a time value.

输入输出延迟 Input and Output Delays

再说

延迟计算 Delay Calculation

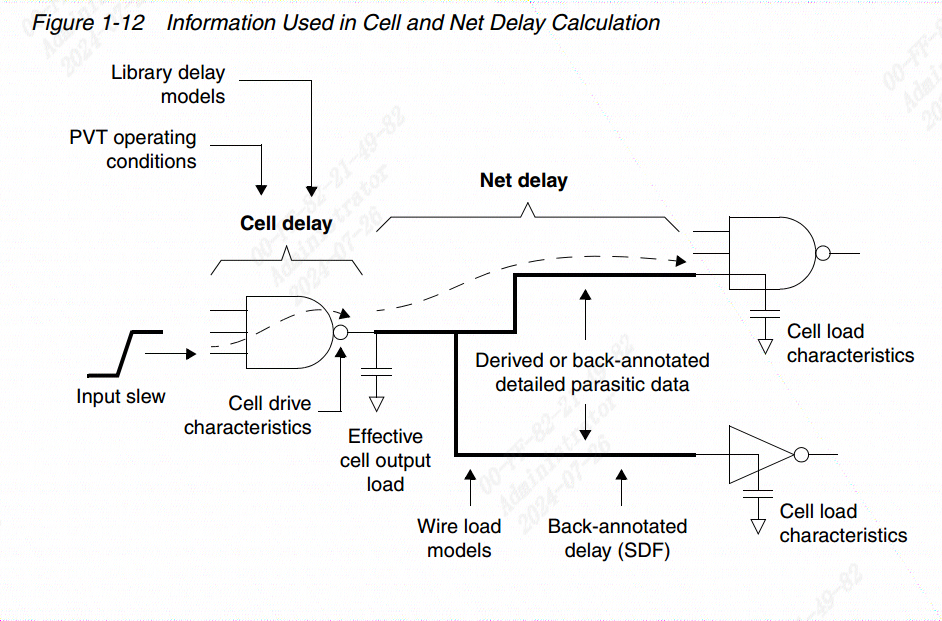

为了找到路径上的累积延迟,分析工具将路径上的各个单元延迟和互连延迟相加。单元延迟信息包含在每个单元的库描述中。为了计算互连延迟,分析工具需要知道驱动网络的驱动单元的特性、驱动网络接收器的负载特性、网络中导线的电阻和电容 (RC) 特性。互连 RC 特性取决于导线的物理配置和长度,因此只有在布局完成后才能准确确定这些特性。

对于在布局和布线之前执行的时序分析,分析工具必须估算导线延迟。最简单的估算方法是导线负载模型,它根据芯片尺寸和网络扇出获得导线总电容的粗略值。 较大的芯片尺寸和较大的扇出被认为会导致更长的导线和更大的电阻和电容。拓扑模式下的Design Compiler可以预测单元布局和导线长度,从而在不使用导线负载模型的情况下获得更准确的结果。

可以使用 report_delay_calculation 命令查看单元或网络的延迟计算的详细说明。

触发器和锁存器时序检查Flip-Flop and Latch Timing Checks

与触发器不同,电平敏感的锁存器,“借用”一个锁存器到下一个锁存器的时间可以放宽某些路径的时序要求。

再说

时序分析流程Timing Analysis in the Design Flow

时序分析在不同阶段侧重点不同。在DC中,时序重点驱动用于综合的库单元选择以及数据通路中组合逻辑间的寄存器分配,ICC中,时序驱动布局布线以最大限度减少关键路径延迟,在PT中,详尽的signoff时序分析是主要目的。

Synopsys Design Constraint (SDC) Commands

DC/ICC/PT共用一套命令语法SDC,write_sdc用于写入sdc命令脚本并指定当前设计应用该约束;而read_sdc用于读入约束文件并应用,类似source,但还可以用来检查命令合法性。SDC命令不仅可以在Synopsys工具间传递,还可应用到某些外部工具。

Library Timing Data

在时序分析中,门延迟、建立保持时间、clk to q 延迟、输出转换时间等时间参数都由库文件给出。工具需要读以下种类的库数据:

read_lib读取liberty(.lib)read_db或read_file读Synopsys database(.db)open_mw_lib读Milkyway database格式的LM(logic model)view

单元时序特性通常由Liberty NCX特性表征工具和HSPICE等电路模拟器结合来决定。Liberty NCX以.lib(人类可读)格式给出单元时序数据。一些时序分析工具可以用read_lib读取.lib文件。

.lib格式文件一般通过Library Compiler编译成.db格式文件。.db是二进制文件,相比.lib更小加载更快。时序工具通过read_db直接读取.db文件或借助link_library变量设置隐式读取。

每个时序参数,如输入到输出延迟或输出转换时间,都是由输入摆率和输出负载组成的函数。可以通过打开.lib或在工具中使用 report_lib -timing 命令查看,举例如下

prompt> report_lib -timing cb13fs120_max nd02d1

...

Lookup Table Template:

Template_name

--------------------------------------------------------------------

del_1_5_7_w

VARIABLE_1: input_net_transition

VARIABLE_2: total_output_net_capacitance

INDEX_1: 0.0150 0.2500 0.6500 1.4000 3.0000

INDEX_2: 0.0000 0.0070 0.0140 0.0385 0.0805 0.1505 0.3500

...

DELAY: A2, ZN, prop, neg_unate, '', ( , ), ( , ), ( , );

cell_rise ( del_1_5_7_w ) :

VALUES : 0.0270 0.0480 0.0690 0.1400 0.2620 0.4650

1.0420 0.0680 0.0990 0.1230 0.1950 0.3160

0.5190 1.0970 0.1010 0.1510 0.1890 0.2870

0.4110 0.6140 1.1910 0.1380 0.2080 0.2630

0.4060 0.5790 0.7920 1.3670 0.1880 0.2860

0.3620 0.5660 0.8170 1.1270 1.7480

该表列出了输入转换时间和输出电容负载的各种组合下,从输入A2到输出ZN的上升延迟值。

可以通过 report_delay_calculation看到详细的延迟计算过程

prompt> report_delay_calculation -from I_RISC_CORE/I_ALU/U27/A2 \

-to I_RISC_CORE/I_ALU/U27/ZN

...

Rise Delay

cell delay = 0.0583731

Table is indexed by

(X) input_pin_transition = 0.103374

(Y) output_net_total_cap = 0.00451049

Relevant portion of lookup table:

(X) 0.0150 (X) 0.2500

(Y) 0.0000 (Z) 0.0270 (Z) 0.0680

(Y) 0.0070 (Z) 0.0480 (Z) 0.0990

Z = A + B*X + C*Y + D*X*Y

A = 0.0244 B = 0.1745

C = 2.9088 D = 6.0790

Z = 0.0583731

scaling result for operating conditions

multiplying by 1 gives 0.0583731

...

由于操作条件不同,库延迟随工艺角(PVT)而变化。有些库可扩展以支持分析工具通过使用定义的操作条件及对应延迟值的插值来得到准确的延迟值。

Design Compiler

DC将RTL转换成网表,主要步骤如下

- 读入RTL(Verilog、VHDL)

- 读入SDC格式的时序、面积和功耗约束

- 使用通用布尔门、优化逻辑生成设计逻辑,并使用目标库的特定门映射到网表

- 将门级网表写到.ddc格式文件中

相对于功耗和面积,满足时序约束的优先级更高。使用check_timing来检查时序,使用report_constraint 和report_timing来查看

理想时钟Ideal Clocking

逻辑综合阶段不需要时钟树综合,因为布局布线之前线长未知,并且clock skew对寄生互联差异非常敏感。所以默认情况下,DC使用理想时钟,这就意味着latency(从时钟源到寄存器时钟引脚)、uncertainty和transition time均为0。时钟网络下的单元和连接都被标记为dont_touch.理想时钟网络在综合阶段不会被优化和缓冲。

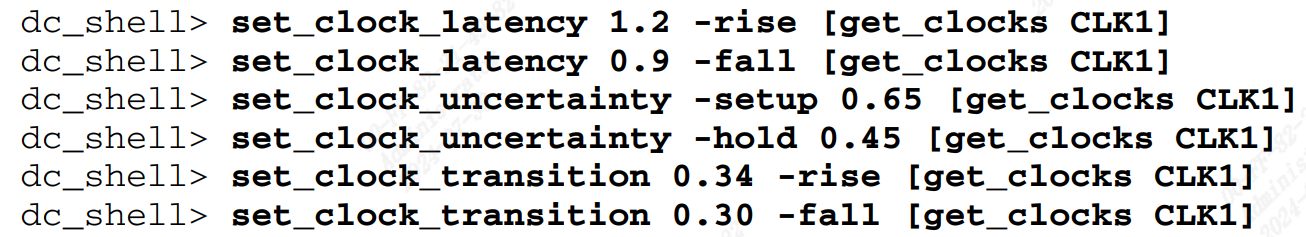

为了获取更准确的结果,可以为理想时钟添加非0的latency、uncertainty和transition time

高扇出除了时钟,还有复位和使能信号。这些也需要在布局阶段而非综合阶段加buffer tree。与理想时钟相似,也可以加非0参数以更贴近布局阶段。

线负载模型和拓扑技术Wire Load Models and Topographical Technology

线负载模型和拓扑技术是在DC中估计RC网络特性的两种技术。

- 线负载模型

线负载模型基于扇出把每个网络简化成一个电容和一个电阻。更大扇出意味着电容电阻更大。技术库提供线负载模型,而这些模型是基于同一工艺技术制造的相似尺寸相似设计中提取的数据。

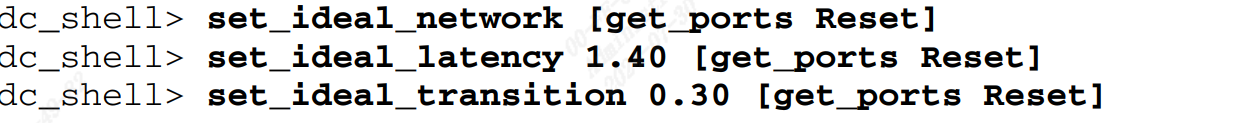

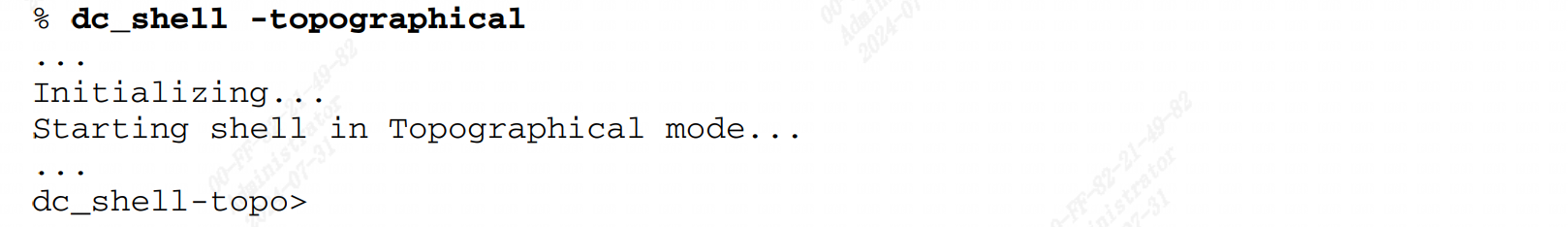

库一般针对不同设计尺寸有不同的线负载模型。一些库供应商会根据设计尺寸大小来命名线负载模型,比如“300KGates”、“600KGates”。当设计是分层的而且每个模块被划分到不同物理区域时,可以为每个模块设置较小的线负载模型,示例如下,

其中,set_wire_load_mode enclosed命令可以指定每个网络电容参数都是由包住该网络的最小子模块计算得到的。

有些库还支持使用 auto_wire_load_selection 来自动选择线负载模型。

- 拓扑技术

线负载模型只是基于统计而不是具体设计。对于超深亚微米设计中,线寄生参数对路径延迟影响增大,因此需要DC的拓扑技术来更精准估计。

拓扑模式下的DC,不需要线负载模型,而是通过Milkyway库来预测实际导线长度。

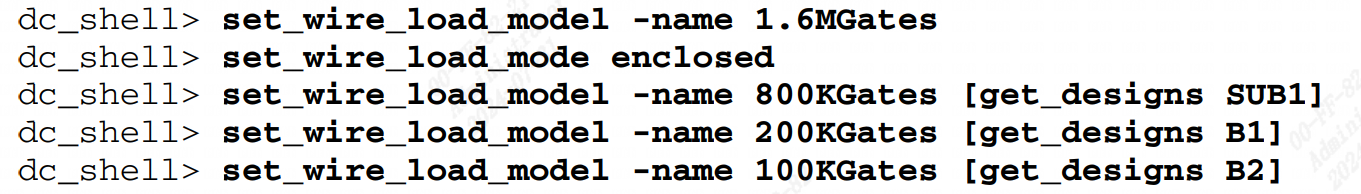

使用-topographical开启拓扑模式

Milkyway参考库包含综合网表的物理布局描述,包括标准单元、宏单元和pad cell。技术文件定义工艺金属层,物理设计规则,阻容单位等。TLUPlus包含超深亚微米RC寄生参数。

设计分层Design Partitioning

在原始设计使用良好分区时最优策略。但当RTL分区不理想时,可以在编译前对逻辑重新分组配置。compile_ultra可以自动重分区。

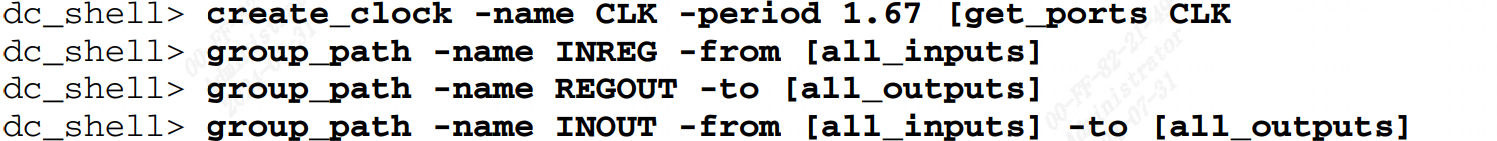

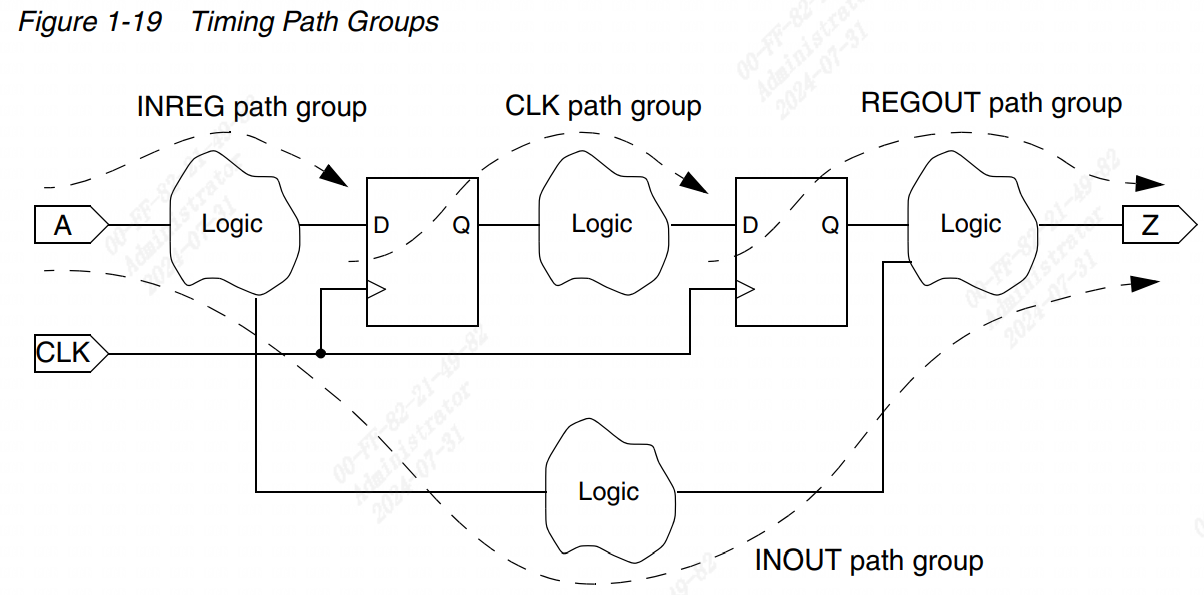

路径组Path Groups

时序路径的组叫做路径组(注意不同于上面一节提到的逻辑分组)。

可以通过时序路径分组来控制目标优化的重点。例如,如果不确定输入延迟要求,就可以吧输入到寄存器路径放到一个单独的组。这样,输入到寄存器路径组与其他路径分开优化,并且最差的输入到寄存器违例不会影响同一时钟下寄存器到寄存器路径的优化。

使用group_path进行分组,示例如下,

默认情况下,所有CLK驱动的都被划分到CLK路径组。但在这里例子中,输入到寄存器、寄存器到输出、输入到输出被划分成三条路径组。另外,寄存器到寄存器路径仍保留在原默认的CLK组,如图1-19所示

分组之后,使用report_timing会分别给出各个组的最差路径。

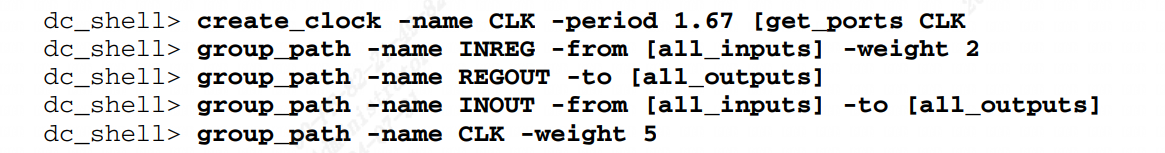

另外还可以对每条路径划分权重,默认权重为1,示例如下

可通过 report_path_group获取组路径信息。如果要去除某个路径组,用 remove_path_group ,去除的会隐式分配到默认路径组中。

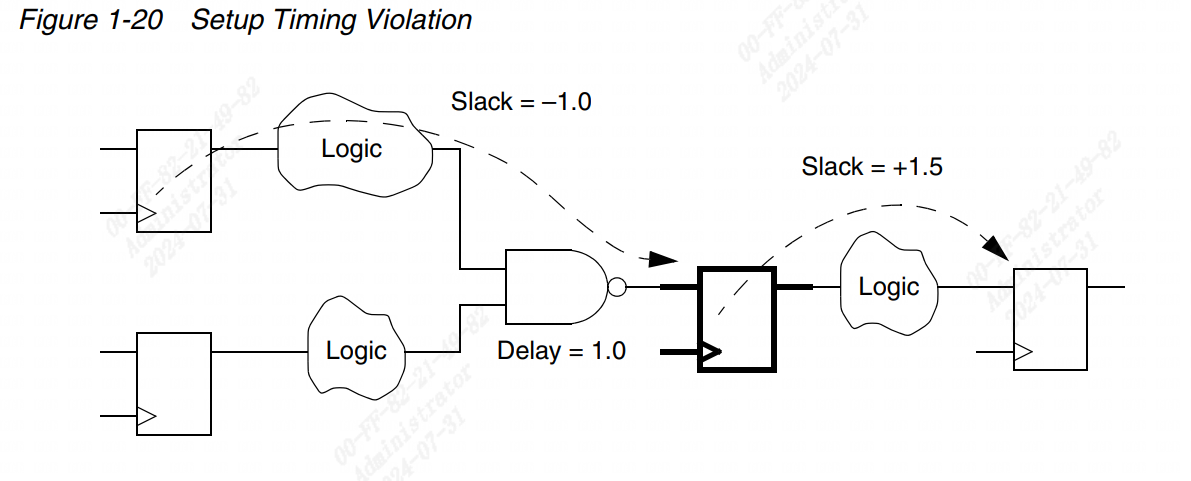

寄存器重定时优化Register Retiming Optimization

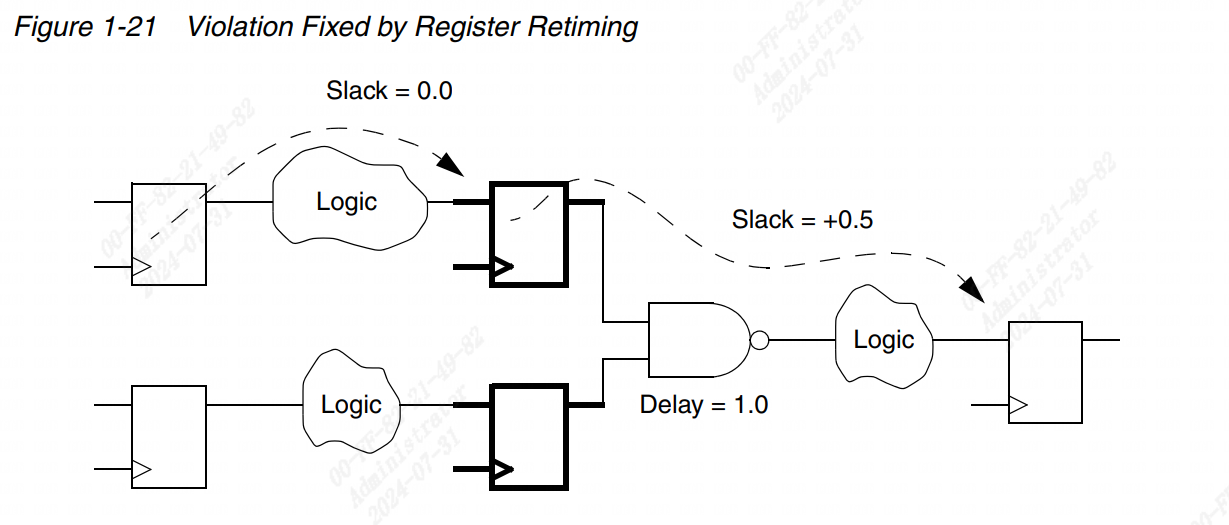

另一种满足时序要求的方法就是重定时优化,即通过重新安排寄存器在组合逻辑中的位置。如图1-20,左边的路径由于长的组合逻辑而有-1.0 slack,右边则+1.5 slack。

如图1-21,DC把与非门移到寄存器后面,代价是增加了一个寄存器。不过如果左边时序slack有余量的话,最左边两个寄存器也可减为一个,有点绕,其实就是刚才的反操作。

可通过以下命令开启重定时功能,compile_ultra -retime, balance_registers, optimize_registers, pipeline_design.