vivado仿真

vivado集成了HLS工具,可以直接使用C \ C++ \ systemC 语言对Xilinx的FPGA器件进行编程。

用户无需手动创建RTL,通过高层次综合生成HDL级的IP核,从而加速IP创建。

参考了下面的视频整理出的流程与步骤:

vivado视频教程:

第一讲:https://www.bilibili.com/video/BV1XU4y1M7nw?p=7&vd_source=da31a9aa66fbe4d6b904e621d9943c75

第三讲:https://www.bilibili.com/video/BV1XU4y1M7nw?p=9&vd_source=da31a9aa66fbe4d6b904e621d9943c75

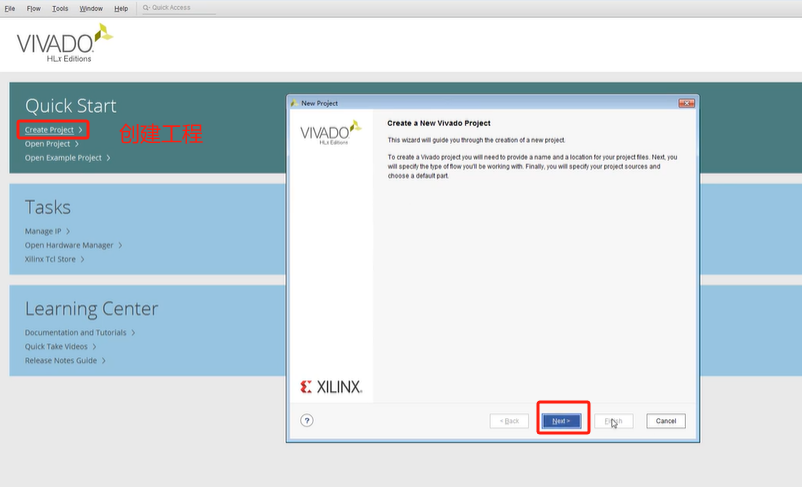

1.创建工程

vivado界面介绍:

第①步:创建文件夹:

注意:文件夹的名字中不能含有中文。

第②步:创建工程:

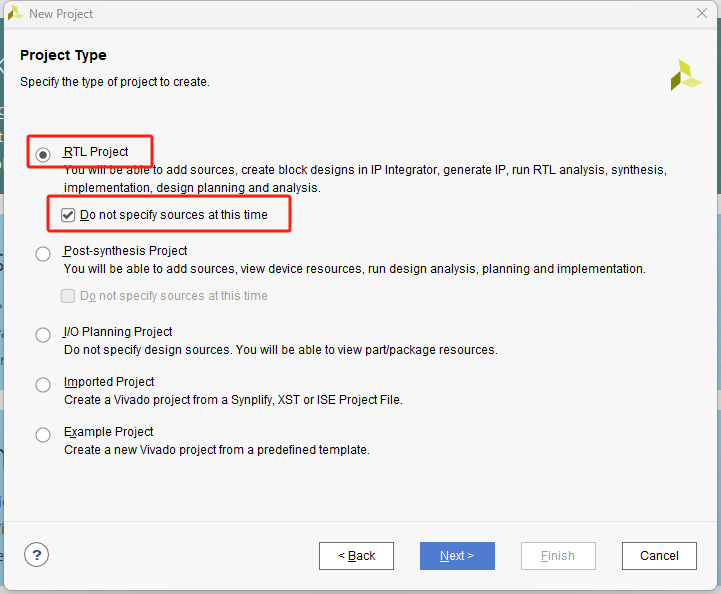

选项1:创建工程

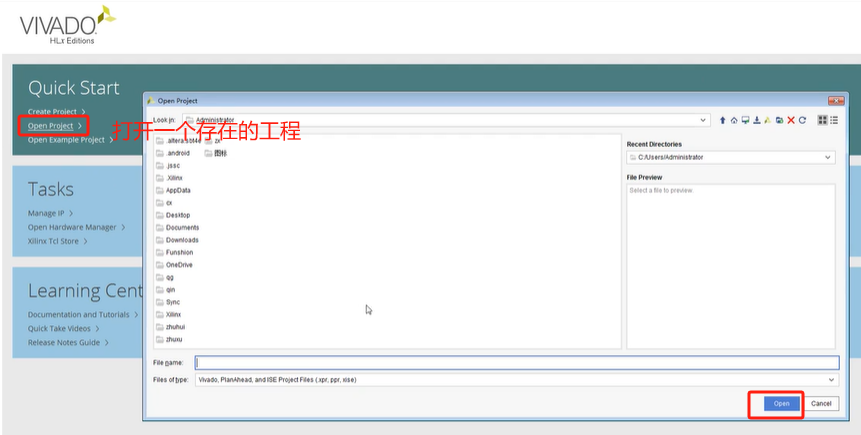

选项2:打开一个已经存在的工程

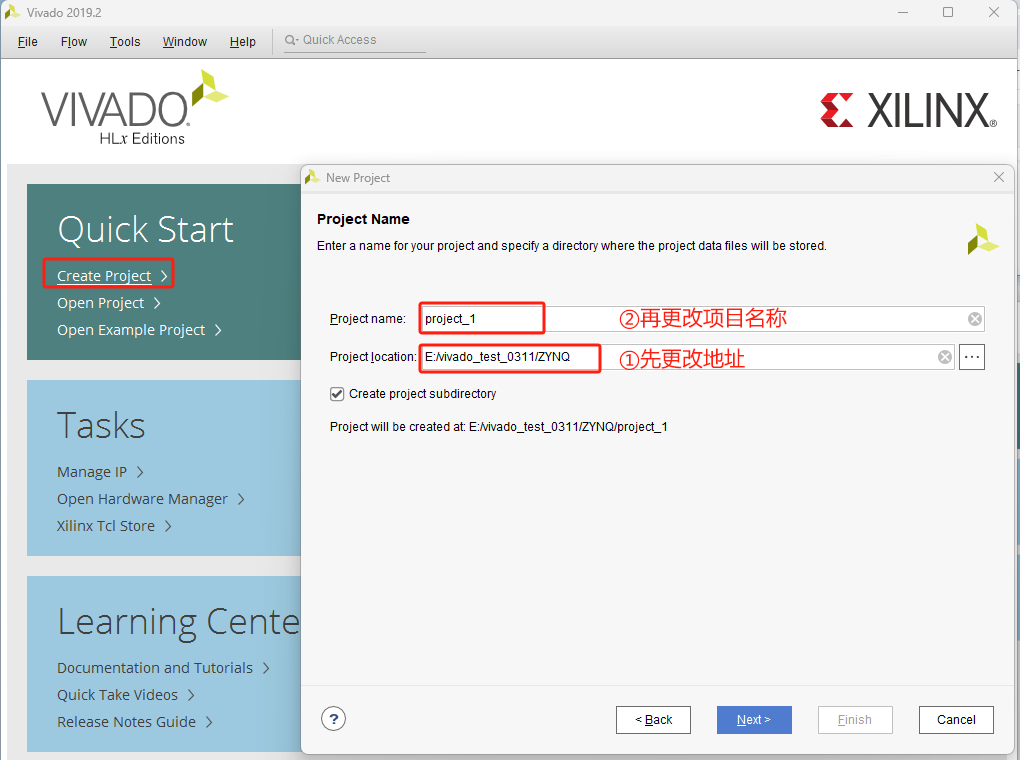

选择项目保存的地址,和项目保存的名称。

点击next

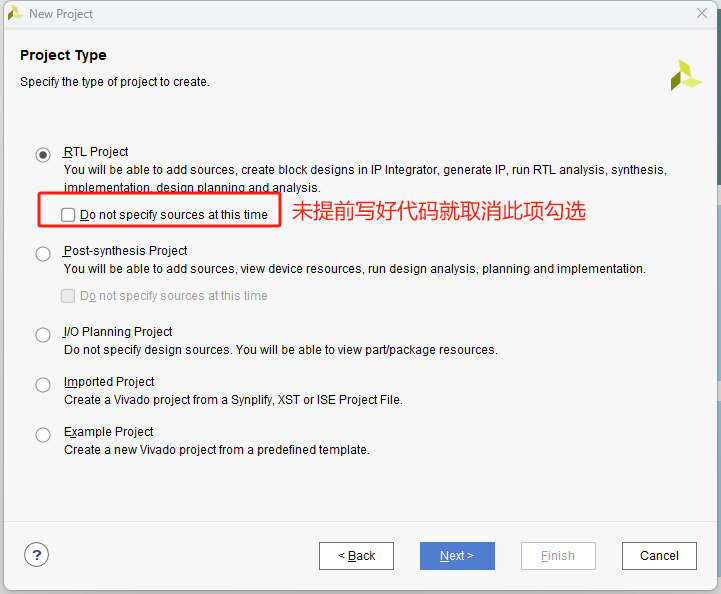

若未提前写好代码就取消此项勾选

如果提前写好代码,检查选项(一般默认为下面的选项)

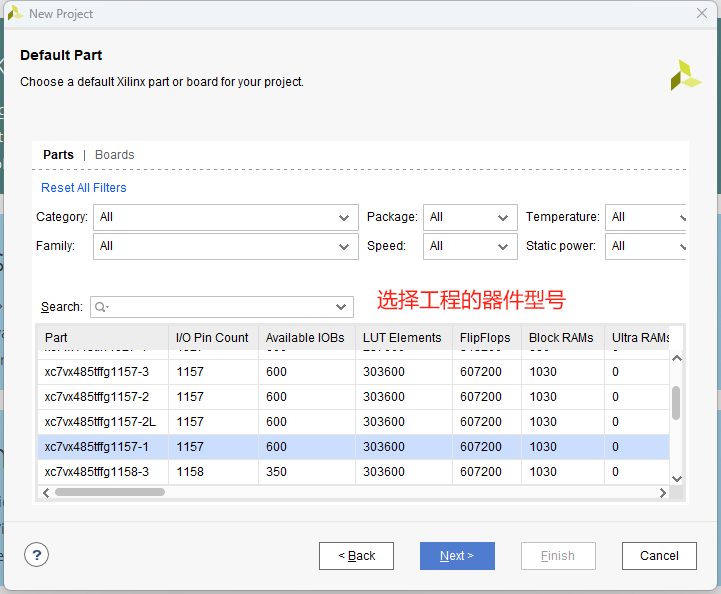

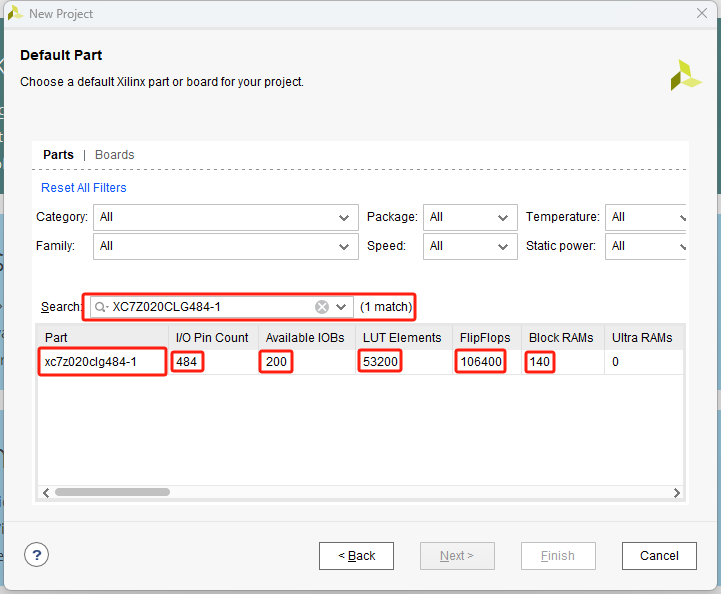

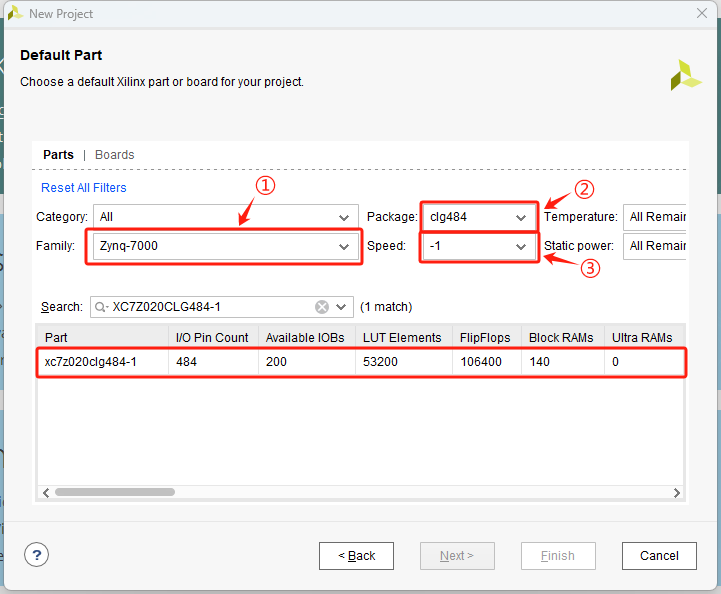

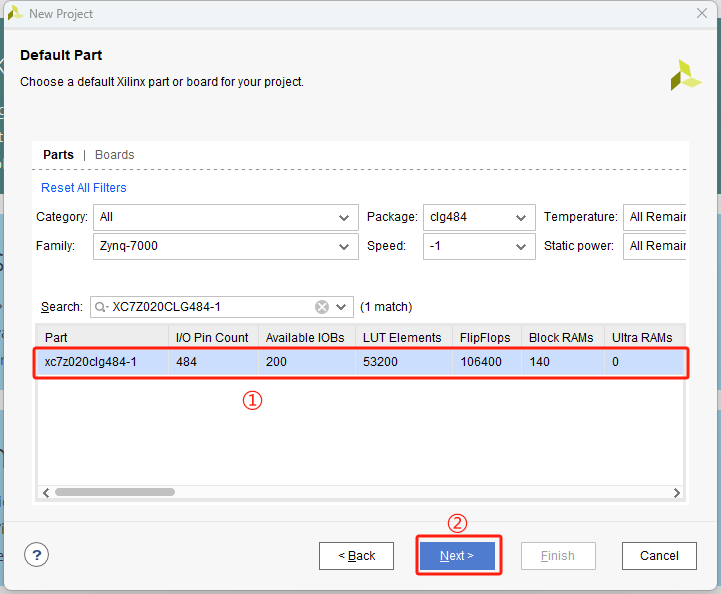

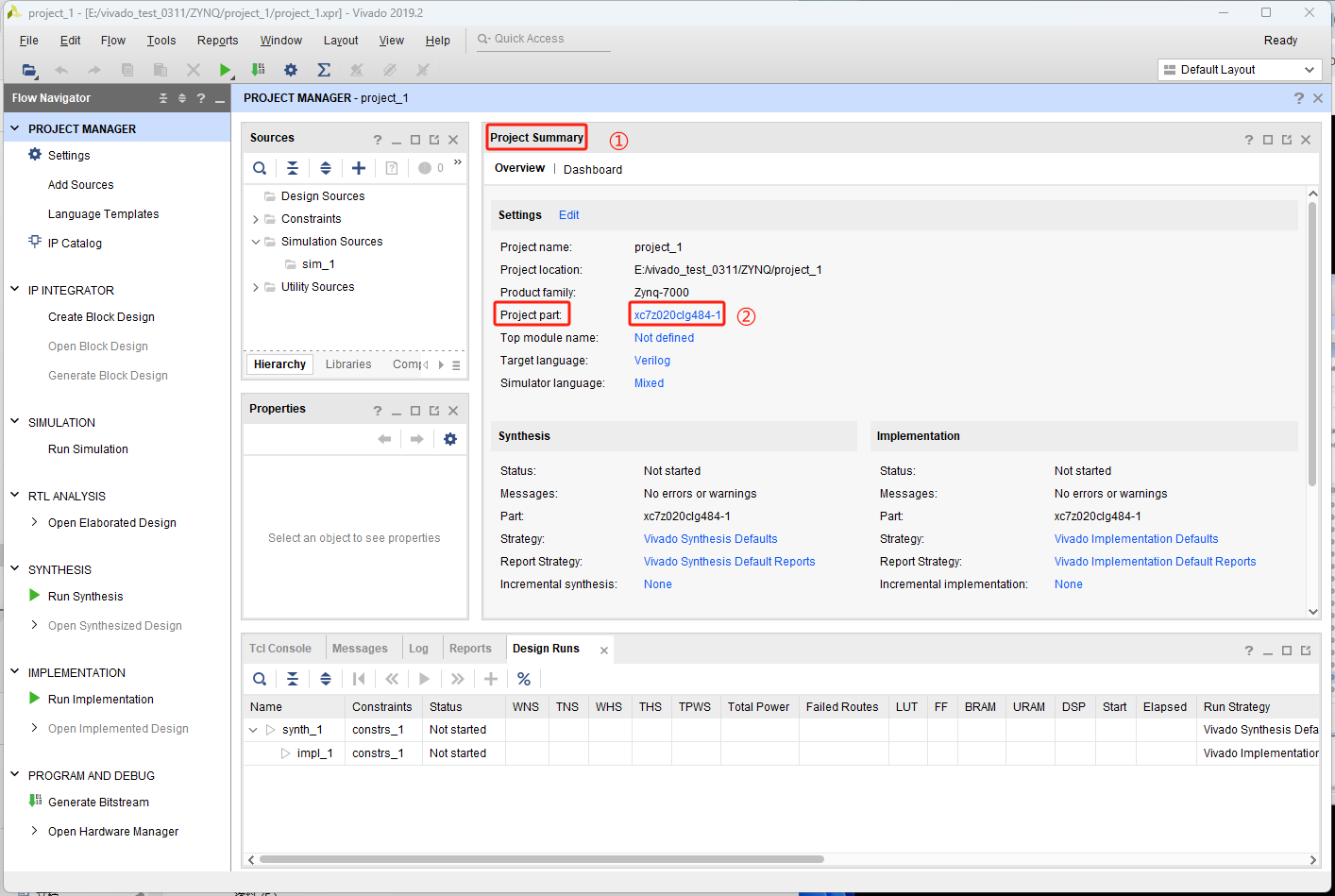

选择器件:

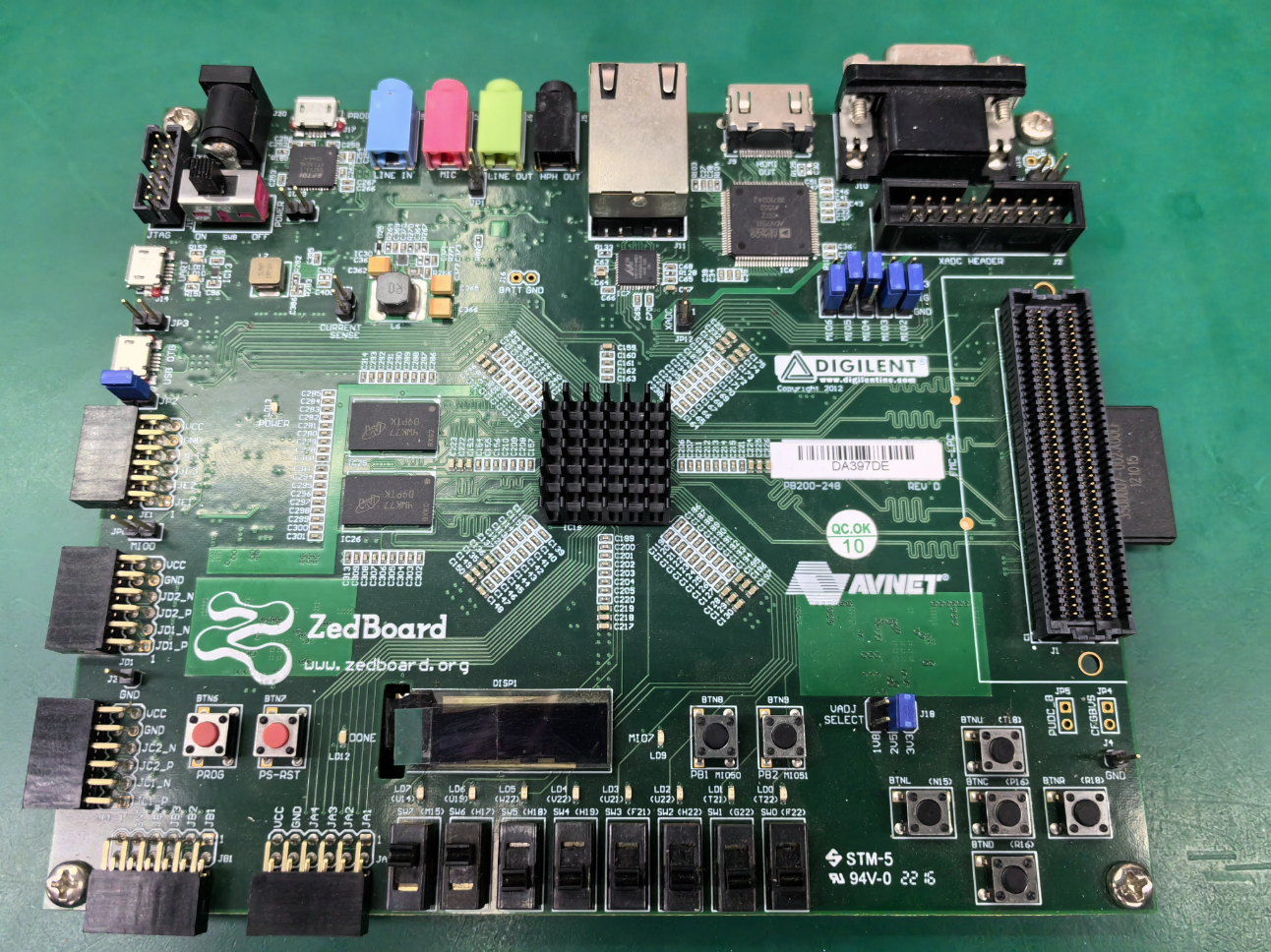

视频教程中的SOC型号是:XC7Z020-CLG400-1

而我用的zedboard的SOC型号:XC7Z020-CLG484-1

方法①直接输入:

可以直接在search里面输入型号。

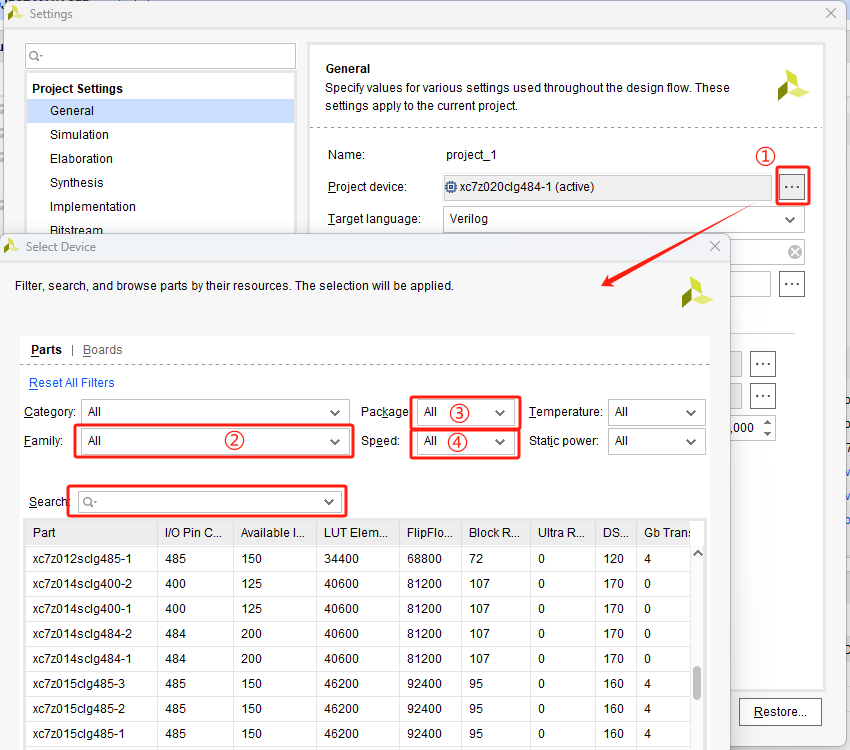

方法②按系列查找:

按照系列查找

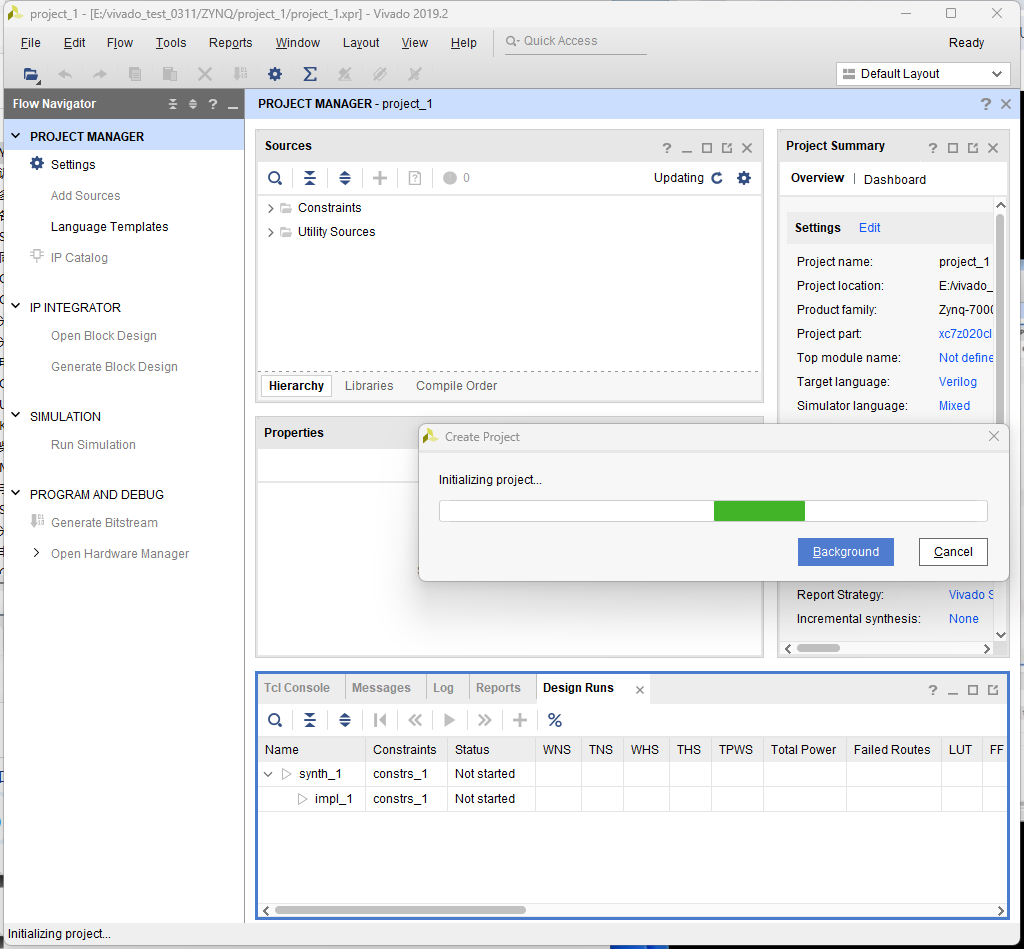

等待一会儿

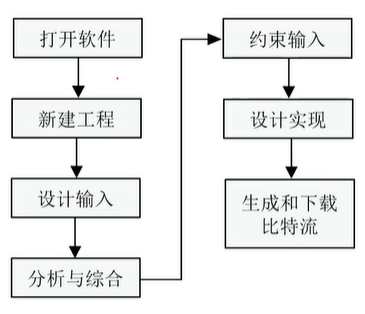

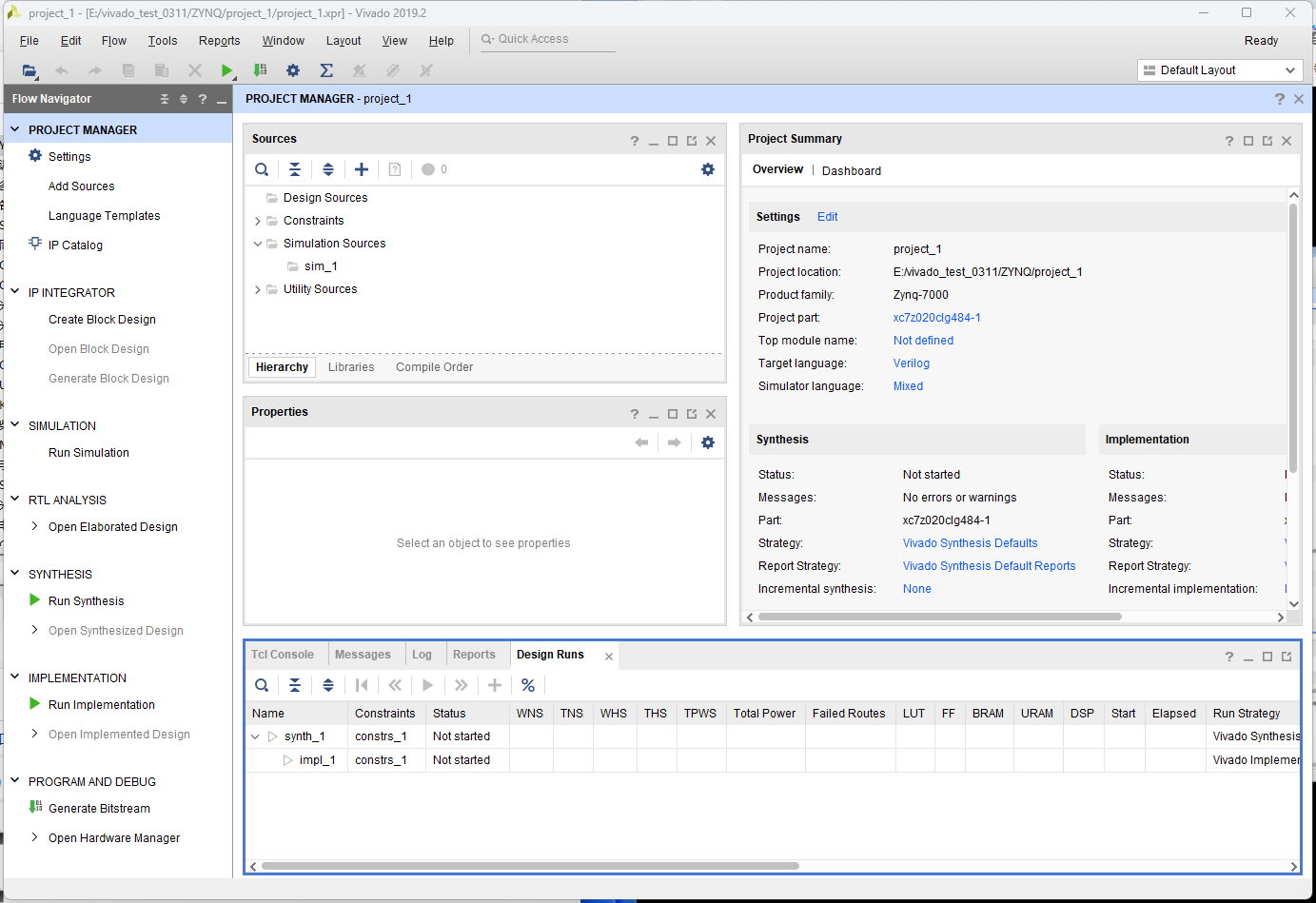

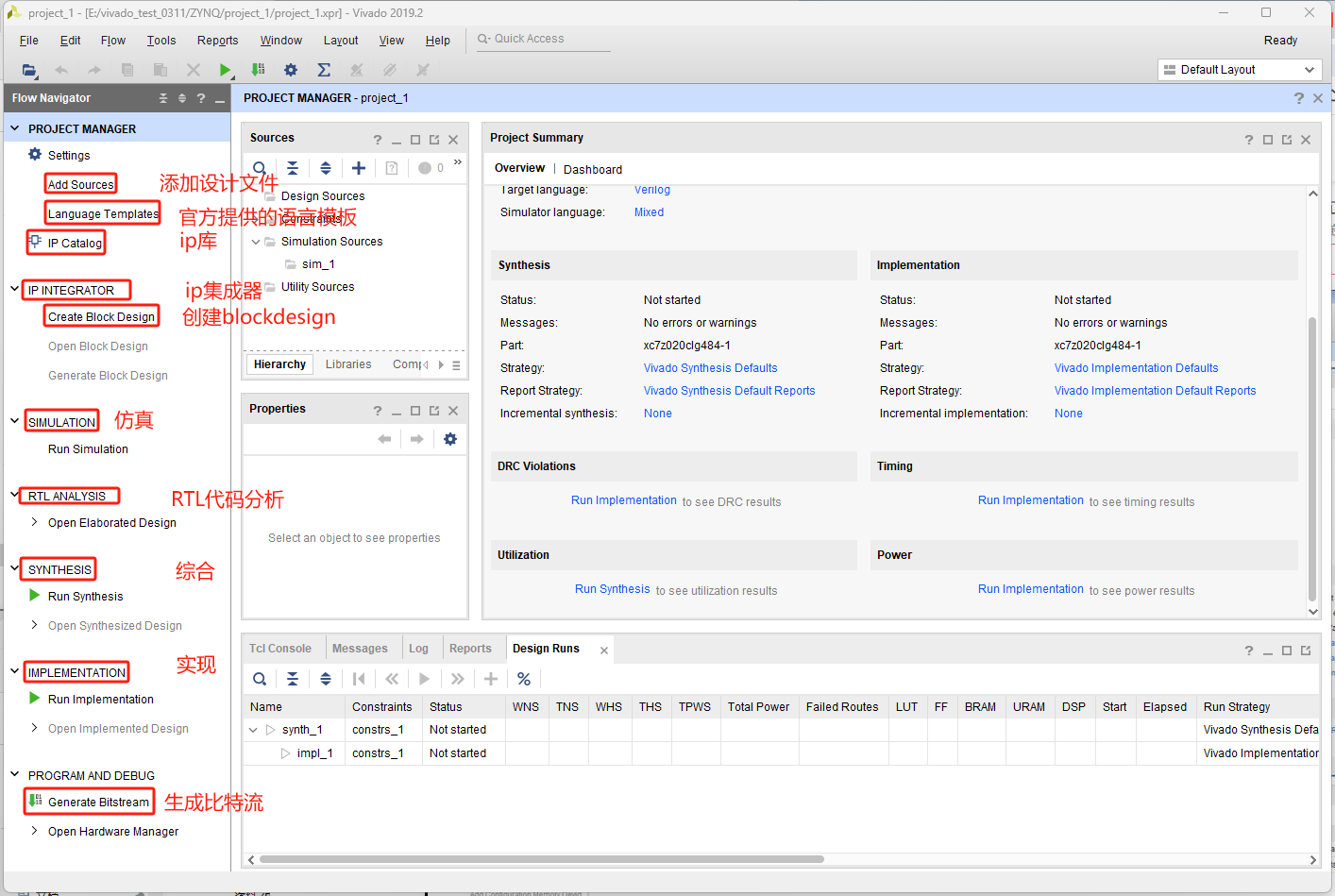

实际的开发顺序也是从上到下。

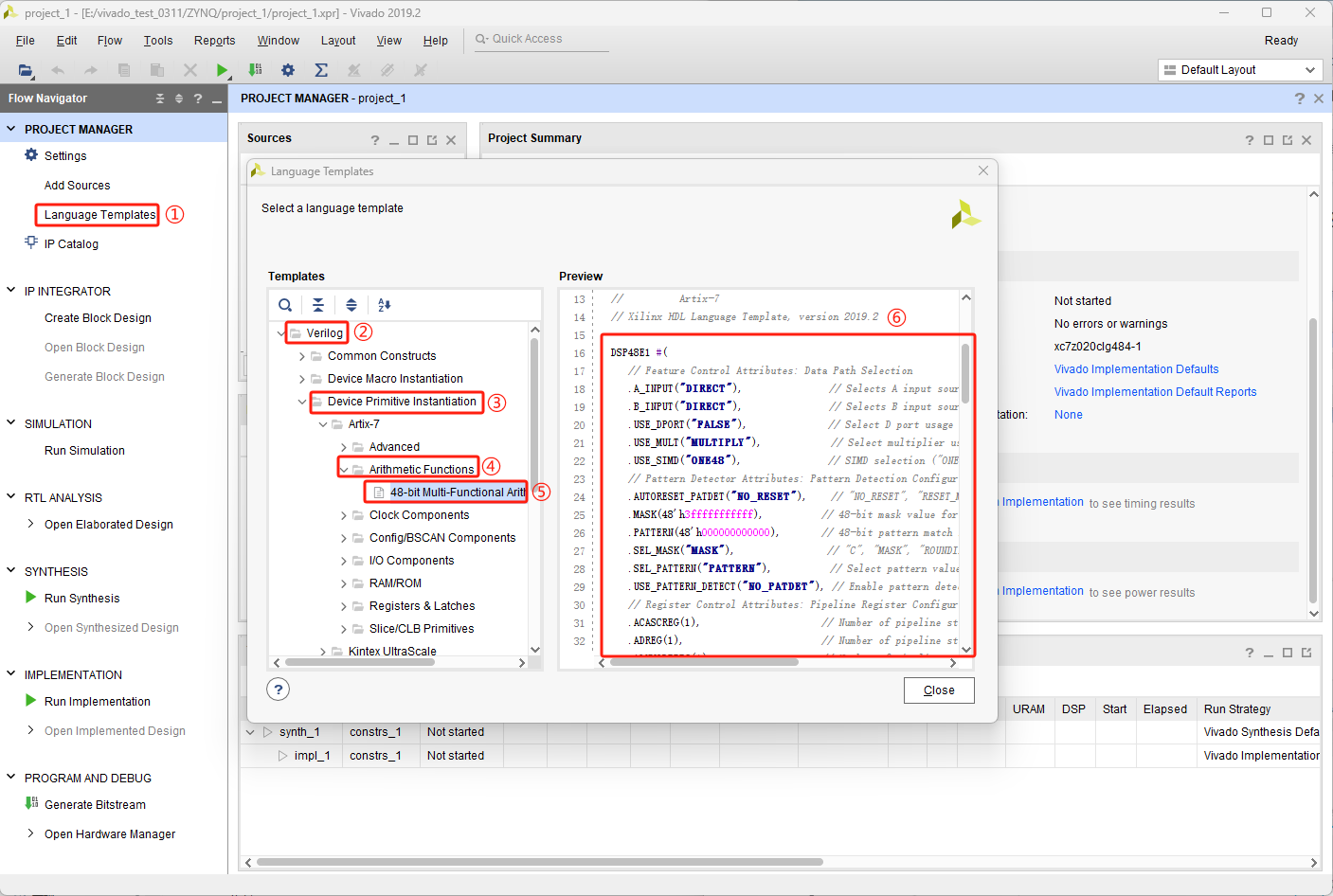

官方语言模板的使用方法:

①-⑥: 其中⑥就是例化源语的模板。可以直接拷贝出来。

更改soc的方法

若需要更改soc器件的型号:

按照如下方式重新选择

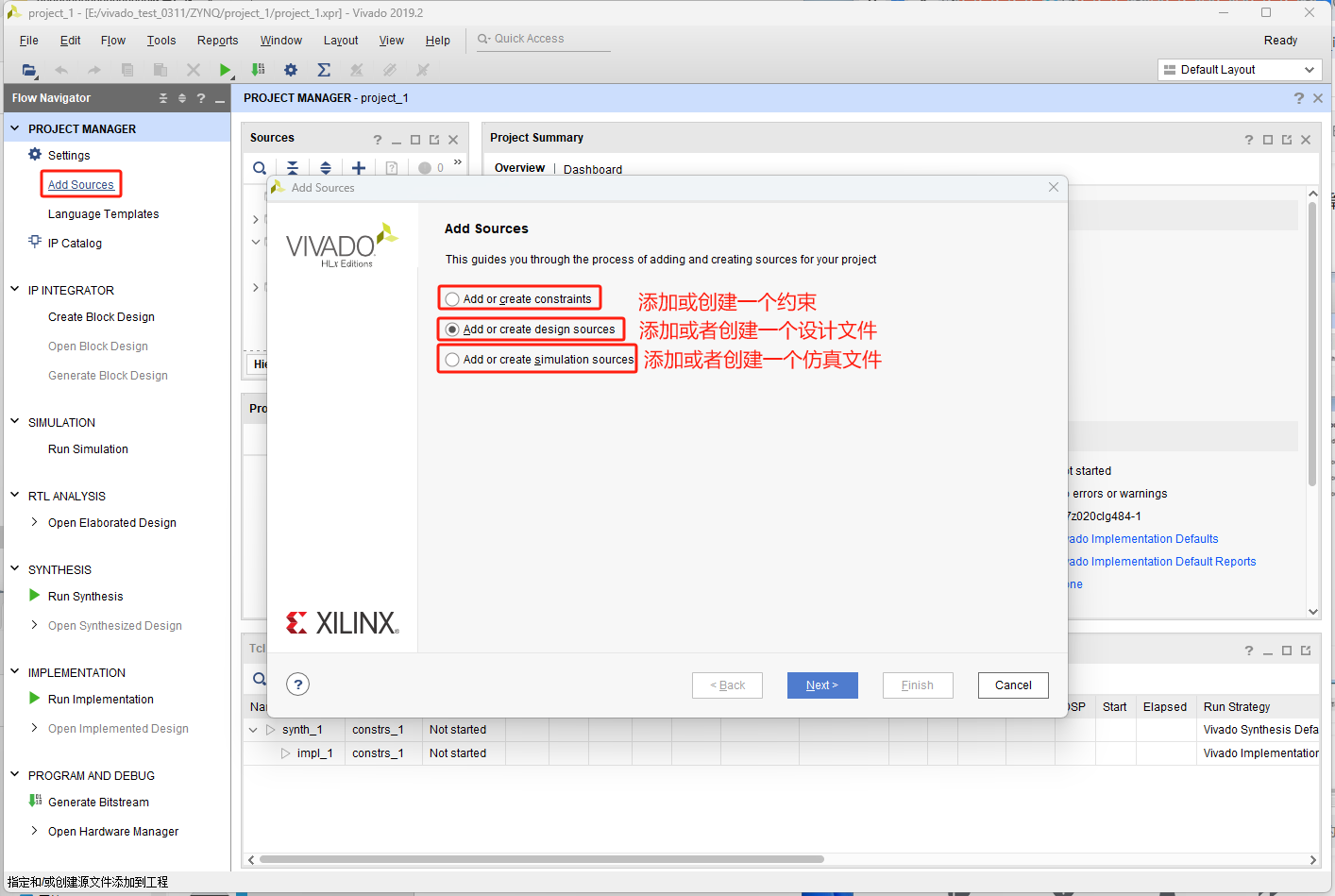

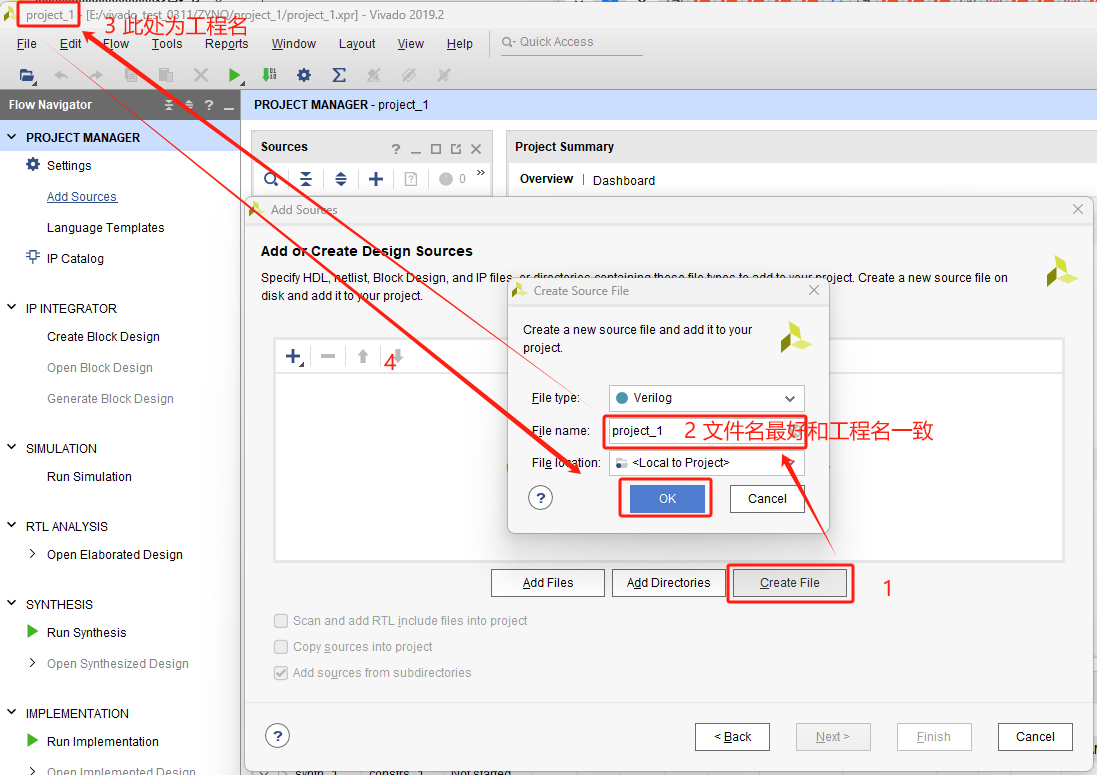

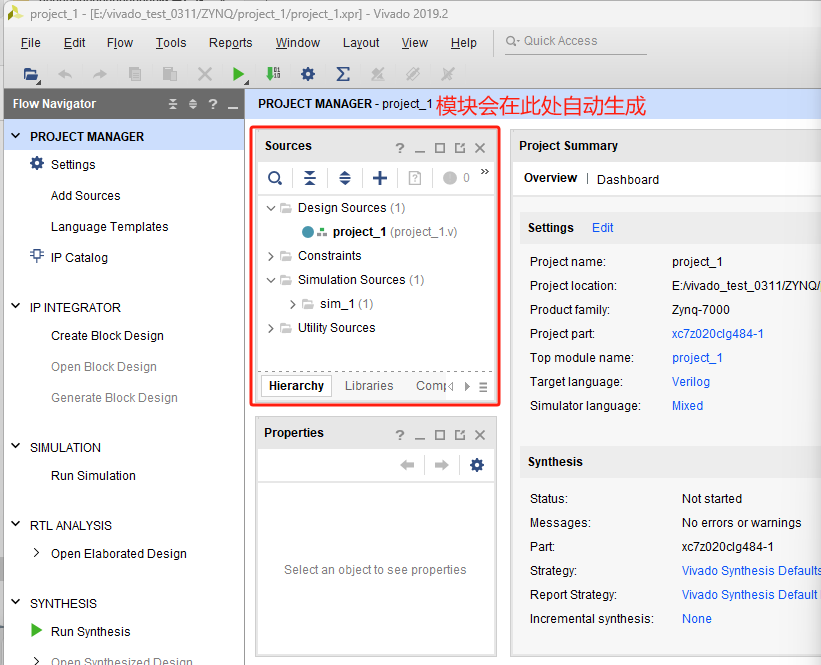

2.设计输入

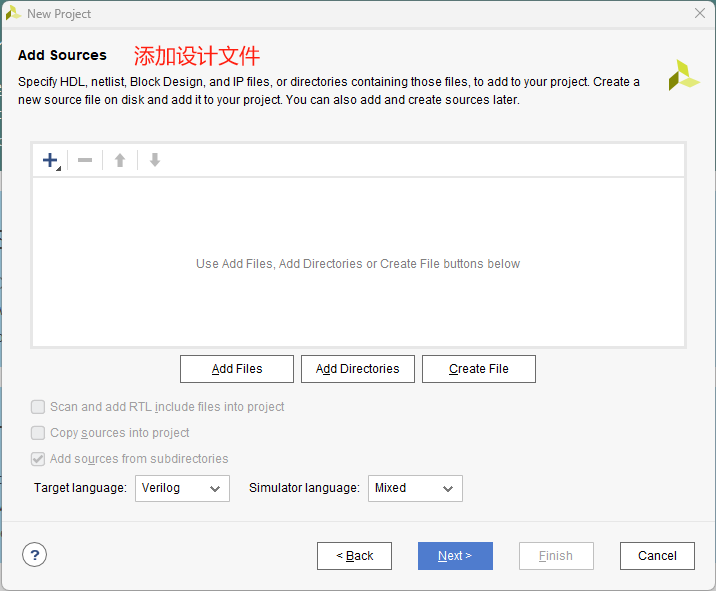

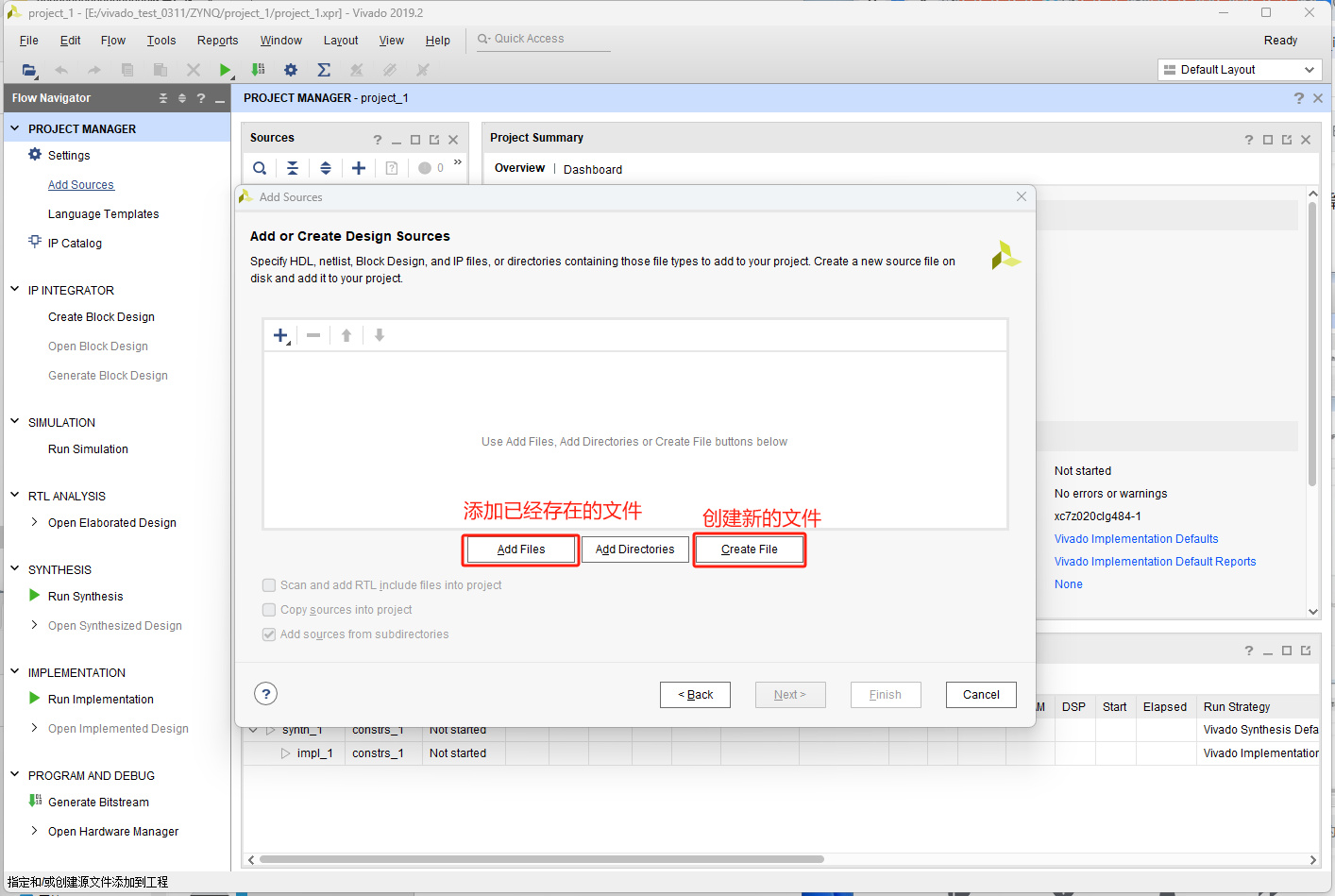

如果有写好的代码可以直接添加已经存在的文件,如果没有可以创建新的文件。

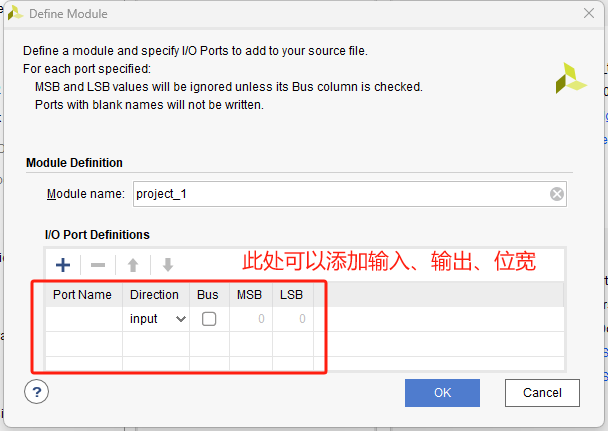

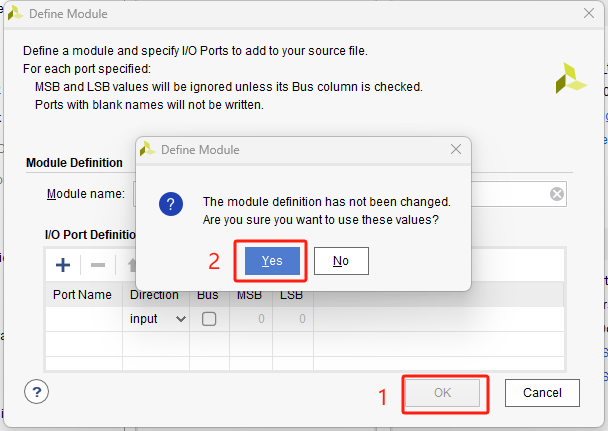

以下为创建新的文件

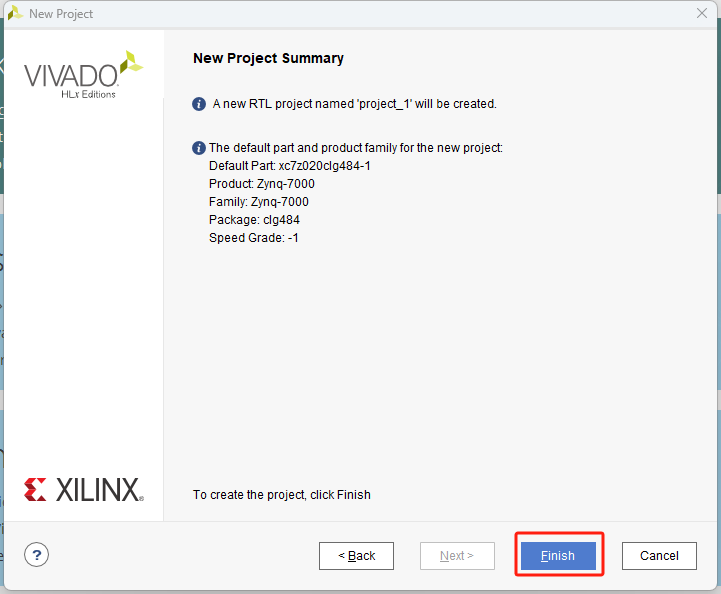

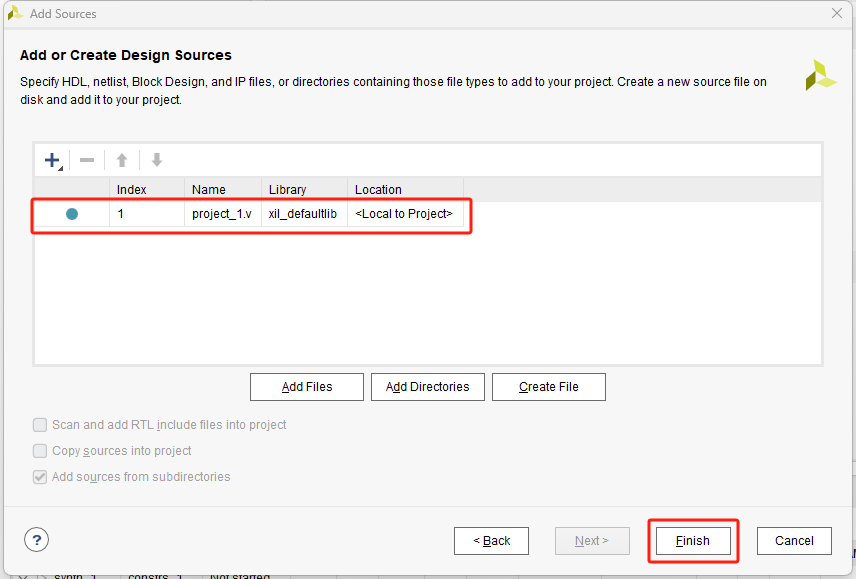

核对无误后点击finish

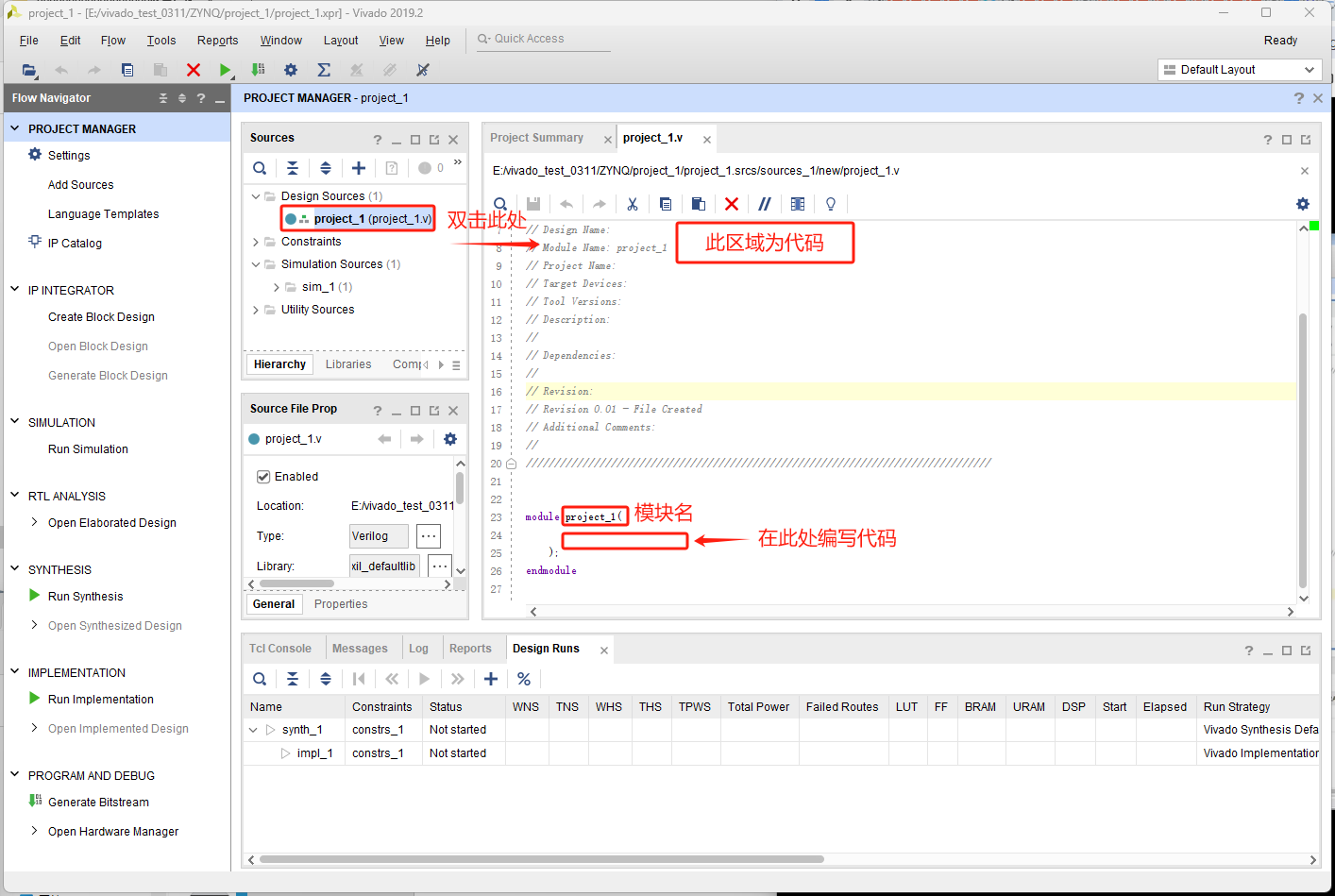

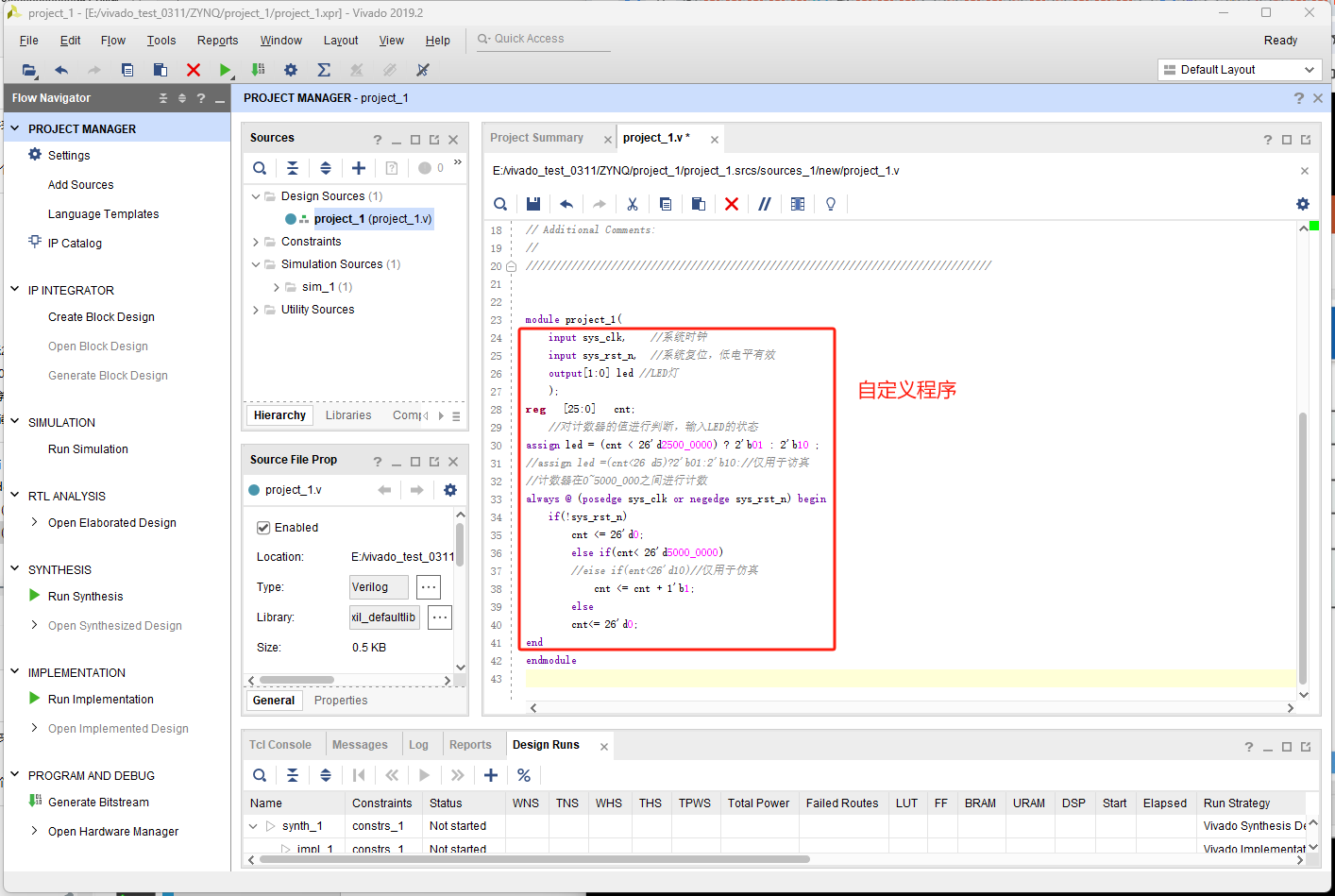

开始编写自定义的程序:

自定义程序:

module project_1(

input sys_clk, //系统时钟

input sys_rst_n, //系统复位,低电平有效

output[1:0] led //LED灯

);

reg [25:0] cnt;

//对计数器的值进行判断,输入LED的状态

assign led = (cnt < 26'd2500_0000) ? 2'b01 : 2'b10 ;

//assign led =(cnt<26 d5)?2'b01:2'b10://仅用于访真

//计数器在0~5000_000之间进行计数

always @ (posedge sys_clk or negedge sys_rst_n) begin

if(!sys_rst_n)

cnt <= 26'd0;

else if(cnt< 26'd5000_0000)

//eise if(ent<26'd10)//仅用于仿真

cnt <= cnt + 1'b1;

else

cnt<= 26'd0;

end

endmodule

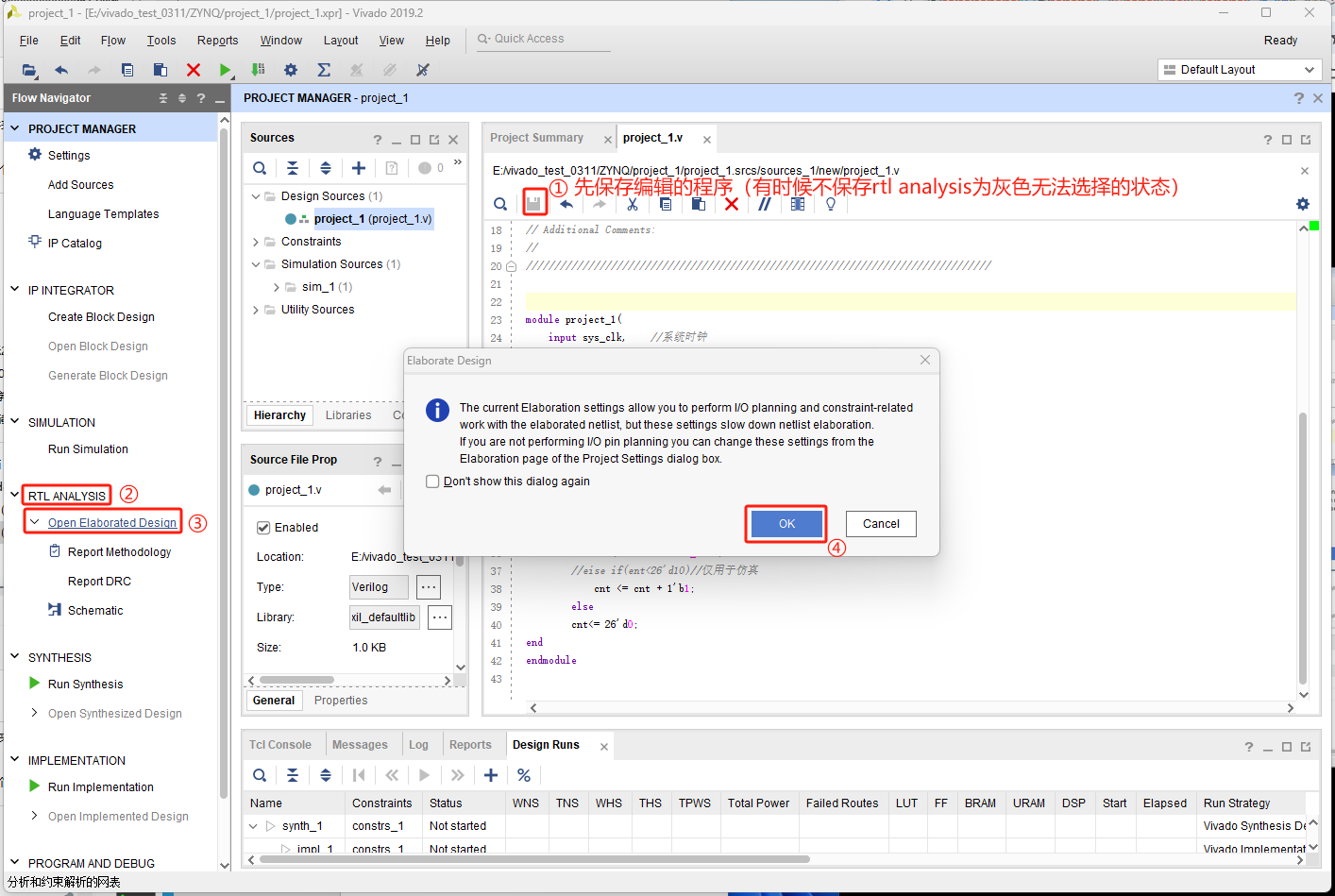

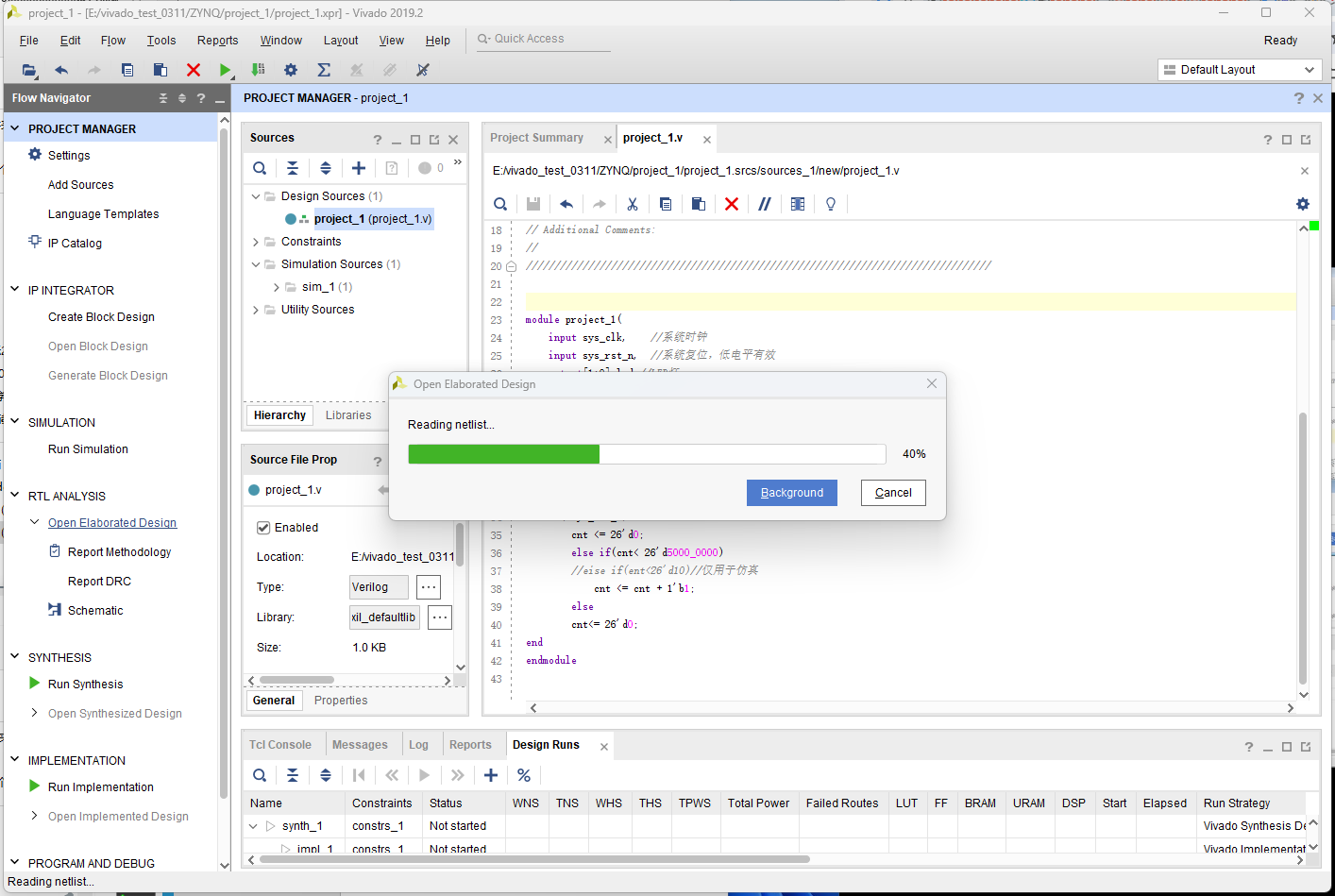

3.RTL分析设计

打开设计

左侧工具栏==>RTL ANALYSIS ==> ==Open Elaborated Design

稍等一会儿

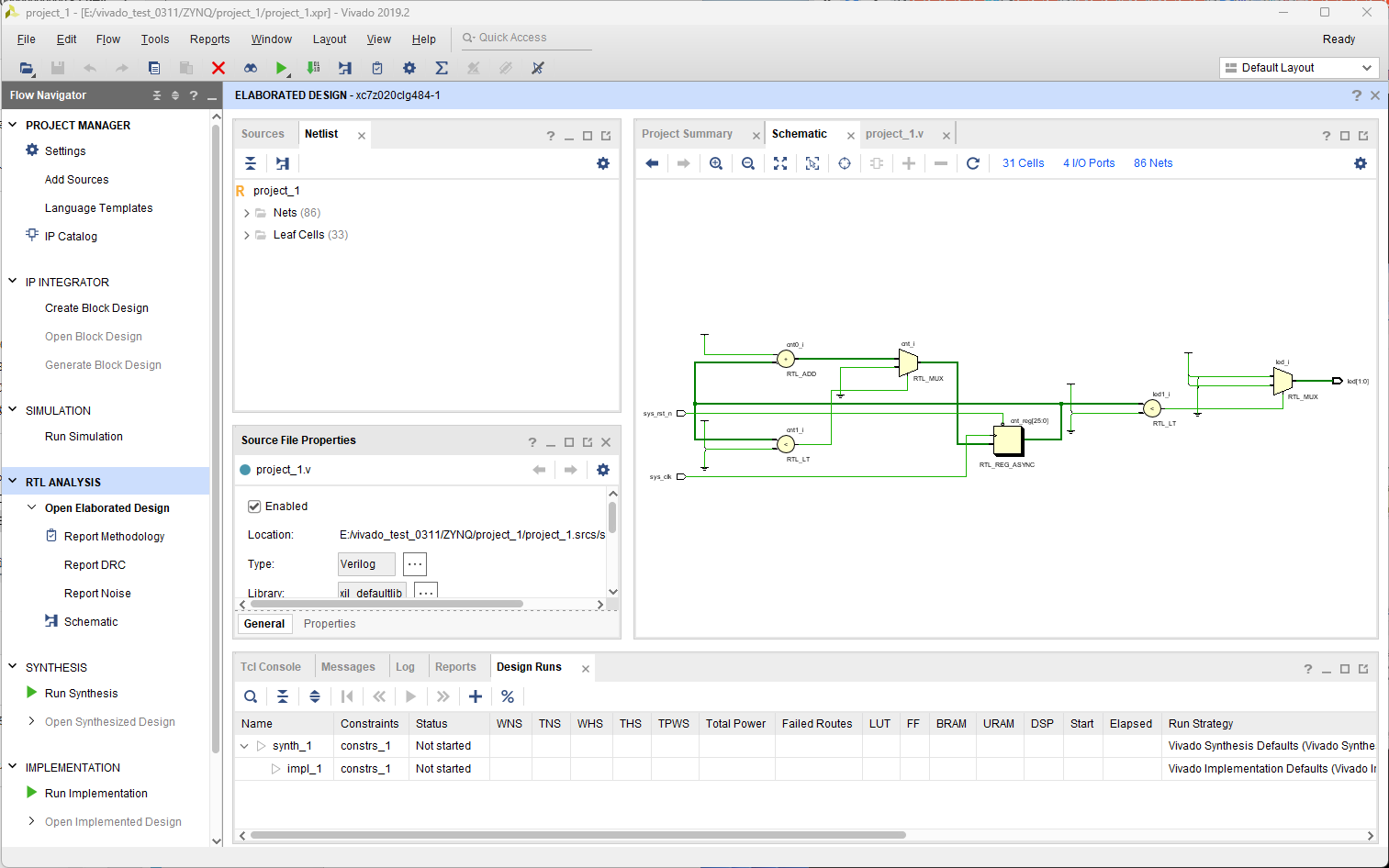

生成了下图右侧的原理图:

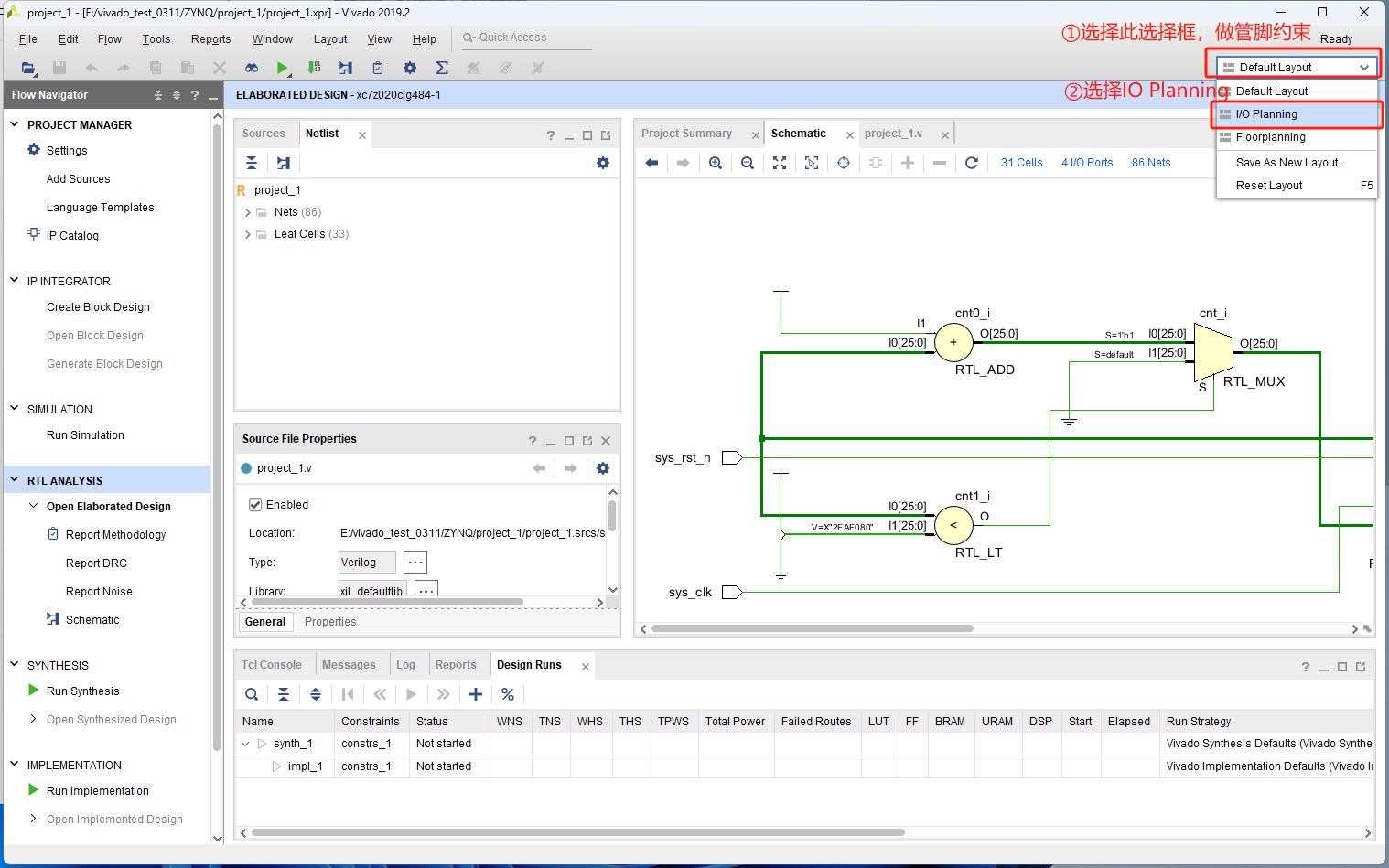

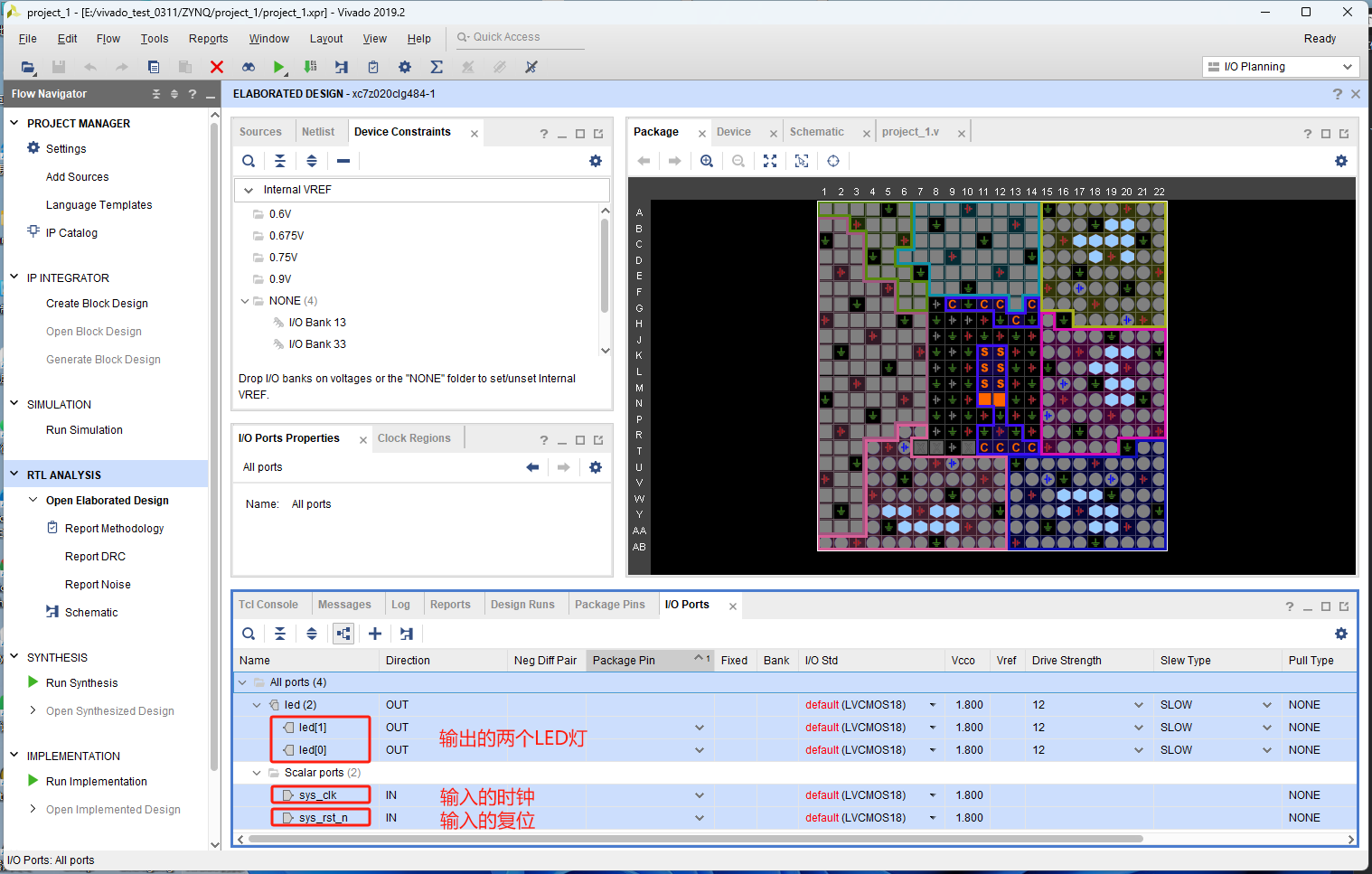

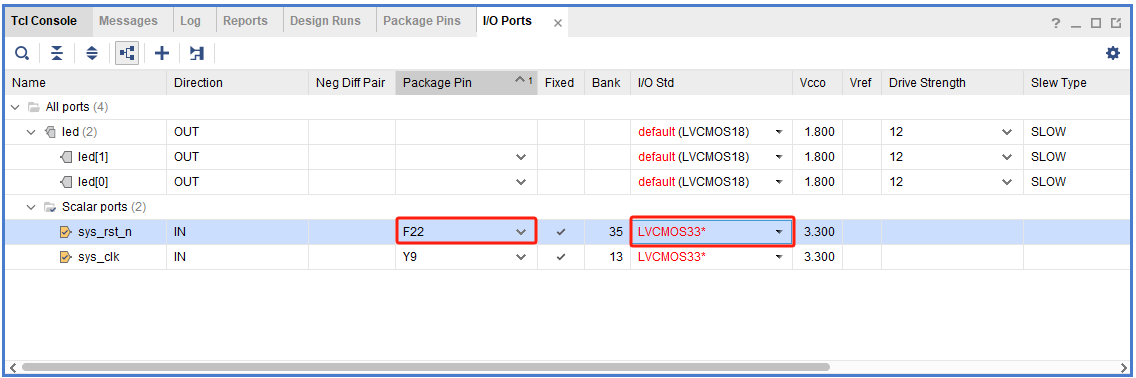

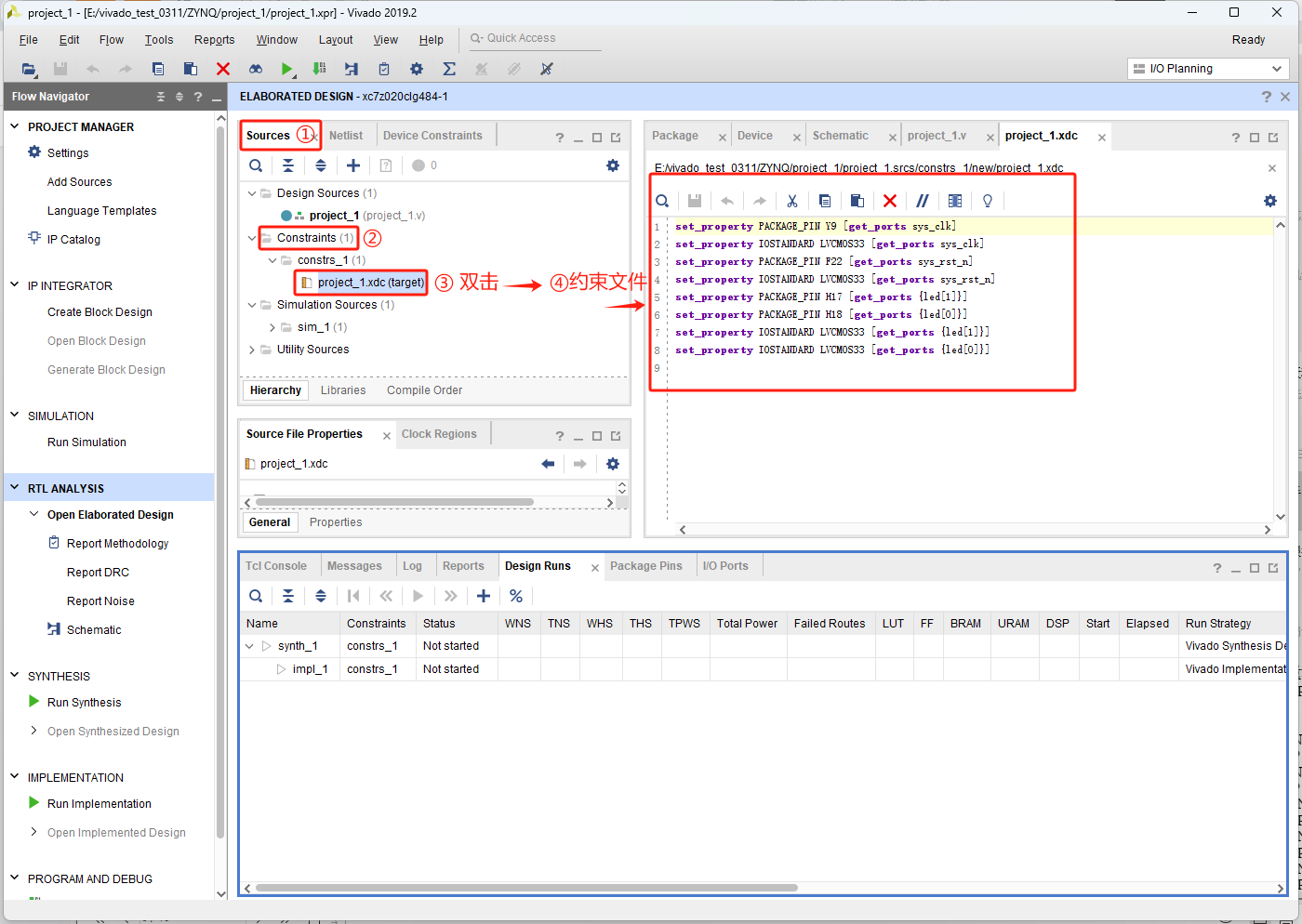

4.做IO引脚的约束:

方法①

将右上角的选择框调整到 IO-Planning管脚约束。

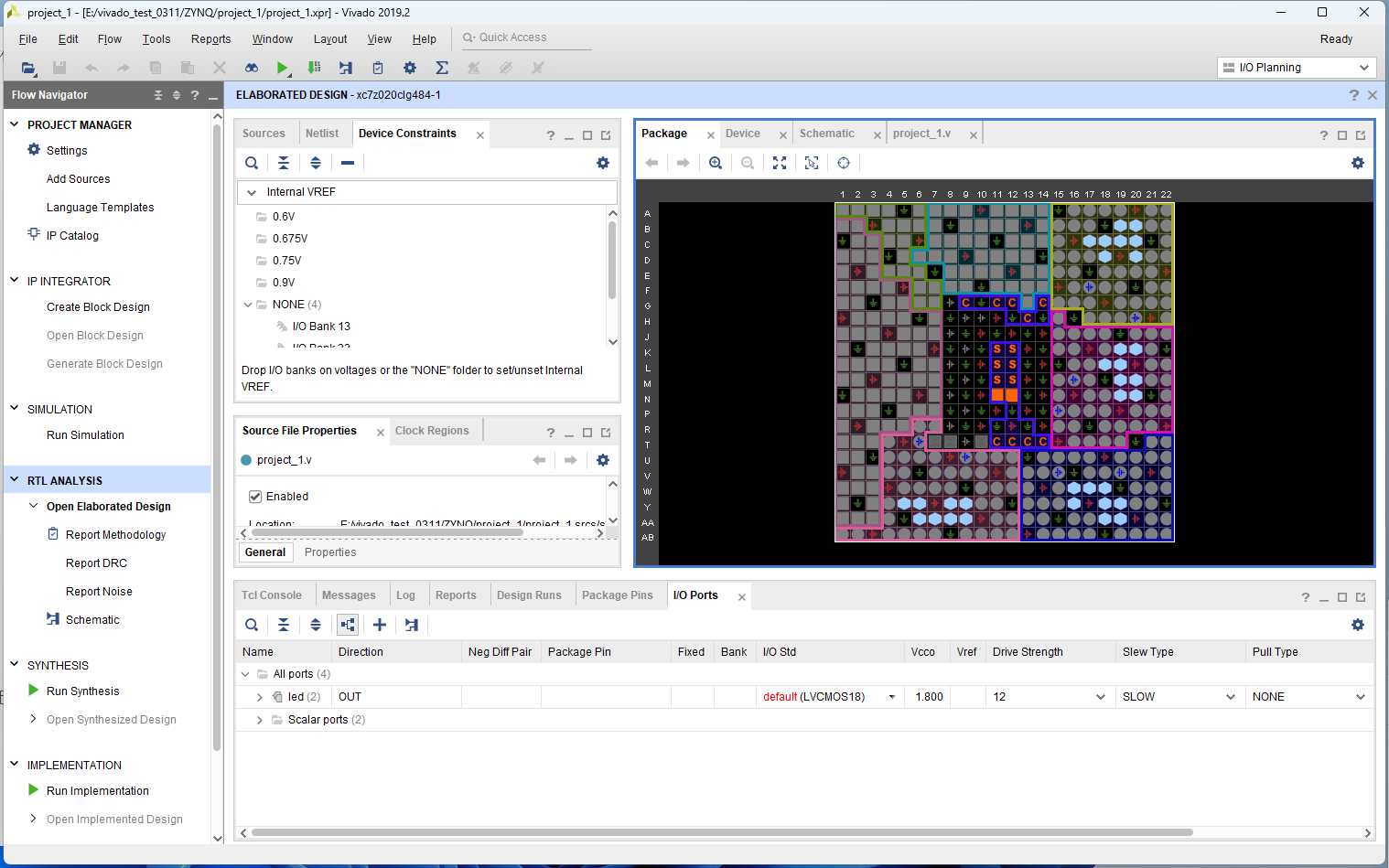

IO-Planning管脚约束界面如下:

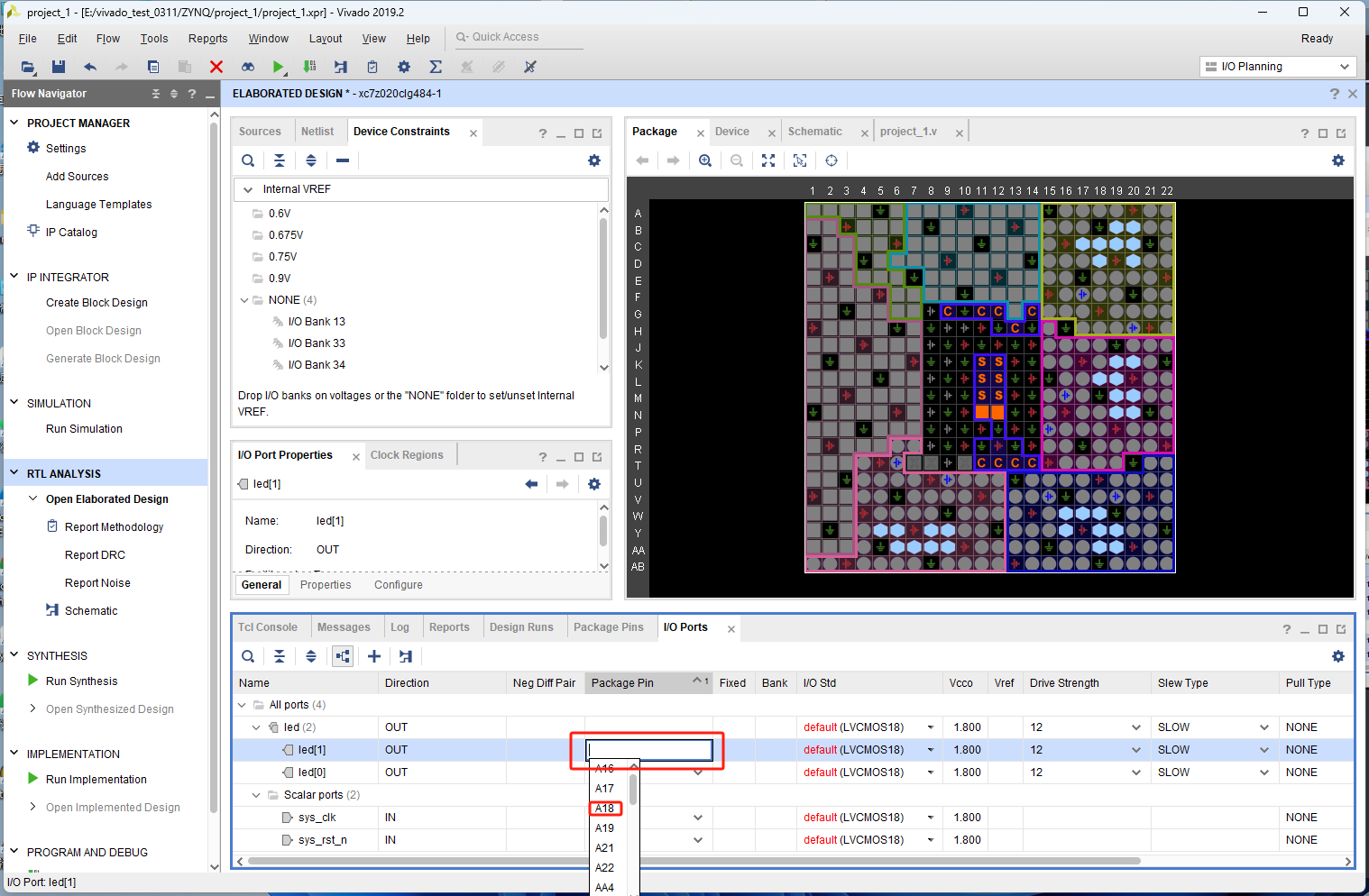

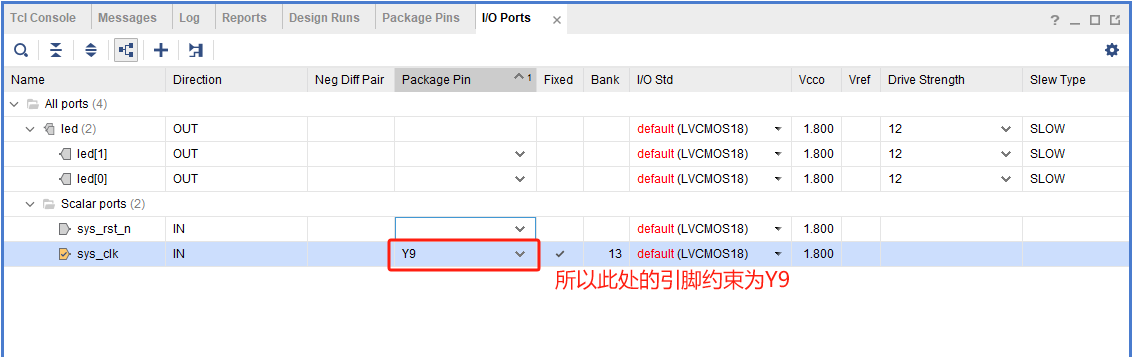

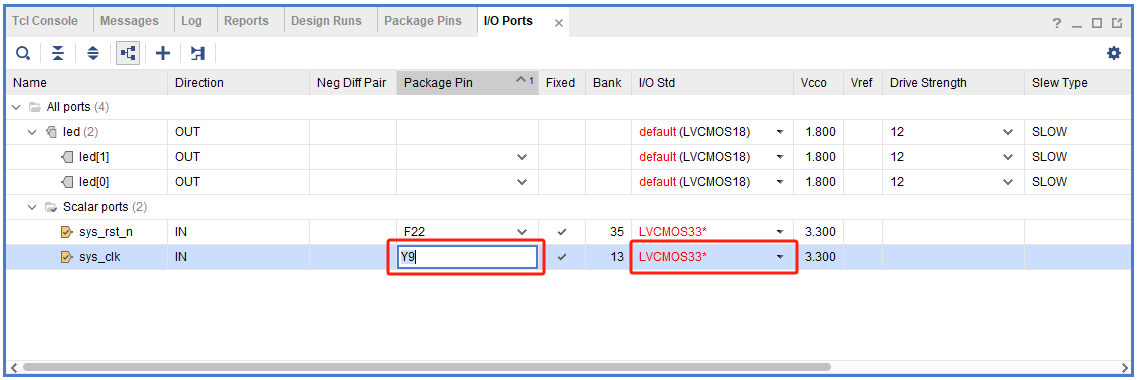

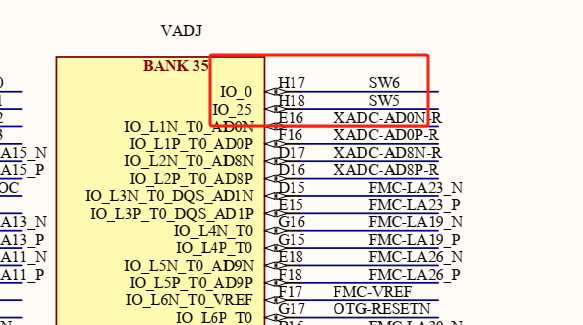

package pin 的管脚约束需要查看电路板的管脚的原理图,然后进行选择。

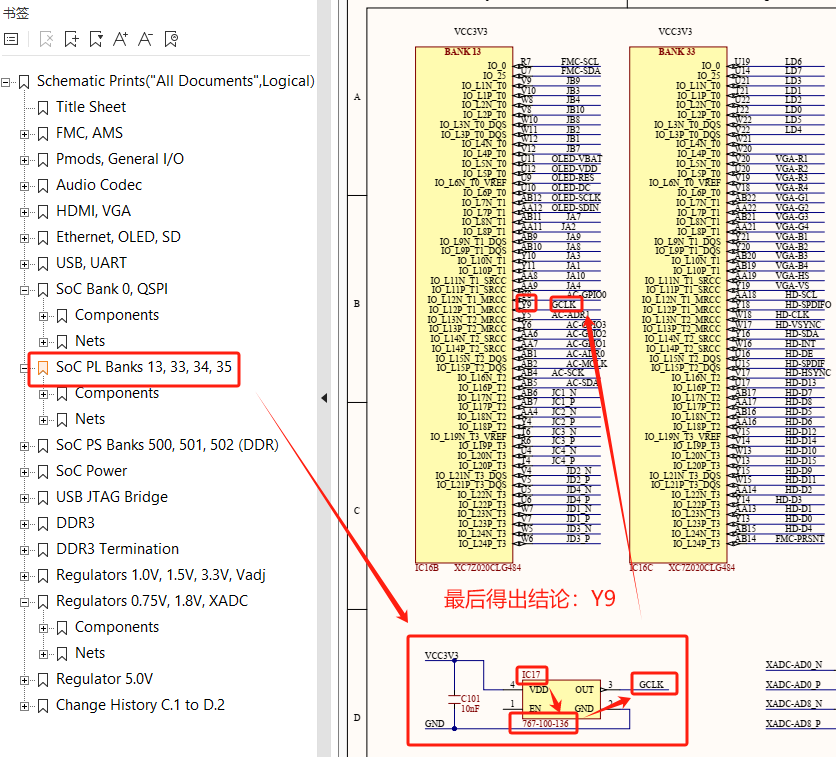

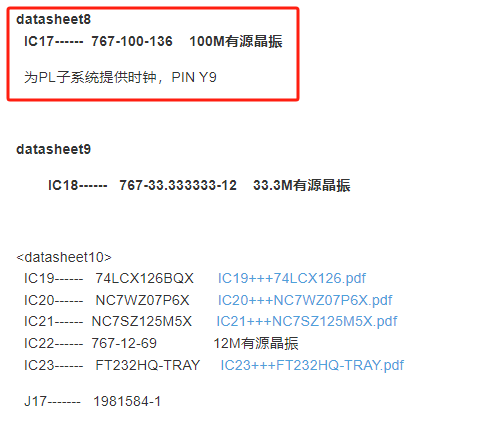

分配时钟引脚:

在PDF文件中搜索GCLK,找到PL的GLK

经过一段时间的查找,此晶振的具体数据为:https://blog.csdn.net/kobesdu/article/details/47132991

原视频的引脚为U18,但是在zedboard的开发板上面的的引脚设置为Y9

注意:引脚与电源的电压

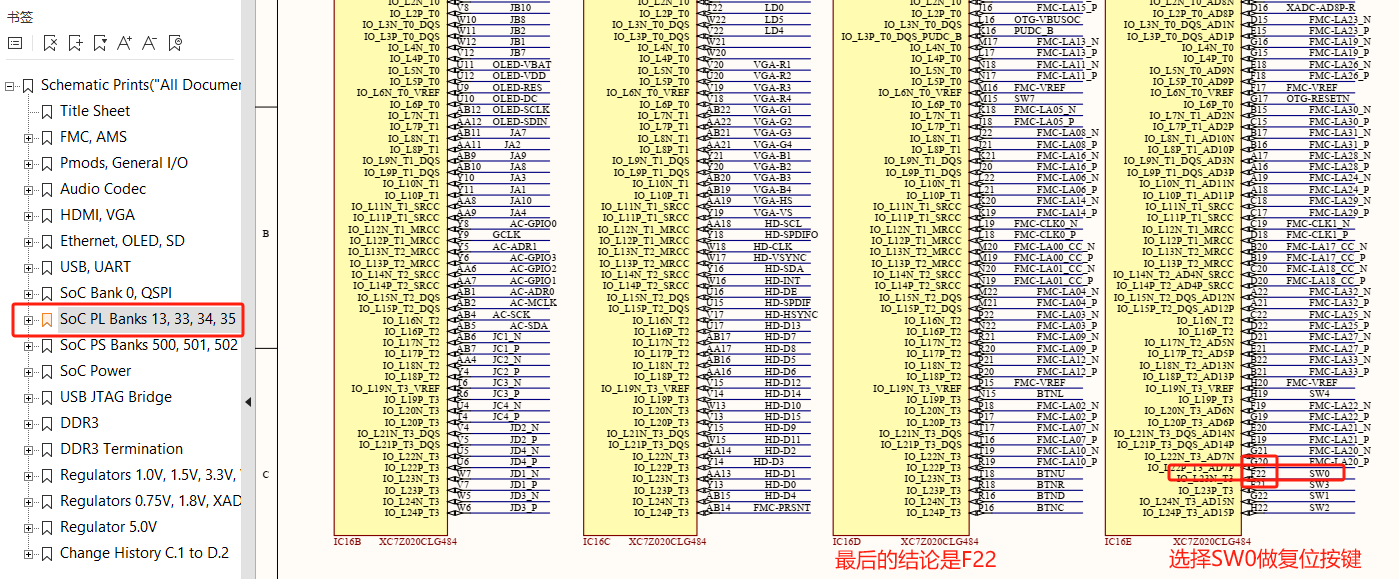

分配复位引脚:

在PDF中搜索reset,发现并未搜索到PL的reset,但是可以利用SW0做功能的替换。

原视频的引脚为N16,此处采用得 引脚为F22

注意:引脚与电源的电压

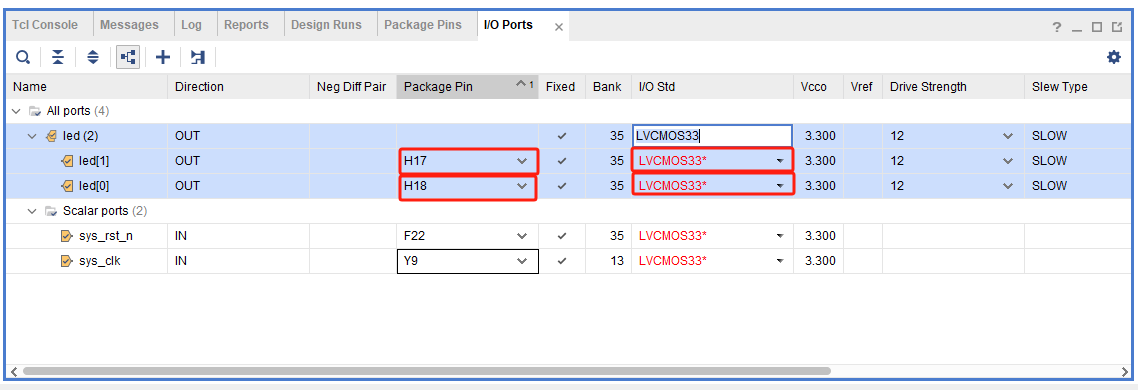

分配LED引脚:

注意LED的电压,进行电压更改。

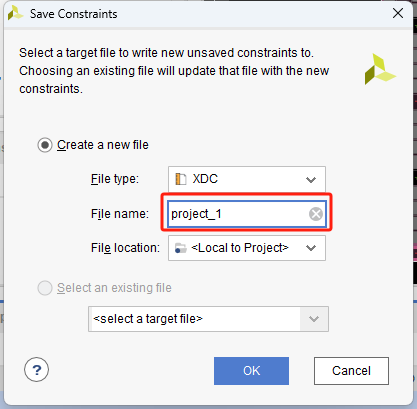

将所有的引脚都分配完之后进行保存(快捷键 ctrl+s)

保存的文件夹命名和项目命名一致,此次命名为project_1

生成的.XDC文件(展示)

set_property PACKAGE_PIN Y9 [get_ports sys_clk]

set_property IOSTANDARD LVCMOS33 [get_ports sys_clk]

set_property PACKAGE_PIN F22 [get_ports sys_rst_n]

set_property IOSTANDARD LVCMOS33 [get_ports sys_rst_n]

set_property PACKAGE_PIN H17 [get_ports {led[1]}]

set_property PACKAGE_PIN H18 [get_ports {led[0]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

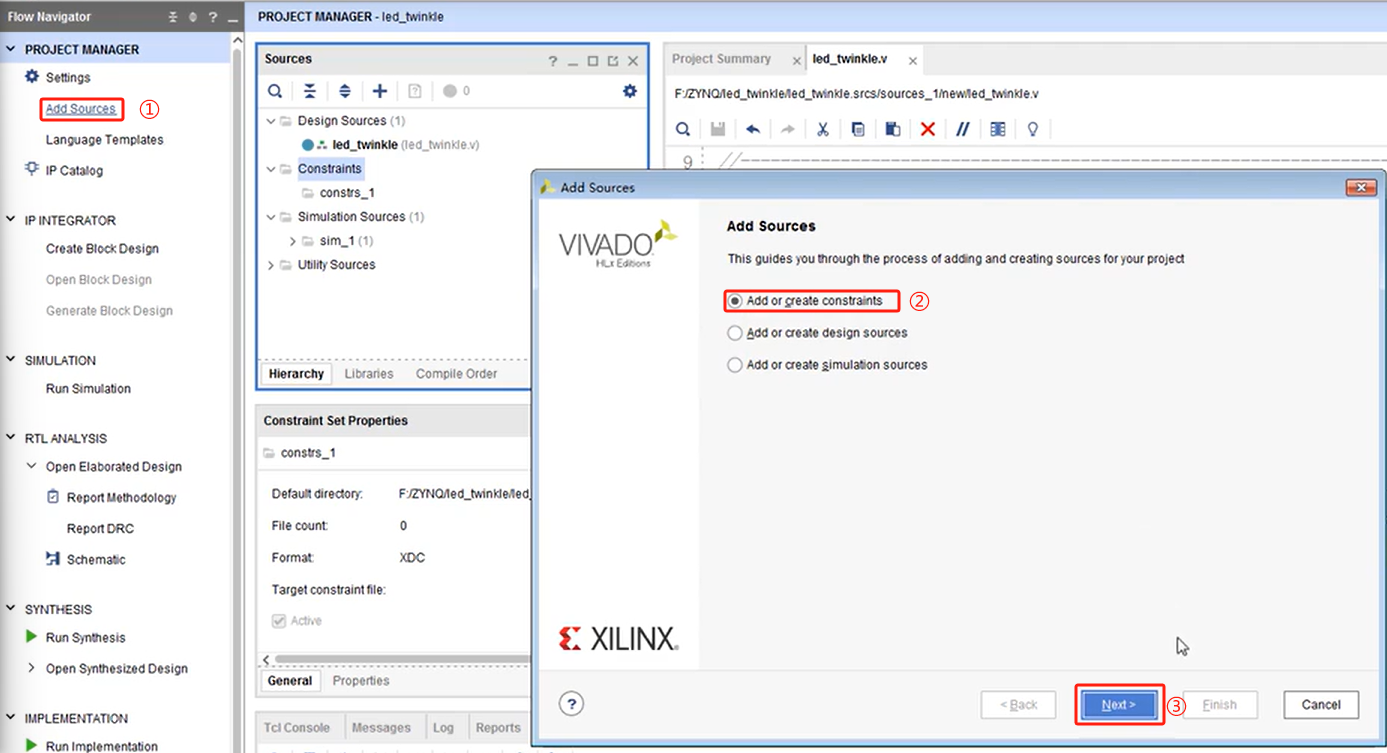

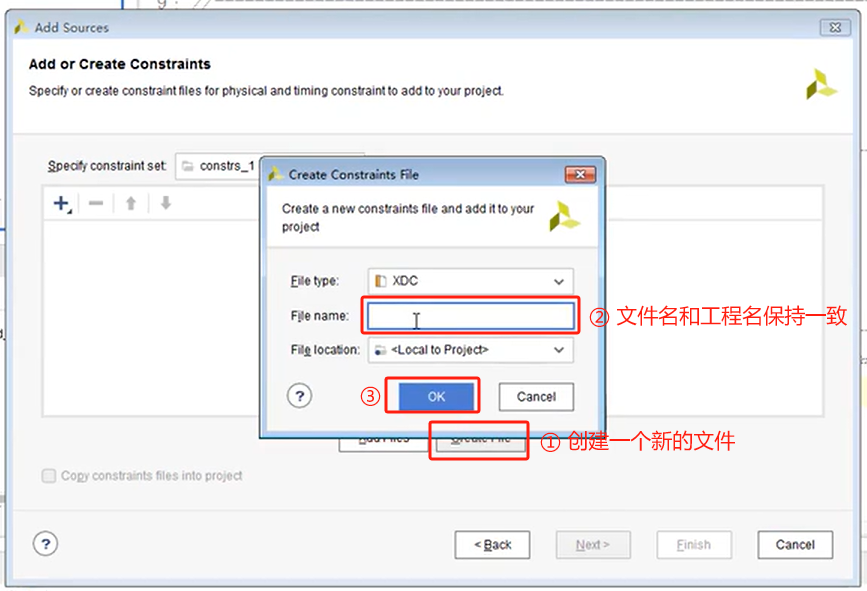

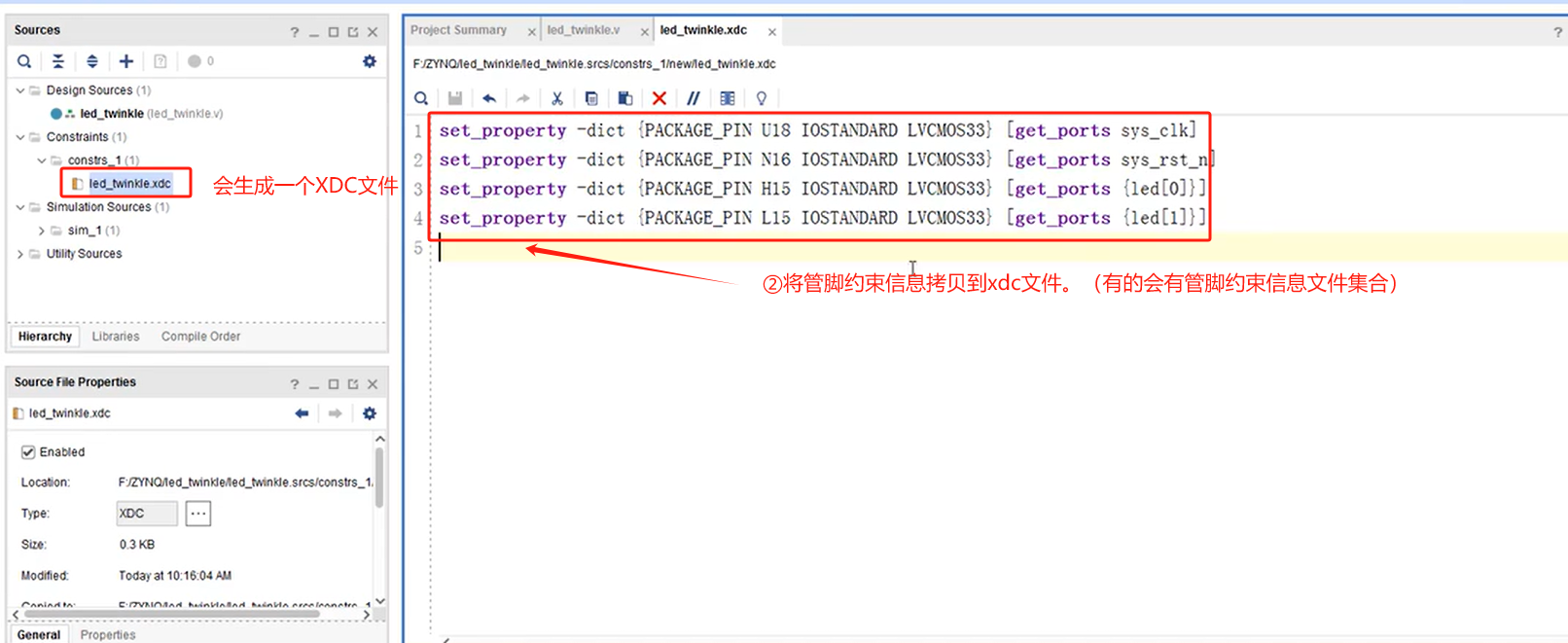

方法②

注意,自动生成的管脚约束信息是两行,而此处写的是集合到了一行,两种写法都可以。

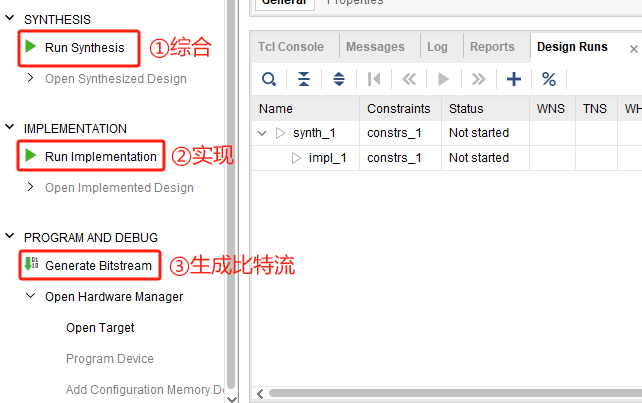

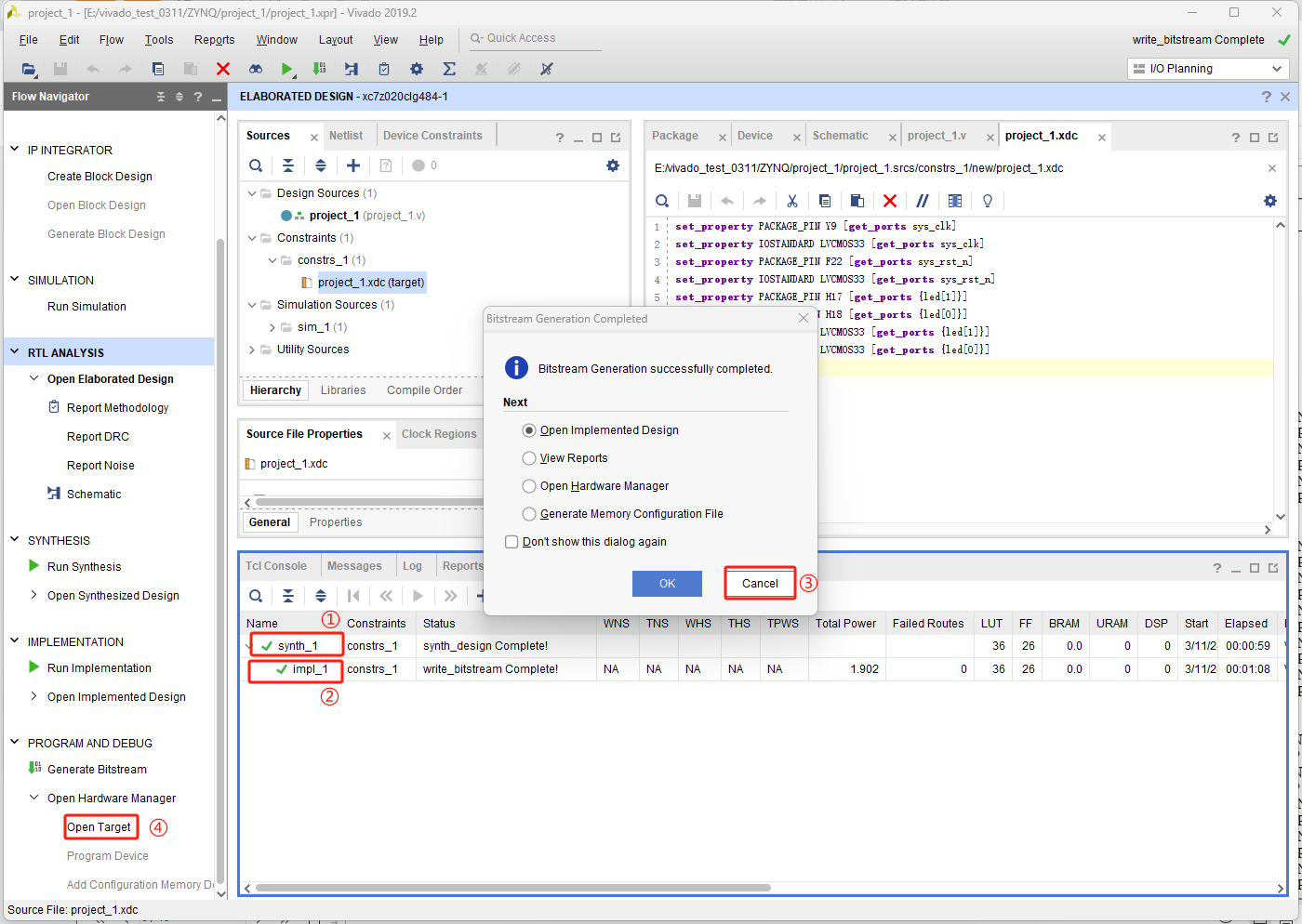

5、分析综合、设计实现、生成比特流

方法①逐步进行

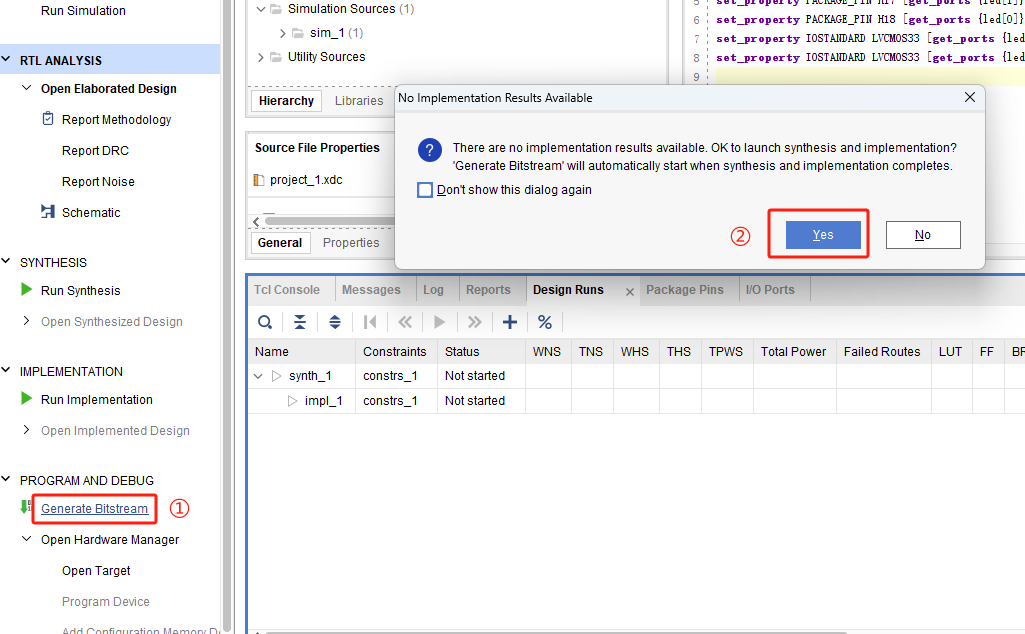

方法② 直接生成比特流

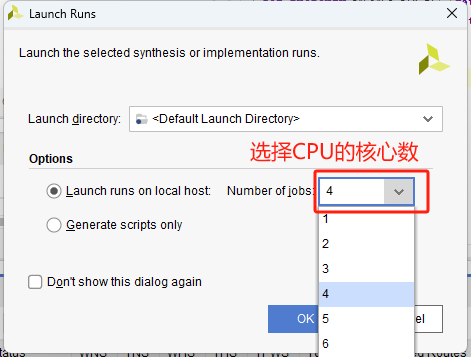

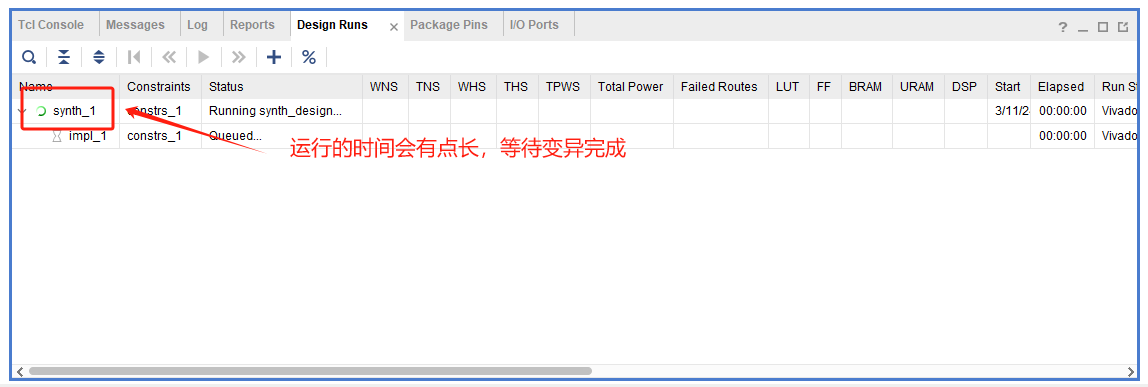

选择cpu核数。

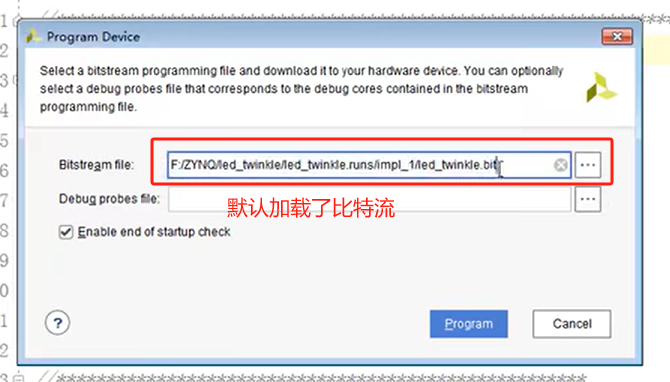

编译完成后按如下顺序操作

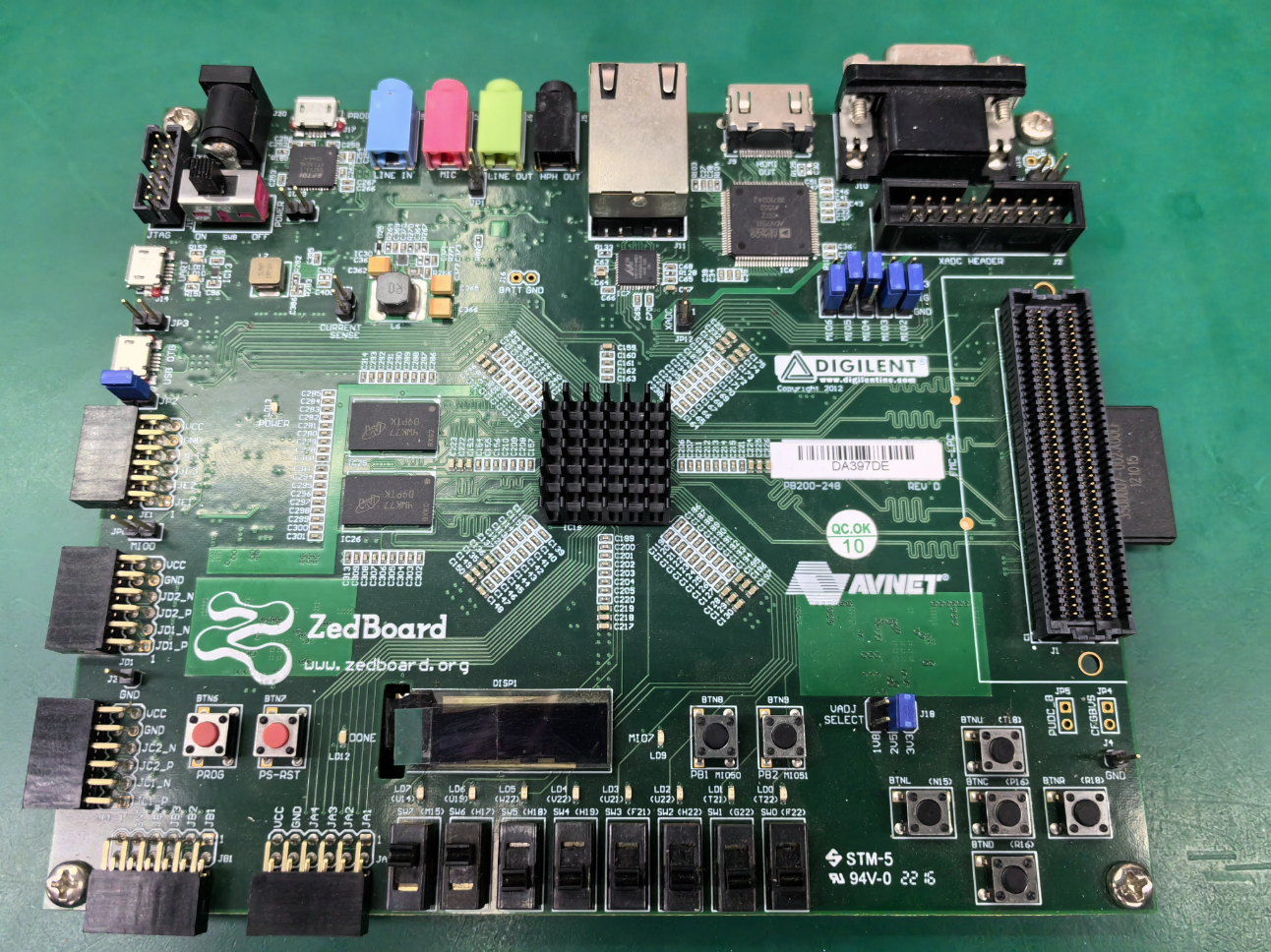

之后准备好硬件电路:

准备好电源线,下载器,先打开电源开关:

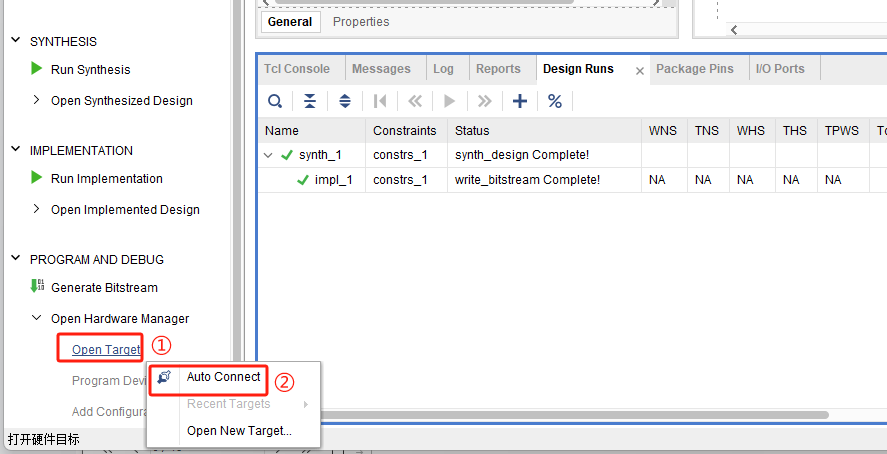

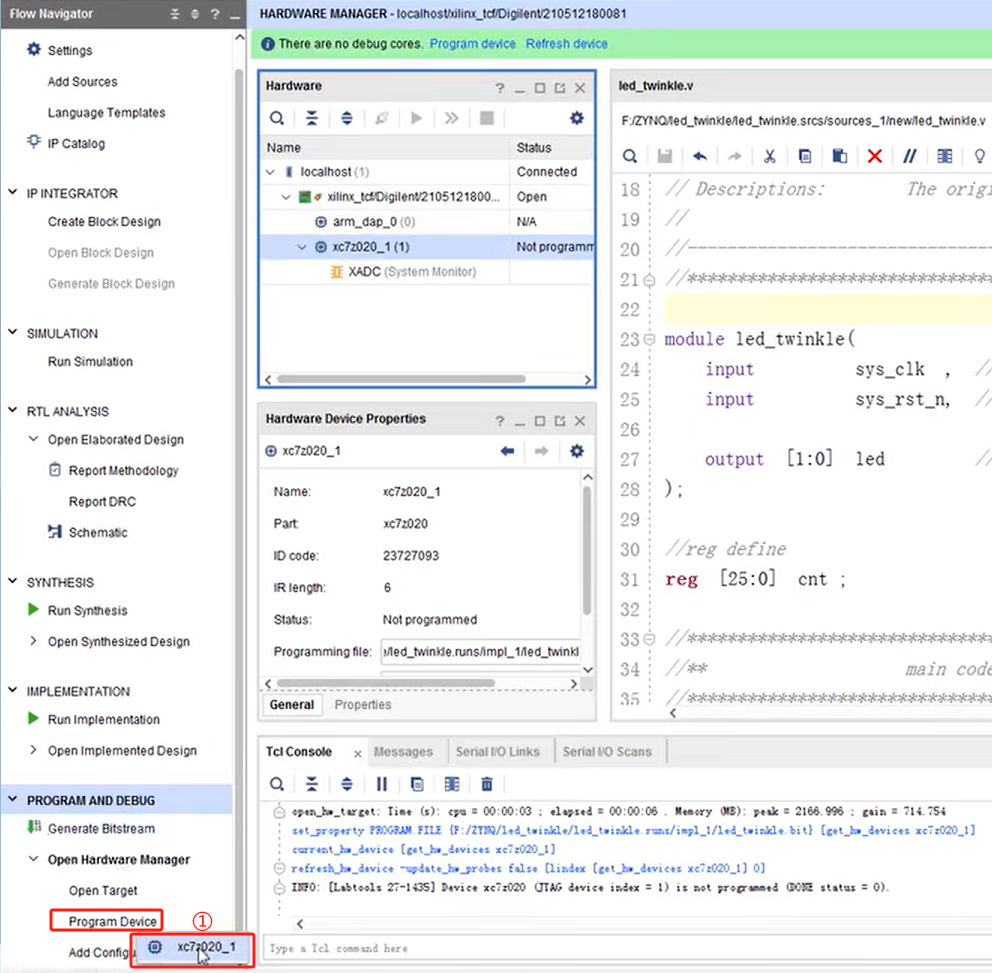

此时需要先将连接器连接好,将开发板上电,否则此处无法进行连接。

然后进行下面的操作。

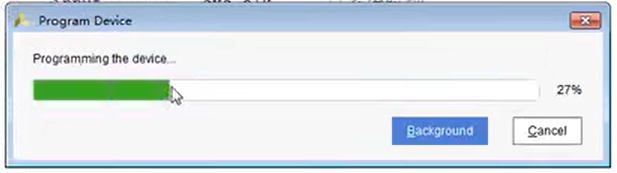

直接点击program

zedboard的配置的灯会亮,两个灯会交替闪烁

注意:开发板断电后上电,程序就没了。

标签:set,led,get,LZQ,引脚,0311,vivado,property,ports From: https://www.cnblogs.com/L707/p/18067635vivado视频教程:

第一讲:https://www.bilibili.com/video/BV1XU4y1M7nw?p=7&vd_source=da31a9aa66fbe4d6b904e621d9943c75

第三讲:https://www.bilibili.com/video/BV1XU4y1M7nw?p=9&vd_source=da31a9aa66fbe4d6b904e621d9943c75