Cadence Sigrity Power-aware SI工具包介绍

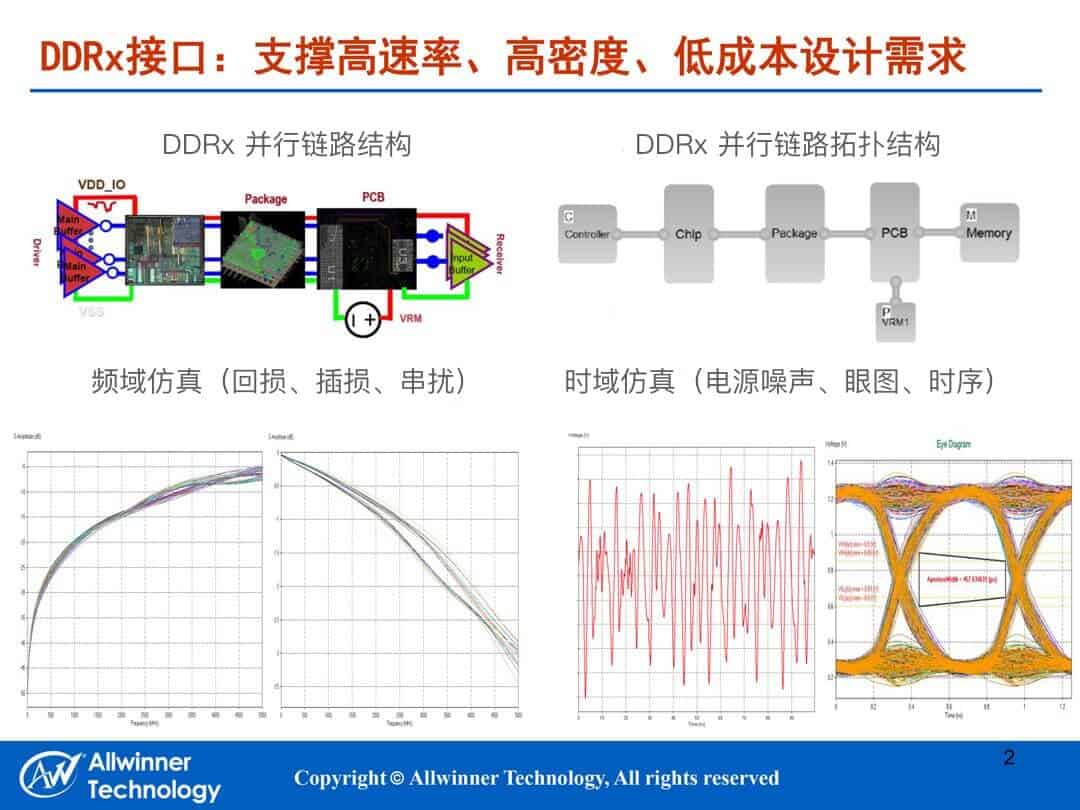

- Power-aware SI工具包是Cadence公司针对源同步并行总线如DDR3、 DDR4等所提供的完整的仿真解决方案。

- 基于行业领先的Sigrity专利技术,Power-aware SI工具包可以快速 、精确提取封装和PCB的信号布线和电源分布系统的网络参数,然后 在模块化的系统级仿真环境中加载模型进行时域波形仿真。

- Power-aware SI工具包能够同时考虑信号完整性和电源完整性,同时 仿真分析反射、串扰、码间干扰和同步开关噪声的影响,并根据 Jedec规范对仿真波形自动进行测量分析并生成波形质量/时序裕量报 告,为DDRx总线的仿真提供了卓越的准确性和操作的方便性。

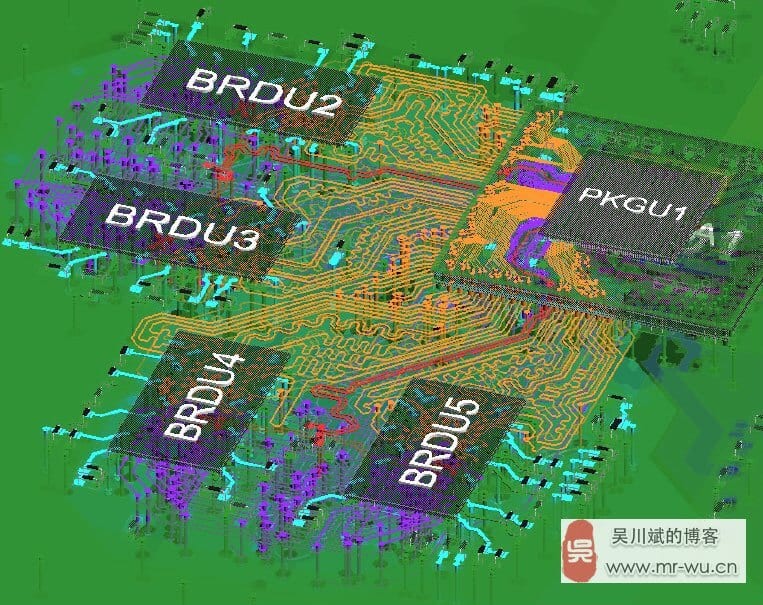

案例介绍–物理链路

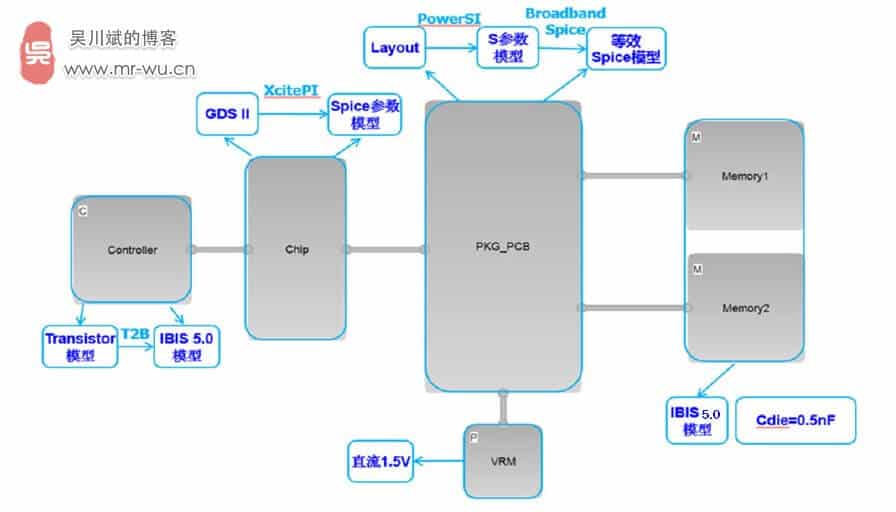

本案例为平板产品主控芯片的DDR3接口。 该芯片共有2个独立的 Memory Controller, 每个Controller带两片Memory颗粒。每个Controller带32位DQ数据,如左图橙色网络所示,仿真速率为 1600Mpbs。紫色网络为地址、命令信号, 红色网络为差分时钟信号。浅蓝色网络为VCC-DRAM电源网络。

Controller模型使用Sigrity T2B工具将后仿的晶体管级spice网表转换成IBIS 5.0模型 。芯片内部金属层的布线,使用Sigrity XcitePI工具提取其RLCK模型。主控芯片的封装基板和PCB的设计文件通过添加Solderball,在物理上连接起来后,使用Sigrity PowerSI工具一起提取S参数模型。Memory模型,本案例使用的是厂商提供的IBIS 5.0模型

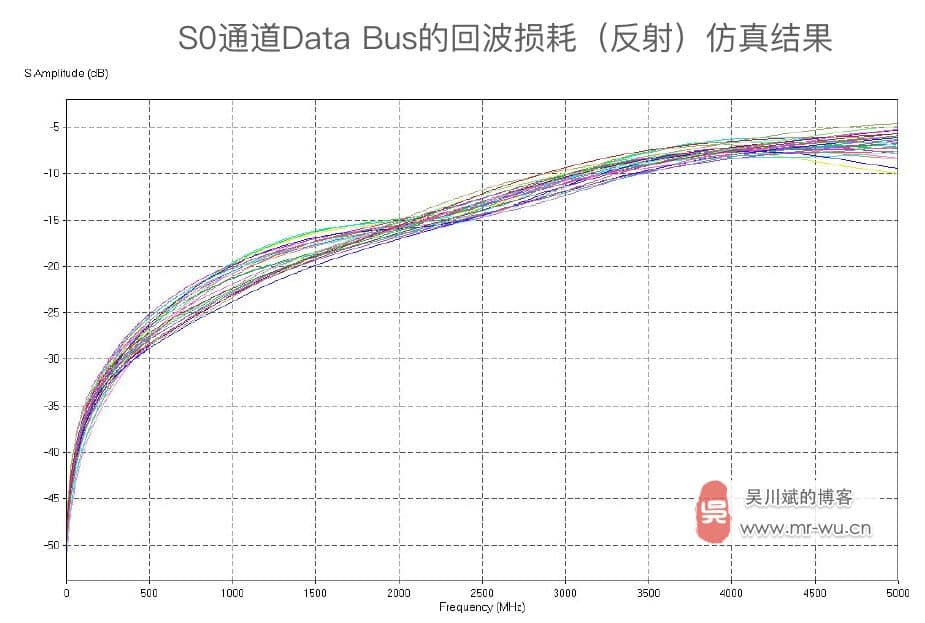

S0通道Data Bus的回波损耗(反射)仿真结果

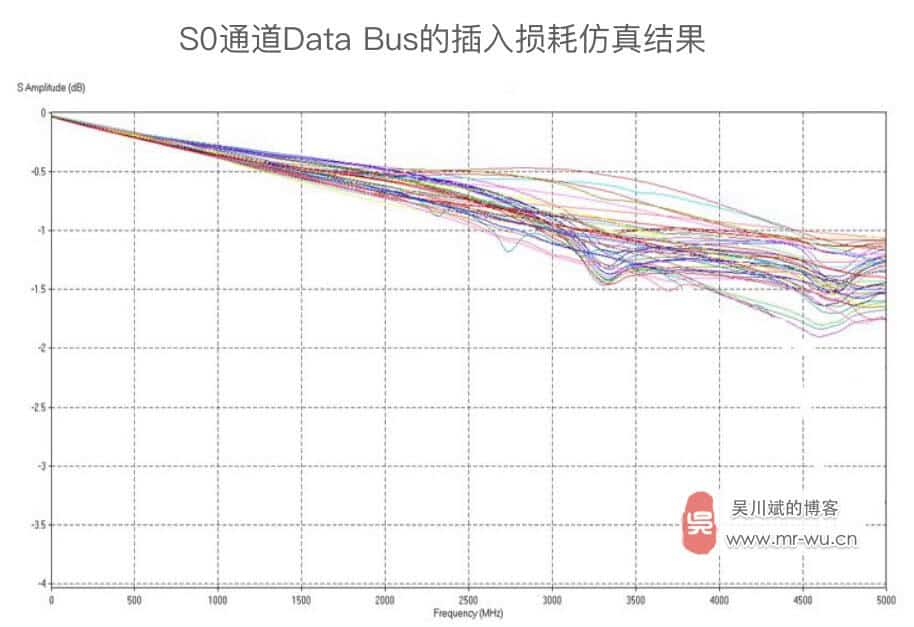

S0通道Data Bus的插入损耗仿真结果

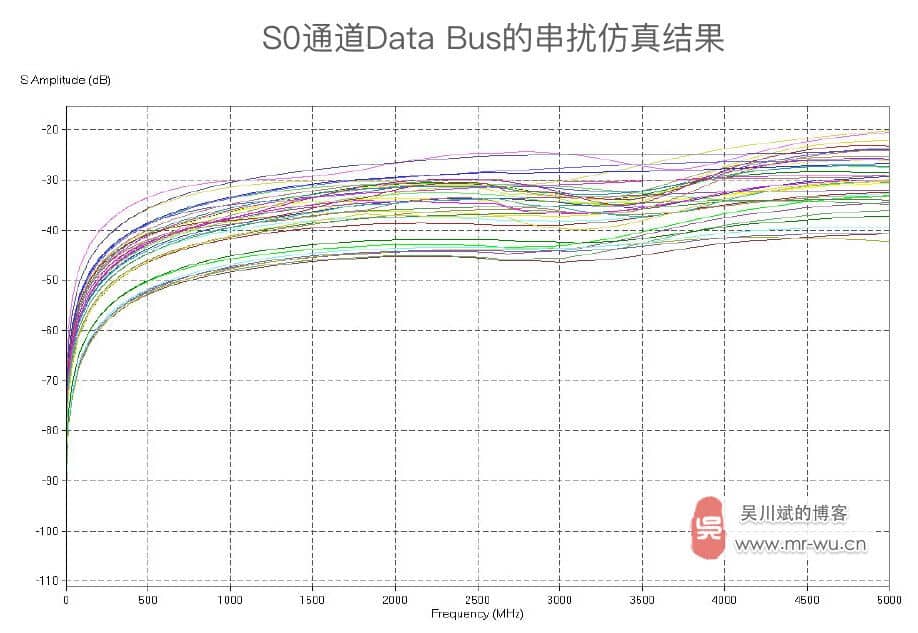

S0通道Data Bus的串扰仿真结果

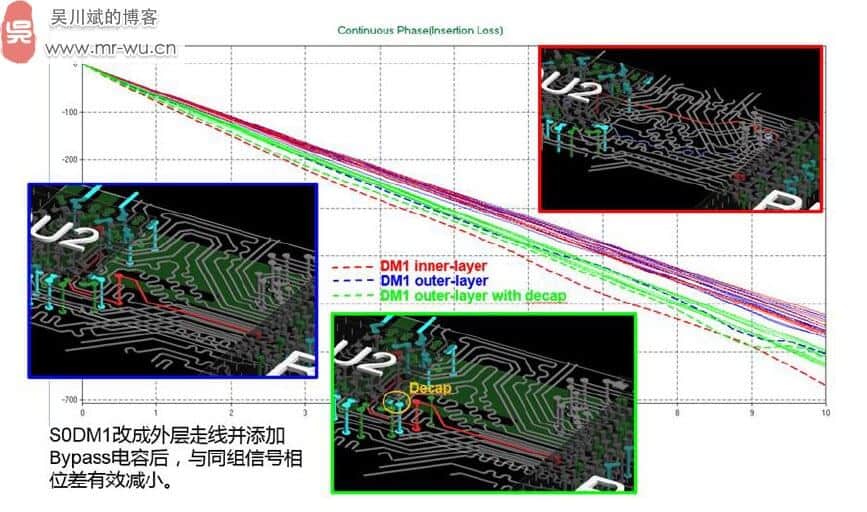

利用插入损耗的Continuous Phase或者Phase Delay功能,还可以分析总线各网络的延时关系。下图是本案例中对S0DM1信号与同组其它信号的Skew进行分析优化的结果。

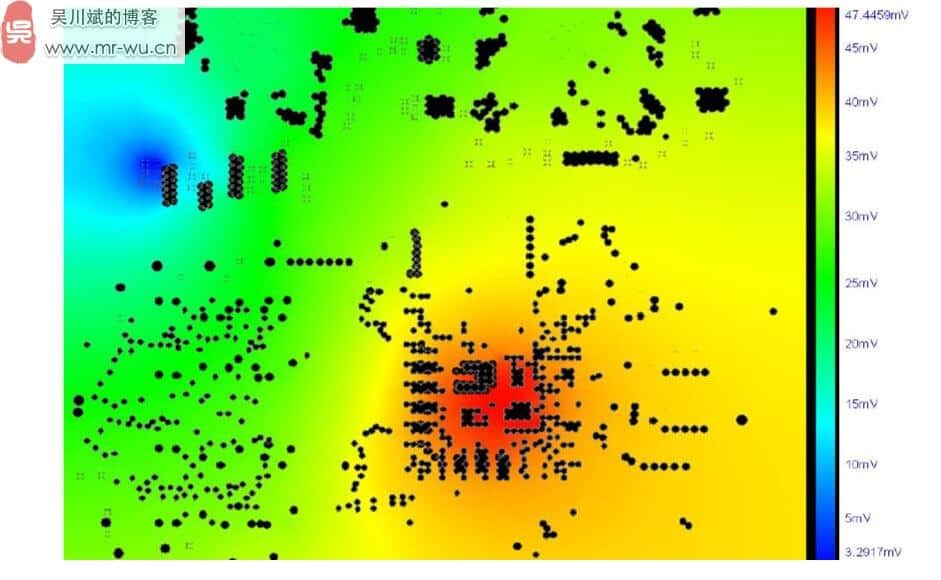

VCC-DRAM电源直流压降仿真结果

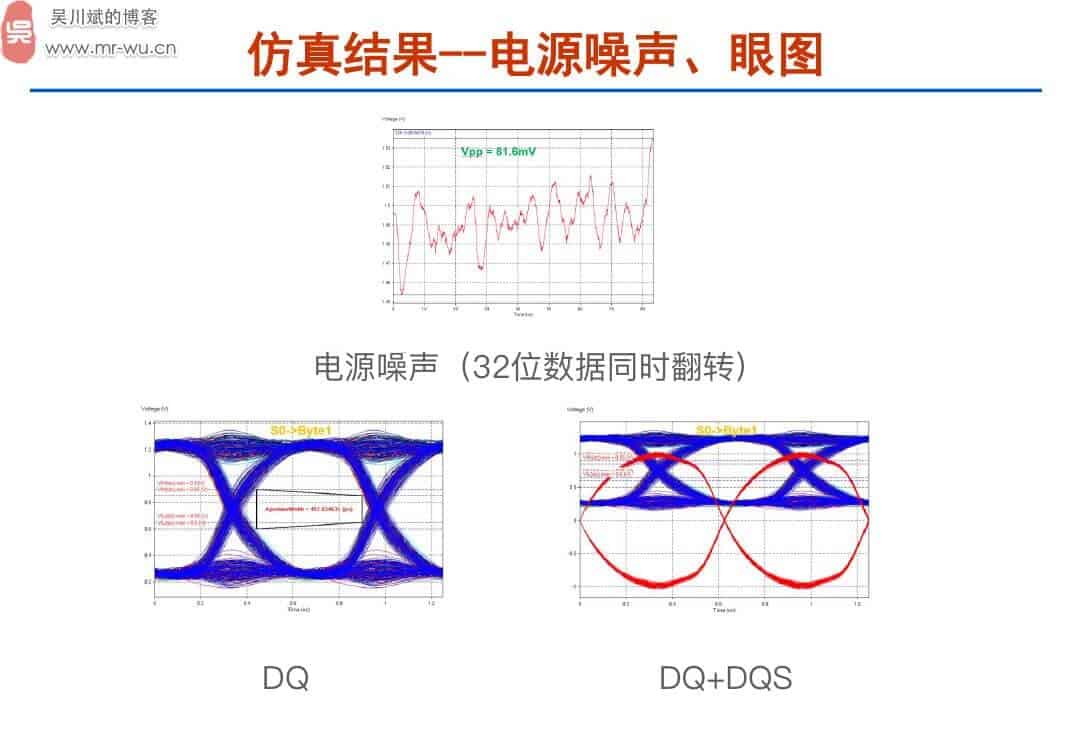

使用100nF*4的封装电容在130MHz存在谐振,且阻抗峰值较高。使用 100nF*2+1nF+2.2nF的封装电容,在100MHz和130MHz位置存在谐振, 但电源阻抗峰值得到一定改善。

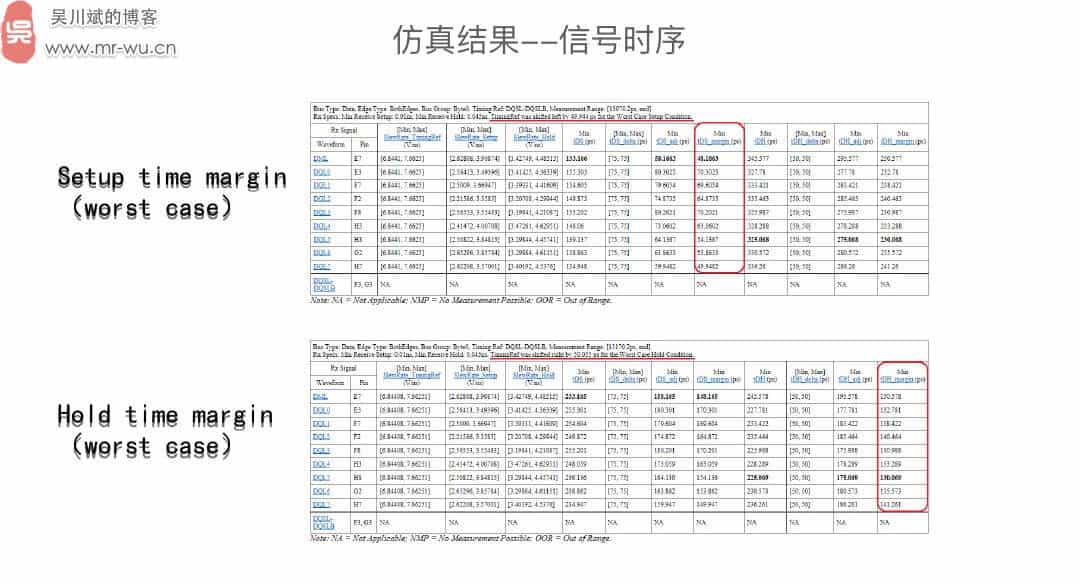

在SystemSI中设置好Controller和Memory的时序参数后,SystemSI会 自动对每个周期的波形进行测量计算并生成仿真报告,从中我们可以 很方便的分析DDR3总线的时序裕量。

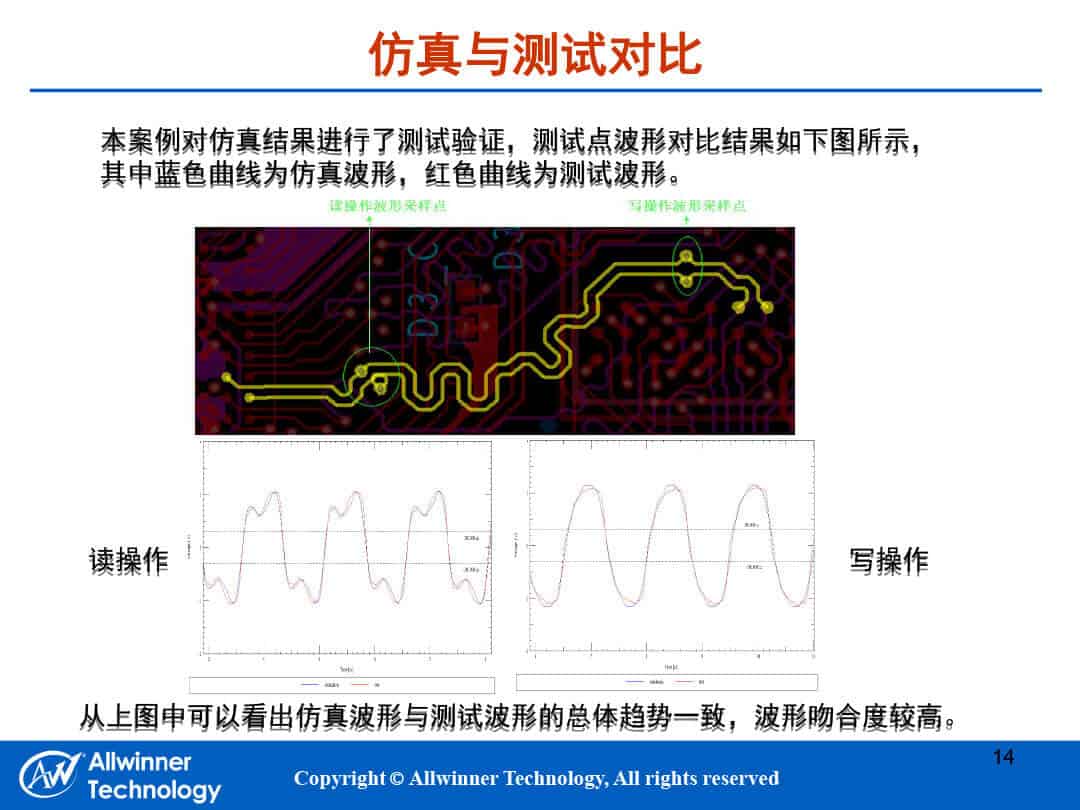

本案例对仿真结果进行了测试验证,测试点波形对比结果如下图所示,其中蓝色曲线为仿真波形,红色曲线为测试波形。

- 效率:Power-aware SI工具里面SystemSI同时仿真DDR3接口32根DQ信 号+4根DM+8根DQS信号,运行256 bit随机码数据,单服务器运行时间 约为6个小时 。同样的case,使用业界同类工具,单服务器运行时间 约为36个小时。基于上面的数据,对于上述DDR3接口信号系统仿真的 例子,SystemSI在单服务器上的仿真速度约为业界同类工具的6倍。

- 精度:通过上面的仿真与测试对比可以得知仿真波形与测试波形的总 体趋势一致,仿真精度高。

- 结论:Candence公司的Power-aware SI工具的仿真结果与实际测试一 致,仿真精度高,可以满足DDRx高速并行信号的需求。仿真效率比业 界同类工具提高6倍以上,可以明显改善DDRx等高速并行信号的设计周期。