cell的传播延时是根据电平转换波形上的某些测量点定义的,使用以下四个变量定义这些测量点

#输入端口下降沿阙值

input_threshold_pct_fall: 50.0;

#输入端口上升沿阙值

input_threshold_pct_rise: 50.0;

#输出端口下降沿阙值

output_threshold_pct_fall: 50.0;

#输出端口上升沿阙值

output_threshold_pct_rise: 50.0;

假设有一个CMOS反相器cell,其输入输出管脚的波形图如下图所示,传播延时是指如下两个值:

- 输出下降沿延时(output fall delay): Tf

- 输出上升沿延时(output rise delay): Tr

从上面的波形图可以看到,Tf指的是从A port上升沿50%的时间点到Z port下降沿50%的点,50%是先前在测量点设定时设置的

Skew between signals

skew指的是多个信号之间在timing上的差值

例如,一个clock tree有500个end points,并且有50ps的skew,这意味着 clock tree起点到最长path终点 与clock tree起点到最短path终点之间的延迟差值是50ps

用下图来区分clock skew和clock latency

图中A是clock tree的起点,B、C、D是三个clock tree的终点

A --> B是一条path,A --> C是一条path,A --> D是一条path

每条path上所花费的时间是clock latency,不同path上的clock latency的差值是clock skew

显式指定clock tree的延迟:

set_clock_latency 2.2 [get_clock BZCLK]

#上升沿和下降沿的latency都是2.2

#也可以使用-fall或-rise选向分别指定不同的latency

显式指定clock skew

set_clock_uncertainty 0.250 -setup [get_clocks BZCLK]

set_clock_uncertainty 0.100 -hold [get_clocks BZCLK]

set_clock_uncertainty为时钟沿的出现指定了一个窗口,时钟边沿时序的不确定性会考虑多个因素,例如时钟周期抖动(jitter)和用于时序验证的额外裕量(slack)

每个实际的时钟源都有一定的抖动量,可以理解成一个可以产生时钟沿的时间窗口

现实中所有的时钟都有一定的抖动量,因此在指定时钟不确定性时应当包含时钟周期抖动

此外在时树实现之前,时钟不确定性还要包括clock skew

即时钟不确定性包括clock skew、时钟周期抖动

hold check和setup check可以指定不同的时钟不确定性,由于hold check的时钟不确定性不需要包含时钟抖动,因此通常为hold check指定较小的时钟不确定性

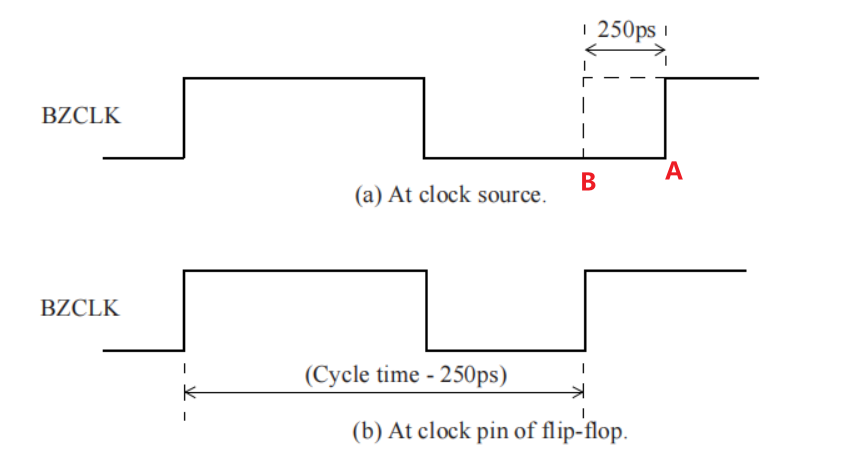

下图是不确定性为250ps时的setup check,图a是时钟源的波形图,图b是触发器时钟端接受到的波形图

在时钟源中,第二个上升沿在A处,因为在setup check中指定了250ps的不确定性,因此对于触发器的时钟端来说,第二个上升沿就有可能出现在B处

set_clock_uncertainty也可以用于建模任何额外的时间裕量,比如design过程中,designer用50ps的时序裕量作为额外的pessimism

通常在实现clock tree之前,要先指定时钟不确定性

时钟不确定性包括:时钟抖动、时钟偏移和额外的pessimism,换句话说,时钟抖动、时钟偏移和额外的pessimism的指定都在set_clock_uncertainty中

set_clock_latency 2.0 [get_clocks USBCLK]

set_clock_uncertainty 0.2 [get_clocks USBCLK]

#200ps的时钟不确定性可能由50ps时钟抖动、100ps时钟偏斜以及50ps额外的pessimism组成

最大和最小时序路径

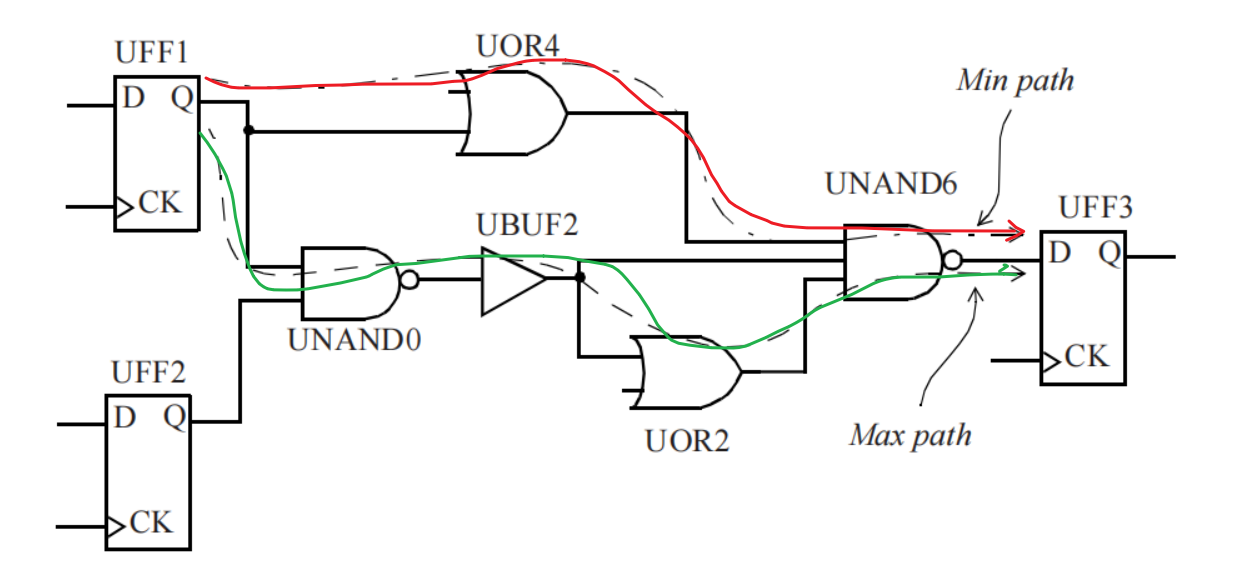

在实际电路中,无论是cell还是net,当逻辑经过时都会产生延迟,通常,一个逻辑从起点到终点可能不止一条逻辑path可以走,如下图所示

可以看到从UFF1/Q到UFF3/D,红色和绿色两条path都可以实现,那么这两条path中,延迟最大的是最大时序路径,延迟最小是最小时序路径

有一点需要强调,最大最小时序路径取决于path上的延迟时间,与path上cell的数量没有直接关系

比如下面这张图

从UFF1/Q到UFF2/D有绿色和蓝色两条path,假设两条path上的net delay相同,绿色path上每个cell的delay为100,蓝色path上每个cell的delay是50

蓝色path上总的delay是50+50+50+net delay,绿色path上总的delay是100+100+net delay

绿色path的delay 比蓝色path上的delay大,因此,绿色path是最大时序路径

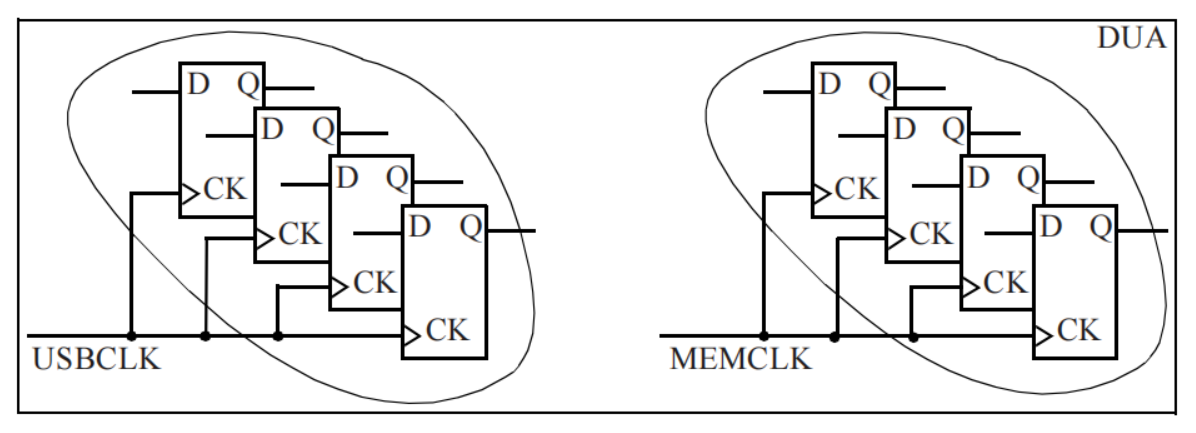

时钟域

由同一时钟驱动的一组触发器称为其时钟域(clock domain)

在一个设计中,可能有多个时钟域,例如,USBCLK驱动了200个触发器,而时钟MEMCLK驱动了1000个触发器,如下图所示。在此示例中,我们称有两个时钟域。

需要关注一个问题:两个时钟域是相关的还是彼此独立的?

时钟域是否相关取决于是否有一条path横跨两个时钟域

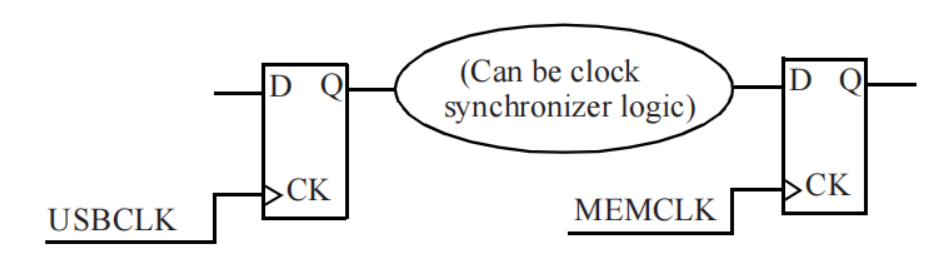

如果存在跨时钟域的data path,则需要判断这些path是否为real path,如下图所示,在USBCLK时钟域下launch一笔数据,在MEMCLK时钟域下capture

如果约束数据在一个时钟周期内通过同步电路,则是real pah,否则是false path

可以使用set_false_path命令指定这是一条false path,从而让工具不去检查这条path

set_false_path -from [get_clocks USBCLK] \ -to [get_clocks MEMCLK]

# 将从USBCLK到MEMCLK的path指定为false path,让工具不用检查这条path的时序