https://blog.csdn.net/hungtaowu/article/details/120703931

UPF与低功耗设计实现实例 -- 附UPF与DC综合脚本

sunvally

sunvally 已于 2022-11-15 17:40:44 修改

已于 2022-11-15 17:40:44 修改 6059

6059 收藏 98

分类专栏: 低功耗设计与验证 文章标签: 硬件工程

版权

收藏 98

分类专栏: 低功耗设计与验证 文章标签: 硬件工程

版权

低功耗设计与验证专栏收录该内容

29 篇文章46 订阅

订阅专栏

低功耗设计与验证专栏收录该内容

29 篇文章46 订阅

订阅专栏

原文链接:https://www.eefocus.com/industrial-electronics/473034

本文摘自《数字集成电路低功耗物理实现技术与 UPF》 孙轶群 [email protected] 国民技术股份有限公司 Nationz Technologies Inc

4.0 低功耗设计实现实例

这里提供一个 DEMO(pl8051_extend_chip),可以使读者更快的理解低功耗设计的基础。下图所示,是该设计的功能结构图:

图 4.1 pl8051_extend_chip 功能结构图

由图 41 可以看出,整个设计主要是由一个 8051 控制器,通过 SFR 总线对其他模块进行控制,U_Des 是一个算法模块,U_Pcu 是功耗控制单元(Power Control Unit)。整个设计都在 Clk 的控制下进行工作,只有 U_Des 工作在 ClkF 下。

这里假设 Clk(28ns)是 ClkF(7ns)的 4 分频时钟,且与 ClkF 同源同向,这样才可以保证 U_Des 控制的正确性。

由于 U_Des 需要在较快的频率下工作,因此需要对 U_Des 进行一些特殊的设计,也就是对整个设计进行低功耗设计,如下所示:

图 4.2 低功耗设计方案示例

上图主要描述以下信息:

- 2 个电压域,TOP 以及 DES_DOMAIN。

- 电源设计外部提供,分 1.2V 的 VDD12 和 1.0V 的 VDD10

- 设计中除 DES 电路几乎所有电路工作在 1.0V 的 VDD 电压域。

- U_Des 由于工作速度要求较高,工作在 1.2V 的VDD12 电压域

DES_DOMAIN,但由于不使用的时候需要关断,以降低静态功耗,因此,通过一组 PowerSwitch 进行控制,控制信号来源为 U_Pcu 的 PcuSfrDatOut[0]输出。该电压域与 TOP 电压域共用 VSS 地信号。

由于 U_Des 电路处于 VDD12 电压域,而 U_Pcu 处于 VDD 电压域,因此需要添加 Level Shifter 进行电平转换。

U_Des 电路输出信号,需要通过一个 Isolation Cell,在关断电源时提供稳定电平,而该电平为 1.2V,因此还需要利用 Level Shifter 转换成 1.0V 电压域信号,Isolation Cell 的 Enable 信号来自于 U_Pcu 模块的 PcuSfrDatOut[1]信号。

U_Des 电路中的寄存器需要使用 Retention Register,save 和 restore 控制信号分别来自于 U_Pcu 输出 PcuSfrDatOut[2]和 PcuSfrDatOut[3]经过 Level Shifter 产生的信号。

Synopsys 公司为低功耗设计提供了一整套的解决方案,即 UPF 设计流程。UPF(Unify Power Format)是一种描述功耗设计思想的文件,Synopsys Galaxy Implementation Platform 只需要读取 UPF 文件,就可以将低功耗设计思路实现,而 Synopsys Discovery Verification Platform 读取 UPF 后,可以对低功耗思路以及最终实现的电路进行验证。

接下来,我们利用 UPF 描述该 DEMO 的功耗设计思路。

4.1 申明电压域以及虚拟电压接口

首先申明电压域,并申明 VDD、VDD12 以及 VSS 等电压端口:

create_power_domain TOP

create_power_domain DES_DOMAIN_domain –elements U_Des

create_supply_port VDD

create_supply_port VDD12

create_supply_port VSS

根据上述指令,工具会识别出如下图所示中画圈的信息,电压域及虚拟电压端口开始出现:

图 4.3 电压域及虚拟电压端口信息

需要注意的是电压端口只不过是虚拟存在的,并不是一定在顶层连接。

4.2 申明电源网络

接着申明每个电压域中的电源网络,建议从顶层往底层进行申明,如首先申明 TOP 的 VSS、VDD:

create_supply_net VDD

create_supply_net VSS

以上语句添加下图中画圈部分:

图 4.4 产生顶层电源网络

接着申明 DES_DOMAIN 的电源网络,但需要注意的是,如果需要插入 Level Shifter,最好是在与其有连接关系的电源域(TOP)同时申请电源线,并连接起来:

create_supply_net VDD12

create_supply_net VDD12 –domain DES_DOMAIN –reuse #DES_DOMAIN 的 VDD12 与 TOP 的 VSS 共用一个网络,因此需要 -reuse

create_supply_net VDD12G

create_supply_net VDD12G –domain DES_DOMAIN -reuse

create_supply_net VSS –domain DES_DOMAIN –reuse

create_supply_net VDD –domain DES_DOMAIN –reuse

以上语句添加下图中画圈部分:

图 4.5 子电路的电源网路申明

然后将电源网络和电源端口连接起来:

connect_supply_net VDD12 –port {VDD12}

connect_supply_net VDD –port {VDD}

connect_supply_net VSS–port {VSS}

以上语句添加下图中画圈部分:

图 4.6 连接电源网络和电源端口

最后为每个电源域申明主电源网络来源,主电源就是该电压域普通逻辑工作使用的电源:

set_domain_supply_net TOP –primary_power_net VDD –primary_ground_net VSS

set_domain_supply_net DES_DOMAIN –primary_power_net VDD12G –primary_ground_net VSS

做完这一步,电源网络申明基本完成。

4.3 添加 Power Switch

这添加 Power Switch 主要是 2 步,第一步创建 Power Switch,第二步 map Power Switch。可以参看以下脚本进行:

Power Switch

create_power_switch des_sw

-domain DES_DOMAIN

-input_supply_port {in VDD12}

-output_supply_port {out VDD12G}

-control_port {des_po U_Pcu/PcuSfrDatOut[0]}

-on_state {state_on in {!des_po}}

-off_state {OFF {des_po}}

map_power_switch des_sw

-domain DES_DOMAIN

-lib_cell HDRSIHVTD0

create_power_switch 和 map_power_switch 在综合时只会检查语法,不会有实际效果,但在综合时将该 UPF 指令读入系统,可以由 DC 输出相应的 UPF 给 Synopsys 的 PR 工具,PR 工具可以自动识别这些指令,到时才会真正添加 Power Switch。2 句命令的结果示意在下图画圈中:

图 4.7 添加 Power Switch Cell

4.4 建立电源状态表格(Power State Table, PST)

在 Power Switch 插入以后,需要对电压域的有效电压,以及不同电压域之间的关系进行设置,同时建立电压分布及关断的情景(scenarios),可以用于静态电压分析、仿真等。

建立电源状态表格,可以参看以下脚本:

add_port_state VDD –state {LV 1.0} #VDD 是 1.0V,属于低电压域(LV)状态

add_port_state VDD12 –state {HV 1.2} #VDD12 是 1.2V,属于高电压域(HV)状态

add_port_state des_sw/out –state {HV 1.2} #Power Switch 输出是 1.2V,属于高电压域(HV)状态

-state {OFF off}#关闭状态(OFF),无电压(off)

add_port_state VSS –state {ON 0.0} #VSS 处于常开状态(ON),电压 0V

create_pst design_pst –supplies {VDD VDD12 VDD12G} #建立一个 PST,由 3 个电源状态不同组成

add_pst_state design_work –pst design_pst –state {LV HV HV} #design_work 状态下,三组电源都开

add_pst_state stand_by –pst top_pst –state {LV HV OFF} #stand_by 状态下,des_sw/out 输出电源为关闭状态

需要注意 add_pst_state 的 -state 括号里的描述顺序,必须与 create_pst 的 -supplies 里一致,选择的状态必须与 add_port_state 的 -state 里描述的一致才可以。

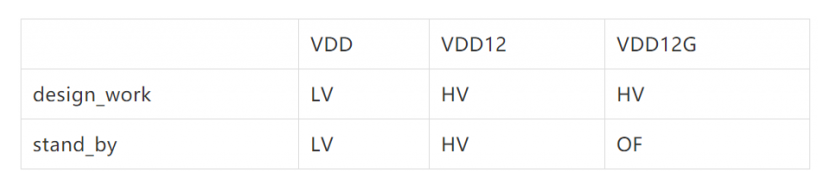

这样就建立了下表所示的 PST,design_pst:

由此建立了 PST,分析工具或仿真工具就知道需要对哪些状态进行分析了。

4.5 插入 Isolation Cell

下面需要为 DES_DOMAIN 输出给 TOP 的输出信号添加 Isolation Cell。脚本如下所示:

Isolation Cell

set_isolation des_iso_out

-domain DES_DOMAIN

-isolation_power_net VDD12 -isolation_ground_net VSS #隔离后只有 VDD12 供电

-clamp_value 1 #关电后输出逻辑 1

-applies_to outputs #对于所有输出添加

set_isolation_control des_iso_out

-domain DES_DOMAIN

-isolation_signal U_Pcu/PcuSfrDatOut[1]

-isolation_sense high #控制信号为高时 ISO 有效

-location self # Isolation Cell 添加在 DES_DOMAIN 里面

这样就可以产生如下图所示画圈部分电路:

图 4.8 插入 Isolation Cell

4.6 替换 Retention Register Cell

接着需要使用 Retention Register Cell 将 DES_DOMAIN 中在关断电源后需要保留数据的寄存器替换为 Retention Register Cell,可以使用如下脚本:

Retention Register

set_retention des_ret -domain DES_DOMAIN

-retention_power_net VDD12G -retention_ground_net VSS #retention_power_net 是关电的 Power,表示需要保持 VDD12G 电源域的数据

set_retention_control des_ret -domain DES_DOMAIN

-save_signal {U_Pcu/PcuSfrDatOut[2] high}

-restore_signal {U_Pcu/PcuSfrDatOut[3] low}

map_retention_cell des_ret

-domain DES_DOMAIN

-lib_cell_type RSDFCSD1

#RSDFCSD1 是带有异步置位的 Retention Register Type,可以从 lib 文件中 retention_cell 属性中看到。

根据以上描述,会按照下图画圈示意图描述电路:

图 4.9 替换 Retention Register Cell

4.7 插入 Level Shifters

插入 Level Shifters 是根据 PST 的定义进行,根据 PST 定义看来,DES_DOMAIN 和 TOP 之间需要插入 Level Shifters,其中 DES_DOMAIN 输出的 pin(Isolation Cell 的输出)需要插入 H->L 的 Level Shifter,而其输入则需要插入 L->H 的 Level Shifter。

插入 Level Shifter 在 Compile 过程中自动进行,也可以利用 UPF 命令 set_level_shifter 定义插入的规则。

插入 Level Shifter 后产生的电路变化示意图如下图画圈处所示:

图 4.10 插入 Level Shifters

4.8 UPF Demo

######################

CREATE POWER DOMAIS

######################

create_power_domain TOP

create_power_domain DES_DOMAIN -elements U_Des

#######################

TOPLEVEL CONNECTIONS

#######################

#VDD

create_supply_port VDD

create_supply_net VDD -domain TOP

create_supply_net VDD -domain DES_DOMAIN -reuse

connect_supply_net VDD -port VDD

#VSS

create_supply_port VSS

create_supply_net VSS -domain TOP

create_supply_net VSS -domain DES_DOMAIN -reuse

connect_supply_net VSS -port VSS

#VDD12

create_supply_port VDD12

create_supply_net VDD12 -domain TOP

create_supply_net VDD12 -domain DES_DOMAIN -reuse

connect_supply_net VDD12 -port VDD12

#VDD12G

create_supply_net VDD12G -domain DES_DOMAIN

create_supply_net VDD12G -domain TOP -reuse

#####################

PRIMARY POWER NETS

#####################

set_domain_supply_net TOP -primary_power_net VDD -primary_ground_net VSS

set_domain_supply_net DES_DOMAIN -primary_power_net VDD12G -primary_ground_net VSS

###################

DES_DOMAIN SETUP

###################

Power Switch

create_power_switch des_sw

-domain DES_DOMAIN

-input_supply_port {in VDD12}

-output_supply_port {out VDD12G}

-control_port {des_po U_Pcu/PcuSfrDatOut[0]}

-on_state {state_on in {!des_po}}

-off_state {OFF {des_po}}

map_power_switch des_sw

-domain DES_DOMAIN

-lib_cell HDRSIHVTD0

Isolation Cell

set_isolation des_iso_out

-domain DES_DOMAIN

-isolation_power_net VDD12 -isolation_ground_net VSS

-clamp_value 1

-applies_to outputs

set_isolation_control des_iso_out

-domain DES_DOMAIN

-isolation_signal U_Pcu/PcuSfrDatOut[1]

-isolation_sense high

-location self

Retention Register

set_retention des_ret -domain DES_DOMAIN

-retention_power_net VDD12G -retention_ground_net VSS

set_retention_control des_ret -domain DES_DOMAIN

-save_signal {U_Pcu/PcuSfrDatOut[2] high}

-restore_signal {U_Pcu/PcuSfrDatOut[3] low}

map_retention_cell des_ret

-domain DES_DOMAIN

-lib_cell_type RSDFCRD1

Level Shifter

set_level_shifter des_ls_lh

-domain DES_DOMAIN

-applies_to inputs

-threshold 0.1

-rule low_to_high

-location parent

set_level_shifter des_ls_hl

-domain DES_DOMAIN

-applies_to outputs

-threshold 0.1

-rule high_to_low

-location parent

#####################

ADD PORT STATE INFO

#####################

add_port_state VDD -state {LV 0.84}

add_port_state VDD12 -state {HV 1.08}

add_port_state VSS -state {ON 0.0}

add_port_state des_sw/out -state {HV 1.08}

-state {OFF off}

#############

CREATE PST

#############

create_pst design_pst -supplies {VDD VDD12 VDD12G VSS}

add_pst_state design_work -pst design_pst -state {LV HV HV ON}

add_pst_state stand_by -pst design_pst -state {LV HV OFF ON}

4.9 DC UPF Flow Script Demo

source -e …/scr/synopsys_dc.setup

source -e …/scr/ variable.tcl

set_clock_gating_style -min ${CG_MIN_BITWIDTH} -max_fanout ${CG_MAX_FANOUT}

-sequential_cell ${CG_SEQ_CELL}

-positive_edge_logic ${CG_POS_CELL_LIST}

-negative_edge_logic ${CG_NEG_CELL_LIST}

-control_point ${CG_CONTROL_POINT}

-control_signal ${CG_CONTROL_SIGNAL}

-setup ${CG_SETUP_VALUE} -hold ${CG_HOLD_VALUE}

set_operand_isolation_style -logic adaptive

set_operand_isolation_slack 0.1

set_svf N E T L I S T P A T H {NETLIST_PATH}NETLISTPATH{top}${VER}.svf

read_verilog ${RTL_INCLUDE}

current_design $top

uniquify

link

load_upf ${SCRIPT_PATH}power.upf

set auto_insert_level_shifters_on_clocks all ;#can be added in backend flow

set_voltage 1.08 -object_list {VDD12 VDD12G}

set_voltage 0.84 -object_list VDD

set_voltage 0.0 -object_list VSS

source -e -v ${SCRIPT_PATH}timing.tcl

#M1~M9 are avaliable, M1 will be used by STD

#set_ignored_layers -min_routing_layer M4

set_ignored_layers -max_routing_layer M7

report_ignored_layers > R E P O R T P A T H {REPORT_PATH}REPORTPATH{top}_ignored_layers.rpt

set_clock_gating_check -setup ${CG_SETUP_CHECK} -hold ${CG_HOLD_CHECK} [all_clocks]

set_fix_multiple_port_nets -feedthroughs -outputs -buffer_constant

set_attr -type string tcbn90lphpwc0d70d9_pg.db:tcbn90lphpwc0d70d9 default_threshold_voltage_group SVT_LS_LH

set_attr -type string tcbn90lphphvtwc0d70d9_pg.db:tcbn90lphphvtwc0d70d9 default_threshold_voltage_group HVT_LP_LH

set_attr -type string tcbn90lphpwc0d7_pg.db:tcbn90lphpwc0d7 default_threshold_voltage_group SVT_LV

set_attr -type string tcbn90lphphvtwc0d7_pg.db:tcbn90lphphvtwc0d7 default_threshold_voltage_group HVT_LV

set_attr -type string tcbn90lphpwc_pg.db:tcbn90lphpwc default_threshold_voltage_group SVT

set_attr -type string tcbn90lphphvtwc_pg.db:tcbn90lphphvtwc default_threshold_voltage_group HVT

set_attr -type string tcbn90lphphvtcgwc_pg.db:tcbn90lphphvtcgwc default_threshold_voltage_group HVT_CG

set_attr -type string tcbn90lphphvtwc0d90d9_pg.db:tcbn90lphphvtwc0d90d9 default_threshold_voltage_group HVT_ISO

set_attr -type string tcbn90lphphvtwc0d90d7_pg.db:tcbn90lphphvtwc0d90d7 default_threshold_voltage_group HVT_LS_HL

set_attr -type string tcbn90lphpwc0d90d7_pg.db:tcbn90lphpwc0d90d7 default_threshold_voltage_group SVT_LS_HL

check_mv_design -verbose

compile_ultra -scan -no_autoungroup -no_boundary_optimization

change_names -rules verilog -hierarchy

write -format ddc -hierarchy -output D D C P A T H {DDC_PATH}DDCPATH{top}_noscan${VER}.ddc

write -format verilog -hierarchy -output N E T L I S T P A T H {NETLIST_PATH}NETLISTPATH{top}_noscan${VER}.v

set write_sdc_output_lumped_net_capacitance false

set write_sdc_output_net_resistance false

write_sdc -version 1.5 S D C P A T H {SDC_PATH}SDCPATH{top}_cons${VER}.sdc

check_design > R E P O R T P A T H {REPORT_PATH}REPORTPATH{top}_check_design_postcomp.rpt

report_area > R E P O R T P A T H {REPORT_PATH}REPORTPATH{top}_area.rpt

check_mv_design –verbose > R E P O R T P A T H {REPORT_PATH}REPORTPATH{top}_check_mv_design.rpt

report_constraint -all > R E P O R T P A T H {REPORT_PATH}REPORTPATH{top}_all_vio.rpt

report_clock_gating -gating_elements >> R E P O R T P A T H {REPORT_PATH}REPORTPATH{top}_icg.rpt

report_operand_isolation -verbose -isolated > R E P O R T P A T H {REPORT_PATH}REPORTPATH{top}_opiso.rpt

report_threshold_voltage_group > R E P O R T P A T H {REPORT_PATH}REPORTPATH{top}_VT.rpt

report_threshold_voltage_group -verbose >> R E P O R T P A T H {REPORT_PATH}REPORTPATH{top}_VT.rpt

save_upf N E T L I S T P A T H {NETLIST_PATH}NETLISTPATH{top}${VER}_dc.upf #upf’ for next part of flow

5.0 总结

本文从 CMOS 电路功耗原理入手,针对不同工艺尺寸下数字集成电路的低功耗物理实现方法进行描述,并通过一个例子介绍了 Synopsys UPF(Unified Power Format)文件对低功耗设计的描述原理。UPF 是 Synopsys 公司提出的一种对芯片中电源域设计进行约束的文件格式。通过与 UPF 格式匹配的 Liberty 文件,UPF 约束文件可以被整套 Galaxy 物理实现平台的任何一个环节直接使用,并将设计者的电源设计约束传递给设计工具,由工具完成设计的实现工作,从而实现整套数字集成电路低功耗物理实现的流程。