05-主存储器

概述

主存中存储单元地址的分配

12345678H 这个数据如何在主存储器中进行存储

两种方式 大端(大尾)方式 和小端(小尾)方式

大端方式:高位字节存储数据的低位,低位字节存储数据的高位

小端方式:低位字节存储数据的低位,高位字节存储数据的高位

设地址线为24根 按地址寻址 2^24=16MB

若字长为16位 按字寻址 8MW

若字长为32位 按字寻址 4MW

主存的技术指标

- 存储容量 主存存放二进制代码的总位数

- 存储速度

- 存取时间,即存储器的访问时间

- 分为读出时间和写入时间

- 存储器的带宽 每秒能读出或写入的数据的位数

半导体芯片简介

半导体存储芯片的基本结构

包括存储矩阵、译码驱动、读写电路、地址线(单向)、数据线(双向)、片选线、读/写控制线

利用地址线和数据线计算芯片容量

地址线(条) 数据线(条) 芯片容量

10 4 1K x 4位

14 1 16K x 1位

13 8 8K x 8位

片选线 $\overline{CS}$ $\overline{CE}$

读/写控制线

有的是一路信号 $\overline{WE}$ 上面的横线表示低电平有效(低电平写,高电平读)

有的是两路信号 $\overline{OE}$ (允许读) $\overline{OE}$ (允许写)

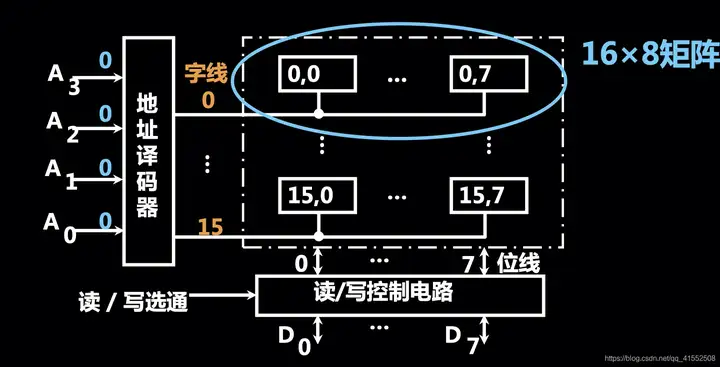

半导体存储芯片的译码驱动方式

线选法

用一根字选择线直接选中存储单元,每个字都对应着一根地址线

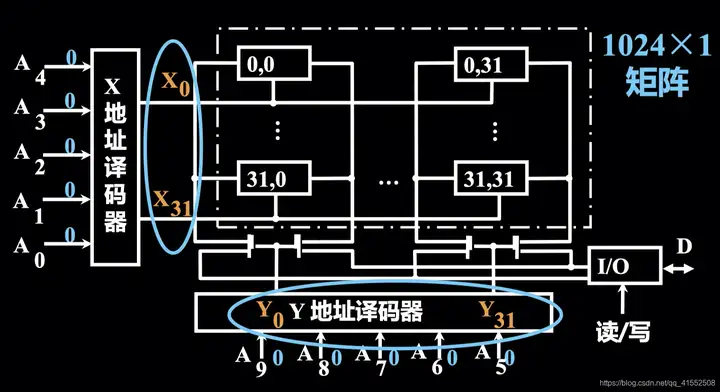

重合法

地址译码器分为X地址译码器(行译码器)和Y地址译码器(列译码器)地址线的规模从O(n)缩减为了O($\sqrt{n}$)

随机存取存储器(RAM)random-access memory

静态RAM(SRAM)

建议看下视频,讲的比较清楚(https://www.bilibili.com/video/BV1WW411Q7PF?p=26&vd_source=3c88fb7dae36f53e6a15081fb7cf9ff8)

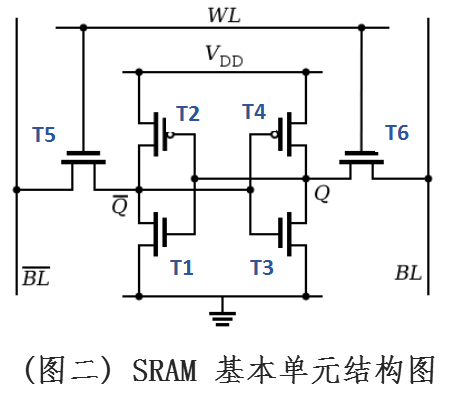

Static Random-Access Memory,即静态随机存取存储器,是随机存取存储器的一种。所谓的“静态”,是指这种存储器只要保持通电,里面储存的数据就可以恒常保持,不须周期性地刷新。每个SRAM基本单元是由六个晶体管电路所构成 (如图二)。每一bit储存在由4个晶体管(T1, T2, T3, T4)所构成两个交叉耦合的反相器中,另外两个晶体管(T5, T6)是用于储存基本单元到读写位线(Bit Line)的控制开关。SRAM功耗取决于它的访问频率,当访问频率增加时,其功耗相对增加,如果用高频率访问SRAM,其功耗比得上DRAM。反之,在系统空闲状态时,SRAM功耗则可以忽略不计。

实现SRAM 01信号存储的元件是双稳态触发器(有两个输出信号,一端与另一端值刚好相反)

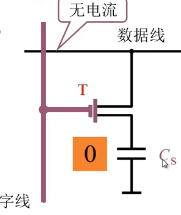

动态RAM(DRAM)

保存0和1的原理是什么?

使用电容存储,电容中如果存储了电量,认为其信号为1,否则认为其信号为0

基本单元电路的构成是什么

有两种基本单元电路,一种是3管动态RAM,一种是单管动态RAM

对单元电路如何读出写入?

读出与原存信息相反

读入与输入信息相同

典型的芯片的结构是什么样子?(Intel1103 三管,Intel4116 单管)

动态RAM芯片如何进行读出和写入操作?

动态RAM为什么要刷新?刷新方法

因为动态RAM是使用电容进行存储电荷,电容会漏电,或一段时间电量就漏没了,所以需要刷新

对动态RAM进行刷新,只和行地址有关,每次刷新都会刷新一行的数据

1)集中式刷新 刷新的时间集中在一段时间内(假设存取周期为0.5微秒,动态RAM刷新周期2毫秒,对于128x128的芯片 死区 0.5*128=64微秒 死时间率为 128/4000 =3.2%)

2)分散刷新(假设存取周期为1微秒,对于128x128的芯片 无死区 但是过度刷新)

3)异步刷新(分散刷新与集中刷新相结合)(对于128x128的存储芯片,存取周期假设为0.5微秒,若每隔15.6微秒刷新一行 每行每隔2ms刷新一次 死区为0.5/15.6 如果将刷新安排在指令译码阶段,不会出现死区)

静态RAM和动态RAM的比较

||DRAM|SRAM|

|-|-|-|-|

|存储原理|电容|触发器|

|集成度|高(一个晶体管一个电容)|低(六个晶体管)|

|芯片引脚|少|多|

|功耗|低(仅电容充放电)|高(有3个关子一直处于导通状态)|

|价格|低|高|

|速度|慢|快|

|刷新|需要刷新|不需要刷新|

DRAM用做主存

SRAM用做缓存

只读存储器(ROM)read-only memory

ROM的发展

- 早期的只读存储器--在厂家出厂就写好了内容

- 改进1--用户可以自己写--一次性

- 改进2--可以多次写--要能对信息进行擦除

- 改进3--电可擦除--特定设备

- 改进4--电可擦除--直接连接到计算机

1.掩模ROM(MROM)

行列选择线交叉处有MOS管为1

行列选择线交叉处无MOS管为0

2.PROM(一次性编程)

行线和列线之间通过熔丝连接

熔丝断 为0

熔丝未断 为1

3.EPROM(多次编程)

N型沟道浮动栅MOS电路

使用紫外线全部擦洗

D端加正电压 形成浮动栅 S与D不导通为0

D端不加正电压 不形成浮动栅 S与D导通为1

4.EEPROM(多次编程-电可擦写)

电可擦写

局部擦写

全部擦写

5.Flash Memory(闪速型存储器)

EPROM 价格便宜 集成度高

EEPROM 电可擦洗重写

Flash Memory比EEPROM快 具备RAM功能

CPU和存储器的连接

1.存储器容量的扩展

位扩展

字扩展

同时扩展

2.存储器与CPU的连接

- 地址线的连接

- 数据线的连接

- 读/写命令线的连接

- 片选线的连接

- 合理选择存储芯片

ROM 系统程序存储及配置信息

RAM 用户的程序区,系统程序运行区

芯片数量尽量少,片选信号尽量简单 - 其他 时序、负载

存储期的校验

汉明码的纠错过程

形成新的检测位Pi,其位数与增添的检测位有关

如增添3位(k=3),新的检测位为P4P2P1

以k=3为例,Pi的取值为

P1=1异或3异或5异或7

P2=2异或3异或6异或7

P4=4异或5异或6异或7

对于按"偶校验"配置的汉明码不出错时P1=0,P2=0,P4=0

提高访存速度的措施

- 采用高速器件

- 采用层次结构 Cache-主存

- 调整主存结构

主存结构

1.单体多字系统 例如cpu能读取的单个数据长度是16位,存储器每次读取的数据长度设为64,一次读取cpu可以使用4次,降低了读取耗时,但是在写入的时候会有问题,写入16位数据,会将另外的48位数据也写进去

2.多体并行系统

1)高位交叉 顺序编址 适合存储器容量的扩展,不适合解决访存速度的问题

2)低位交叉 各个体轮流编址,用于存储器带宽和访问速度的提升

3.高性能训处新编

1)SDRAM(同步DRAM) 在系统时钟的控制下进行读出和写入

2) RDRAM 主要解决 存储器带宽 问题

3) 带cache的DRAM 有利于猝发式读取