@

目录一、总线简图

先来说一下总线的物理原理。

如下:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-4Uvngig2-1673767564844)(D:\Typora图片\image-20230115095910112.png)]](/i/ll/?i=692ea63de24a40bb9c611d5e9ef7d85f.png)

地址总线:

CPU可以通过地址总线给主存或者打印机、硬盘发送地址信息。

数据总线:

CPU可以通过数据总线,给其他部件进行数据传输。

控制总线:

CPU可以通过控制总线给其他的部件发送控制信号,控制的是电信号。

❓为什么数据总线或者地址总线可以并行传递很多bit的信息?

因为每个总线可能由很多根信号线组成。

比如现在将数据线拆解一下:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-SSJBvTMF-1673767564846)(D:\Typora图片\image-20230115100827341.png)]](/i/ll/?i=7fd06bfb19ef488cad254a799a5c304f.png)

可能一个数据总线里面包含了四根信号线。

如果想并行传递32bit的数据,那么数据总线内部就可以包含32根信号线。

现在CPU想给主存发送4bit(比如0101)的数据,这就意味着CPU只要给数据总线的四根线上分别加上高低电平信号。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-UD9YgTql-1673767564846)(D:\Typora图片\image-20230115101047020.png)]](/i/ll/?i=6dfffd4b44dd4313bab4ad456018f01f.png)

0101的数据可以被主存、硬盘或打印机接收。

只要高低电平信号加在数据线之后,由于所有的硬件部件都是连接在数据总线上的,所以所有的部件都可以通过数据总线来接收CPU发送给它们的信号。

虽然平时都是说一根总线,但是总线里面是包含多根信号线的。

比如上面的例子,4根信号线组成一根总线,所有硬件部件都可以通过这根总线传递数据。

具体包含几根信号线,这要看具体需求。

如果想并行传递32bit,那么就可以让总线包含32根信号线。

上图可以并行发送4bit的数据,同一时刻只能有一个部件发送数据,但是可以有多个部件接收数据。

这个很好理解,比如CPU发送了一个低电平信号,而硬盘发送了一个高电平信号,这时候总线上的信号就会有冲突,其他部件就不知道接收哪一个信号了,就乱套了。所以同一时刻只能有一个部件发送数据。

比如CPU发送了一个0101的信号,由于其他部件都直接和总线相连,那么都可以从连接点检测到高低电平信号,所以都可以接收到CPU发送的数据。所以同一时刻可以有多个部件接收数据。

如下图:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-38n4Vy9C-1673767564846)(D:\Typora图片\image-20230115102601573.png)]](/i/ll/?i=4aa18112dca24519b0cb3f9e2083dd88.png)

主存和CPU可以通过主板上的总线进行数据交互。

这种总线的设计思想,可以让电脑扩充硬件部件变得很容易。只要留出对应的接口,那么就可以在主板上扩充其他硬件部件。

接下来我们逐步学习下面的内容:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-pcPfUPtj-1673767564847)(D:\Typora图片\image-20230115103549729.png)]](/i/ll/?i=cf3bcd1cc73a455bb7831f765d85a096.png)

总线仲裁:

比如两个设备都想要使用总线,那么这两个设备都往总线上发送数据,是会造成冲突的。

因为总线上连接了很多设备,这些设备都想占用总线发送数据,那么应该将总线的使用权交给谁呢?

操作与定时:

当我们将总线的使用权分配给某个设备之后,这个设备就可以通过总线与其他设备进行数据交互了。那么数据交换又是如何进行的?

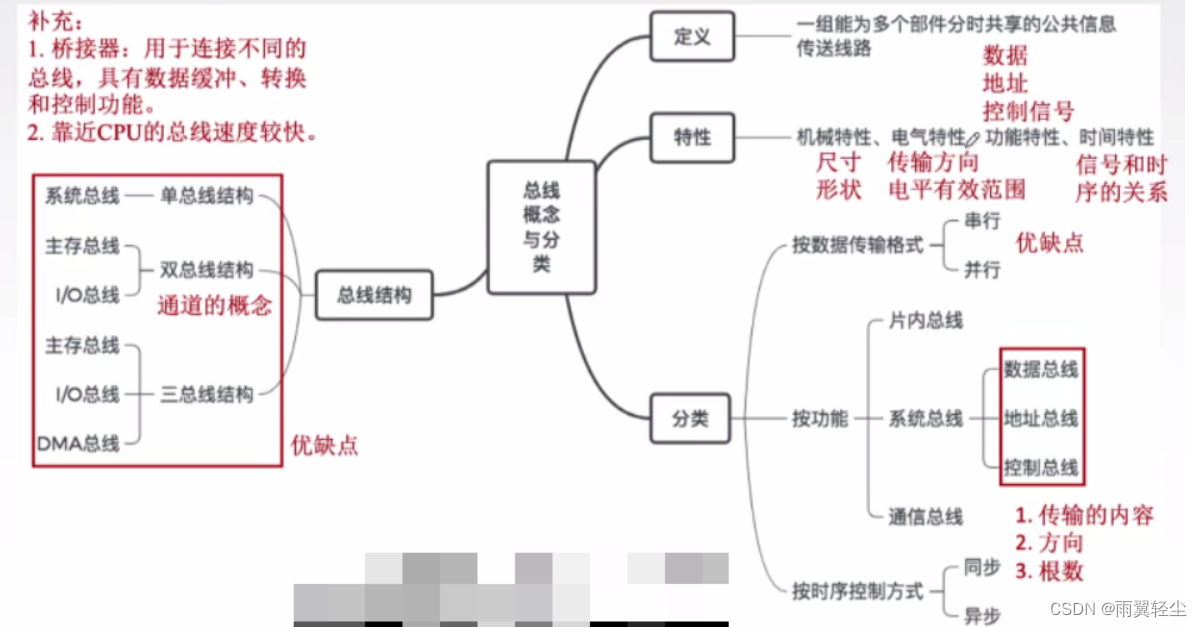

二、概念与分类

1.总线定义

总线:总线是一组能为多个部件分时共享的公共信息传送线路。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-oWMXDZou-1673767564847)(D:\Typora图片\image-20230115103831859.png)]](/i/ll/?i=bc958a3d88cb4c1ea8032ff24d17f995.png)

上半部分是CPU,CPU可以通过一组系统总线,和主存、I/O设备进行数据交互及控制信号的收发。

所有的硬件部件都是通过系统总线来进行相互的控制和数据的传送。

❓ 为什么要用总线?

早期计算机外部设备少,大多采用分散连接方式,不易实现随时增减外部设备。

比如CPU只需要和特定的外部设备“纸带机”进行数据交互,这时候专门建立一条数据传送线路即可。

随着外部设备的增多,如果还是采用分散连接,每增加一个设备,就专门建立一条数据传送线路,这明显不利于增减外部设备。

为了解决主机和外部设备之间连接的灵活性,计算机的结构从分散连接发展为总线连接。

如果要增加外部设备,只需要将它连接在总线上即可。如果想要移除,只需要将它与总线断开即可。

2.总线特点

(1)分时

同一时刻只能由一个部件往总线上发送信息。

如果多个部件想往总线发送信息,那么就需要在不同时刻使用总线。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-DqZAVrGm-1673767564848)(D:\Typora图片\image-20230115105120359.png)]](/i/ll/?i=059cb339543e4eb9b31ae3198efa1240.png)

(2)共享

所有的硬件部件都是共享总线的。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-g3Eh6EUk-1673767564848)(D:\Typora图片\image-20230115105109614.png)]](/i/ll/?i=46efccb215d54350b5bf5e2f4ed14147.png)

3.总线特性

当设计总线的时候,需要关注下面的特性。

①机械特性

尺寸、形状、管脚数、排列顺序

②电气特性

传输方向:比如CPU可以通过地址总线告诉主存此次要读或者写的地址,那么只能是CPU向主存传递,不能是反方向。又比如CPU要通过数据总线往主存里面写数据或者读数据,所以对于数据总线来说,传递方向就是双向的。

有效的电平范围:比如规定0v~0.5v是低电平,4.8v~5.2v是高电平。那么只有电平信号落在这个范围里面,才认为电平信号是有效的。

③功能特性

需要关注每根传输线的功能,是地址线还是数据线还是控制线。

④时间特性

信号的时序关系,比如请求使用总线的信号什么时候发出。

4.总线的分类

可以从不同的维度,对总线进行分类。

如下:

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-OmJYO2zf-1673767564849)(D:\Typora图片\image-20230115110505209.png)]](/i/ll/?i=af5848b7eaba404d90afd2f0202b92a3.png)

(1)按数据传输格式

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-JHymL2nd-1673767564849)(D:\Typora图片\image-20230115110647868.png)]](/i/ll/?i=767693436f2f470bb59393b79fae6899.png)

①串行总线

每次只能传送一位

比如设备A往设备B发送一个信号(比如1011),只能一个比特一个比特地发送数据。B也只能一个比特一个比特地接收数据。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-p0eaq0cu-1673767564849)(D:\Typora图片\image-20230115111008468.png)]](/i/ll/?i=4d3d1eb8273547739b0d14d321c1b557.png)

USB这种总线规范,每次只会传送一个bit的数据。

<1> 优点

只需要一条传输线,成本低廉广泛应用于长距离传输。

应用于计算机内部时,可以节省布线空间。

一根传输线抗干扰能力强,在进行长距离数据传输的时候,数据不容易发生跳变。

<2> 缺点

在数据发送和接收的时候,要进行拆卸和装配。

还要考虑串行-并行转换的问题。比如通过USB给电脑发送数据,是1个比特1个比特地发送数据,但是CPU不可能是1个比特1个比特地接收。虽然是串行地给电脑发送数据,但是这些数据还要进行转换之后,通过并行的方式,多个bit同时送给CPU。

②并行总线

每次可以传送多位

比如设备A可以并行向设备B发送多个比特的数据。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-J9oluFAH-1673767564850)(D:\Typora图片\image-20230115111441720.png)]](/i/ll/?i=80a04b4693994c848c9f4079d1069cf9.png)

可以看出,CPU与主存之间传送数据的数据线就是并行总线。

数据总线可以并行传送32bit位或者64bit等的数据。

<1> 优点

总线的逻辑时序比较简单,电路实现起来比较容易。

<2>缺点

信号线数量越多,占用更多的布线空间。

远距离传输成本高。

由于工作频率较高时,由于线之间距离较近,所以并行的信号线之间会产生严重干扰,对每条线等长的要求也越高,所以无法持续提升工作频率。

所以,并行总线的工作频率不会特别高,这就可能导致在实际信息传送的速度上甚至不如串行总线。

并不是说并行总线可以同时发出多个比特数据就注定比串行总线快。

因为各个信号线之间的干扰问题,导致并行总线在发送数据的时候,发送频率是有上限的,不能特别高。而串行总线不存在信号线之间的干扰问题,所以发送频率就可以做的很高。

并行总线一定比串行总线快,这句话是错的!

(2)按总线功能

①片内总线

片内总线是芯片内部的总线。

它是CPU芯片内部寄存器与寄存器、寄存器与ALU之间的公共连接线。

②系统总线

系统总线是计算机系统内各功能部件(CPU、主存、I/O接口)之间相互连接的总线。

按系统总线传输信息的内容不同,又分为3类:数据总线、地址总线和控制总线。

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Zmqf1oI2-1673767564850)(D:\Typora图片\image-20230115135231264.png)]](/i/ll/?i=eb499a4d419d4c699f6b2fe3a1a70466.png)

数据通路表示数据流经的路径(逻辑上);数据总线是承载的媒介(承载数据流动的物理媒介)。同样,地址总线也可以当作数据通路的一个物理媒介。

下面来详细讲解系统总线。

<1> 数据总线(Data Bus)

双向,传输各个功能部件之间的数据信息。

包括指令和操作数。

位数(根数)和机器字长、存储字长有关。

如果数据总线的宽度和机器字长一致,那么CPU就可以通过一次数据读入取得CPU一次可以处理的数据。

如果数据总线的宽度和存储字长一致,每次主存的读或者写操作,只需要数据总线传一次即可。如果数据总线的宽度只有存储字长的一半,那么要取出一个存储字就需要数据线传两组数据。

<2>地址总线(Address Bus)

单向,传输地址信息,包括主存单元或I/O端口的地址。

地址总线一定是单向的,由CPU发送信号,来表示CPU想要读或者写的设备。

CPU可以通过地址总线发出地址信号,来指明它想访问的主存单元的地址是多少。

也可以通过地址总线来指明它想访问的输入输出设备是哪一个。

位数(根数)与主存地址空间大小及设备数量有关。

地址总线的宽度(位数)需要与主存地址空间大小一致,如果主存和I/O设备采用统一编址的方式,那么除了主存空间之外,还需要考虑设备数量。

比如,主存对应的地址空间是0~n,输入设备1的编号是n+1,输出设备2的编号是n+2。

这种情况下,地址总线的宽度就至少需要能够表示0~n+2的地址信息。

<3> 控制总线(Control Bus)

一根控制线传输一个信号。

有出:CPU送出的控制命令。

有入:主存(或者外设)返回CPU的反馈信号。

控制总线包含多根控制线,每一根控制线负责传输一个控制信号。

对于单根控制线来说,这种控制信号的传输方向都是单向的。

对于整个控制总线来说,它的传输方向可以是出也可以是入。

因为有的控制线由CPU发出,发给主存或者其他设备。有的控制线是CPU用来接收其他的硬件设备给它返回的控制信号的。

③通信总线

通信总线是用于计算计系统之间或计算机系统与其他系统(比如远程通信设备、测试设备)之间信息传送的总线。

通信总线也称为外部总线。也可以理解为网线。

(3)系统总线的结构

这里重点讲解系统总线的结构。

①单总线结构

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-e6RsJAot-1673767564851)(D:\Typora图片\image-20230115141405699.png)]](/i/ll/?i=11db064da13f480e80b36b385e6e6c19.png)

只会在计算机内部设置一组系统总线,CPU、主存、I/O设备都连接在系统总线上。

所有的功能部件都是通过这一组系统总线来进行数据的传输。

注意,这里的系统总线是一组,包含了数据总线、地址总线和控制总线。

<1> 优点

结构简单,成本低,易于接入新的设备。

<2> 缺点

带宽低,各个部件对总线的使用应该是互斥的,同一时刻只能有一个功能部件获得总线的使用权,所以会有多个设备来争用总线的控制权。

不支持并发传送这里的并发应该理解为并行,就是同一时刻只能有两组部件之间传送数据,不可能是多组部件之间同时通过总线来传递数据。

CPU和主存对数据的读写速度快,而外部设备对数据传输速度很慢,所以这些慢速的设备接在可以传输快速数据的总线上,总线的性能就显得相当浪费,屈才了。

②双总线结构

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-Pbpy6qa3-1673767564852)(D:\Typora图片\image-20230115143205698.png)]](/i/ll/?i=735a7a4ab723446e93e4b61404681a52.png)

为了解决单总线结构带来的问题,我们这里让CPU和主存连接在主存总线上,还有一个通道。

何为通道?通道可以理解为阉割版的小CPU,只用于管理I/O设备。(通道可以缓和CPU与I/O设备之间的速度矛盾)

I/O总线和通道之间是双向箭头,所有的I/O设备(不管快还是慢)都可以通过这个通道与CPU进行间接交互。

由于通道对信息的处理速度很快,所以它也可以连接在主存总线上,与CPU进行交互,将主存总线充分利用起来。

通道要运行的程序,放在主存里面。通道可以通过主存总线从主存中取出想要执行的程序。

I/O总线由于连接的是各种慢速的I/O设备,所以性能可以稍微慢一点。

主存总线可以支持突发传送。CPU每指明一个地址,可以从主存中读出一个字的信息,由于主存中保存的信息很多时候是需要被连续访问,比如需要顺序执行指令序列。

因此,CPU指明一个地址之后,如果能从主存中读出多个字的数据,那么系统的效率就能更高。

所以,突发传送可以送出一个地址,收到多个连续的数据,就是上面描述的情况。

主存总线--快

I/O总线--慢

③三总线结构

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-7VgsklmQ-1673767564852)(D:\Typora图片\image-20230115145609897.png)]](/i/ll/?i=0a0df38c3e144c8fb19be6166c880702.png)

我们可以看到三组总线。

-

主存总线用来连接CPU和主存这两个高速部件之间的交互,

-

DMA总线用来连接主存和某一些快速的I/O设备。

比如高速外设磁盘机,对磁盘的数据读写,是以块为单位,每次读或者写一个磁盘块。

如果一个磁盘块的大小是4kB,我们让磁盘与主存通过DMA总线交换数据,就可以很快完成一整块数据的传递。

这么做的好处是,CPU不需要通过慢速的I/O总线和磁盘机进行数据的交互。

而是可以先将CPU需要的数据从磁盘机子通过DMA读入主存,然后CPU就可以通过快速的主存总线中取走这些数据。

这样可以缓和CPU和磁盘机之间的速度矛盾。

- I/O总线:相比于DMA总线,I/O总线的速度更慢,CPU可以直接通过I/O总线和某些慢速的I/O设备交互。

比如键盘每次只输入一个字符,键盘输入的速度相较于CPU处理的速度来说要慢得多 。

<1> 优点

这种结构可以使某些高速设备的性能得到提升,因为这些高速设备可以通过更快的DMA总线和主存之间进行数据交互。

低速设备与CPU直接连接,因此这些低速设备还可以更快响应CPU发出的命令。

之前说的双总线结构,I/O设备还要通过通道的处理才能与CPU进行交互。所以,双总线结构中CPU对I/O设备的响应会慢一点。

<2> 缺点

系统工作效率低。

因为三个总线在同一时刻只能有一个总线工作。

④四总线结构

![[外链图片转存失败,源站可能有防盗链机制,建议将图片保存下来直接上传(img-voOXJFNg-1673767564853)(D:\Typora图片\image-20230115150500854.png)]](/i/ll/?i=375564d77119448b9e776bf58fcdc8a6.png)

-

CPU总线:用于连接CPU和cache。

-

系统总线:用于连接主存。

-

高速总线:用于连接显卡之类快速的设备。

-

扩充总线:用于外部设备的扩充。比如连接USB设备。

CPU总线速度最快,其次是系统总线和高速总线,然后是扩充总线。

由于不同总线之间有速度差异,所以要增加一个中间设备桥接器,作用是连接不同的总线,具有数据缓冲、转换(比如串行数据并行地发给CPU)和控制功能(总线仲裁,要将总线使用权交给哪一个设备)。

注:考试不考四总线,但是这是现代计算机经常使用的结构。

三、总结