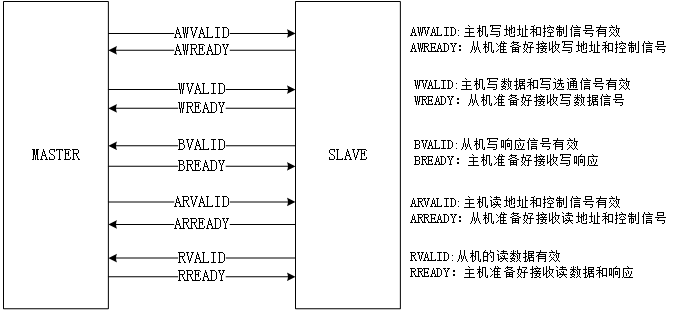

1. VAILD 和READY 传输方向

2. VAILD 和READY依赖关系

前面说到AXI的五个通道是独立的,但通道间必须保持一定的约定关系:

写回复必须在一次写事务的最后一个写数据之后

读数据必须在接收到读地址信号之后

通道间握手必须满足一定的依赖关系

2.1 读通道

读传输的依赖关系也可以参考上图,其中,单头箭头表示其指向的信号可以在箭头起始信号置起之前或之后置起,也就是说被指向的信号不依赖起始信号;双箭头表示其指向的信号必须在箭头起始信号置起之后置起,也就是说被指向的信号必须依赖起始信号。

1.主机不可以等待从机置起ARREADY以后,来决定是否置起主机的ARVALID,即主机发起ARVALID不依赖ARREADY;

2.从机可以等待(也可以不等待)主机发起ARVALID后再发起ARREADY,即从机发起ARREADY不依赖主机ARVALID;从机可以等待主机置起ARVALID之后置起ARREADY,也可以在主机置起ARVALID之前置起ARREADY

3.从机必须等待主机置起ARVALID 和从机置起ARREADY 之后,才可以置起RVALID,因为要在正确接收到读地址后才能返回数据;

从设备只有在输出有效读数据时才能使能RVALID信号,同时在主设备的RREADY信号有效后的第一个时钟上升沿必须保持有效。即使从设备只有一个读数据源,它也必须在收到数据请求时才令RVALID信号有效。

4.从机在发起RVALID之前不用等待主机发起RREADY,即从机发起RVALID不依赖RREADY;

5.主机可以等待(也可以不等待)从机发起RVALID后再发起RREADY,即主机发起RREADY不依赖从机RVALID;主机可以等待从机置起RVALID之后置起主机的RREADY,也可以在从机置起 RVALID 之前置起主机的RREADY

2.2 写通道

图中WVALID上面的†代表WVALID的发起还依赖WLAST。

对于写传输来说,在写地址和写数据通道上,主机是发送方,从机是接收方;在写响应通道,主机是接收方,从机是发送方,这时的依赖关系是:

1.主机不可以等待从机的AWREADY和WREADY,来置起主机的AWVALID和WVALID,即相互之间不依赖;

2.从机在发起AWREADY/WREADY之前可以等待(也可以不等待)主机发起AWVALID/WVALID,即从机发起READY不依赖主机VALID;

从机可以等待主机置起AWVALID和WVALID之后置起从机的AWREADY,也可以在主机置起AWVALID和WVALID之前置起从机的AWREADY

从机可以等待主机置起AWVALID和WVALID之后置起从机的WREADY,也可以在主机置起AWVALID和WVALID之前置起从机的WREADY

3.从机必须等待WVALID/WREADY/WLAST都发起了,才可以置起BVALID,因为BRESP要在最后一个写数据收到后才能发起;

4.从机不可以等待主机置起BREADY之后再置起BVAILD,即从机发起BVALID不依赖BREADY;

5.主机在发起BREADY之前可以等待(也可以不等待)从机BVALID发起,即相互之间不依赖;主机可以等待从机置起BVALID之后置起BREADY,也可以在从机置起BVALID之前置起BREADY

上面听起来有点像绕口令,其实记住一个大原则就好:发起方不能挑事,接收方有自主权。

在AXI4和AXI5中,写传输增加了额外的从机置起 BVALID 信号所需的依赖,从机必须等待AWVALID,AWREADY,WVALID和WREADY。比起AXI3,BVALID还要依赖于AWVALID和AWREADY。从机要等写地址和写数据都完成以后才可以返回写响应,这在道理上是对的。但是,一般而言,写数据会在写地址前完成。

VALID/READY握手机制是AMBA中一个很重要的机制。正是因为有了这个机制,发送方和接收方都有能力控制传输。协议中花费了大量篇幅来描述VALID/READY。

PS.为什么第一条规则很重要?举个例子,如果主机在发起VALID之前等待从机发起READY,而从机定义的是在发起READY之前等待主机发起READY,这样系统就会陷入死锁。

READY 信号比VAILD 信号先到达的情况

READY 信号先到达:READY 信号很自由,可以等待 VALID 信号到来再做响应,但也完全可以在 VALID 信号到来前就置高,表示接收端已经做好准备了。READY 信号与 VALID 不同,接收方可以置起 READY 之后发现:其实我好像还挺忙,然后拉低 READY 信号。只要此时 VALID 信号没有置起,这种操作是完全可以。

VAILD信号比READY信号先到达的情况

VALID 信号先到达:发送方 VALID 信号早早就到了,这时还不到 T2 时刻,并带来了新鲜的数据(数据通道),地址或者控制信息(地址通道)。但过了 T2 也没见到接收方的 READY 信号。原来是接收方还忙着,可能上一次的数据还没存完,还堵在数据通路上,忙过了 T2 才来。好吧,那也行,T3 时刻传输完成。在这种情况下,接收方通过 READY 信号控制了传输速度,反压了发送速度。

协议规定:VALID 信号一旦置起就不能拉低,直到此次传输完成。对于接收方编程来说,检测到 VALID 信号置起,如果系统正忙,完全可以让发送方等待,发送方在完成传输之前都不会置低 VALID 信号,不需要考虑发送方撤销传输的可能。

协议另外规定:发送方不能在置起 VALID 信号之前就光等待 READY 信号。

从总线接口编程的角度理解:READY 信号可能先到达,如下图的情况。但是发送方编程时,不能依赖 READY 信号先到达的情况。不能将 READY 信号置高作为置高 VALID 的条件,比如将 READY 信号通过组合逻辑生成 VALID 信号。

换句话说,发送方准备发送,置起 VALID 信号是完全主动的过程。接收方按照协议可以依赖发送方,但如果此时发送方也依赖接收方,就会造成死锁的情况,所以协议在这里规定了 VALID 信号的主动性。

VAILD信号和READY信号同时到达的情况

3.同时到达:同时到达就很简单,等到下一个时钟上升沿 T2,传输就这么轻松愉快地完成了,一个时钟周期里就完成了。

VAILD信号与READY信号同时到达的情况

协议建议 AW/AR READY 信号(这里 AW/AR 指的是读写地址通道的 READY 信号)的默认电平为高电平。若默认电平为低,则每次传输至少需要 2 个周期才能完成,第一个周期置高 VALID 信号,第二个周期从机才会置高 READY 信号。相当于每次传输增加 1 个周期时间开销,这在某些情况下会对传输效率有较大的影响。

标签:发起,主机,从机,VALID,信号,READY,AXI From: https://www.cnblogs.com/lanlancky/p/17093464.html