一、GT的概念

Xilinx FPGA的GT意思是Gigabyte Transceiver。通常称呼为Serdes、高速收发器。GT在xilinx不同系列有着不同的产品,从7系列到UltraScale系列分别有GTP、GTX、GTZ、GTH、GTY和GTM。不同GT整体结构上类似,为了支持越来越高的line rate,在细节上有着不同的差异。

Blog:FPGA Xilinx 高速串行收发器横向比较_搞FPGA开发的Tony老师的博客-CSDN博客_xilinx高速串行收发器![]() https://blog.csdn.net/wuyanbei24/article/details/118310132 对Xilinx GT各系列进行了横向的比较,本文章主要以UltraScale系列里面的GTH为例做介绍:

https://blog.csdn.net/wuyanbei24/article/details/118310132 对Xilinx GT各系列进行了横向的比较,本文章主要以UltraScale系列里面的GTH为例做介绍:

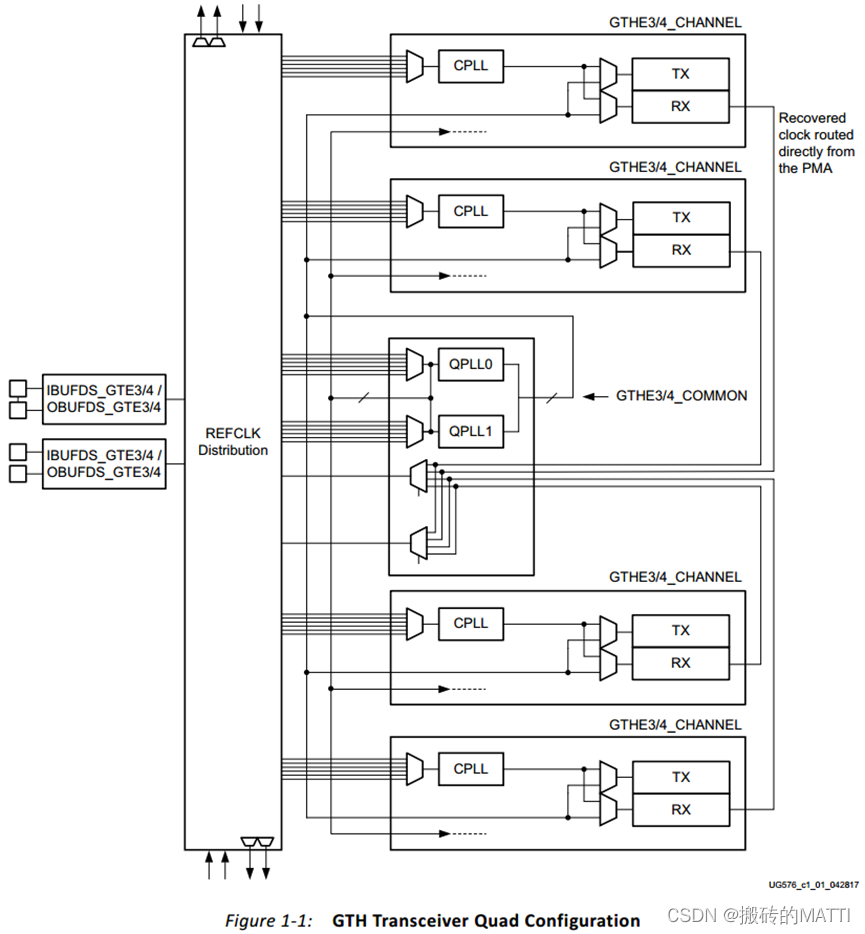

二、GT Quad

Xilinx FPGA中的GT资源以Quad为单位

一个GT Quad包含一个GTHE3/4_COMMON 和 4个 GTHE3/4_CHANNEL。

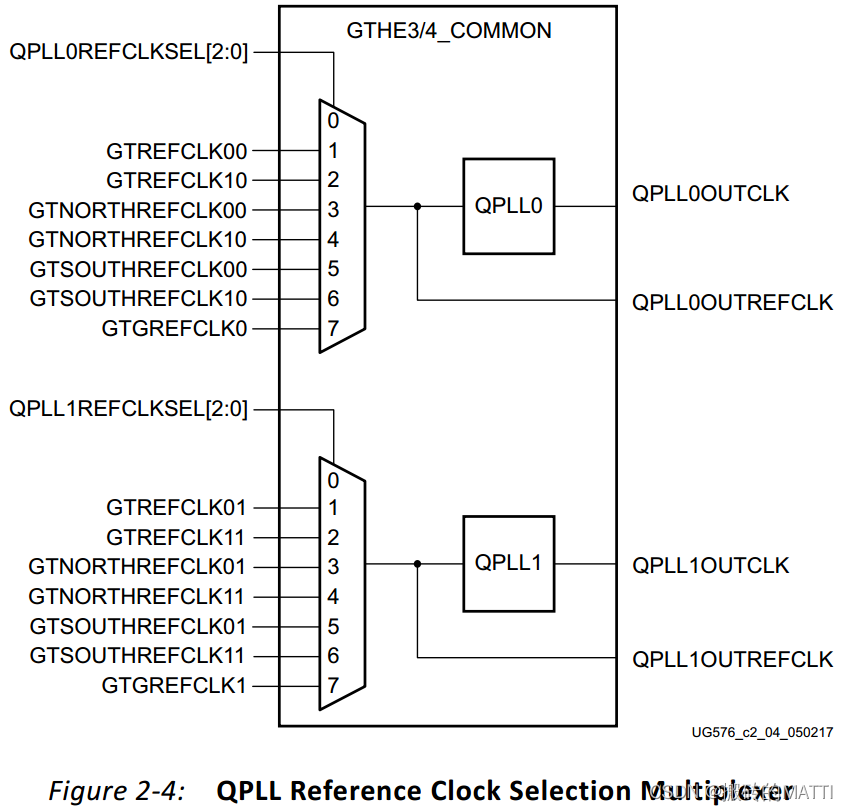

每个GTHE3/4_COMMON包含两个QPLL,在设计中,只有需要使用QPLL时,才需要例化GTHE3/4_COMMON。

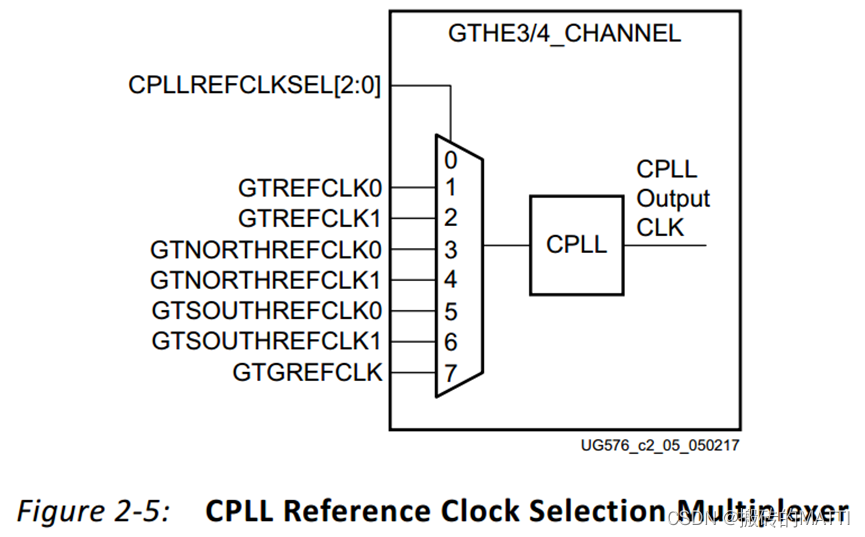

每个GTHE3/4_CHANNEL包含一个CPLL和一个transmitter和一个reciever

Reference Clock Selection and Distribution

一个GT Quad包含一个GTHE3/4_COMMON 、 4个GTHE3/4_CHANNEL、2对专用外部参考时钟pin、专用参考时钟routing。每个transceiver都需要例化对应的GTHE3/4_CHANNEL,但只有需要使用高性能QPLL时才需要例化GTHE3/4_COMMON。

通常Quad(Q(n))的参考时钟可以由其他Quad(最多上/下2个相邻Quad)的输入管脚输入

三、GT Channel

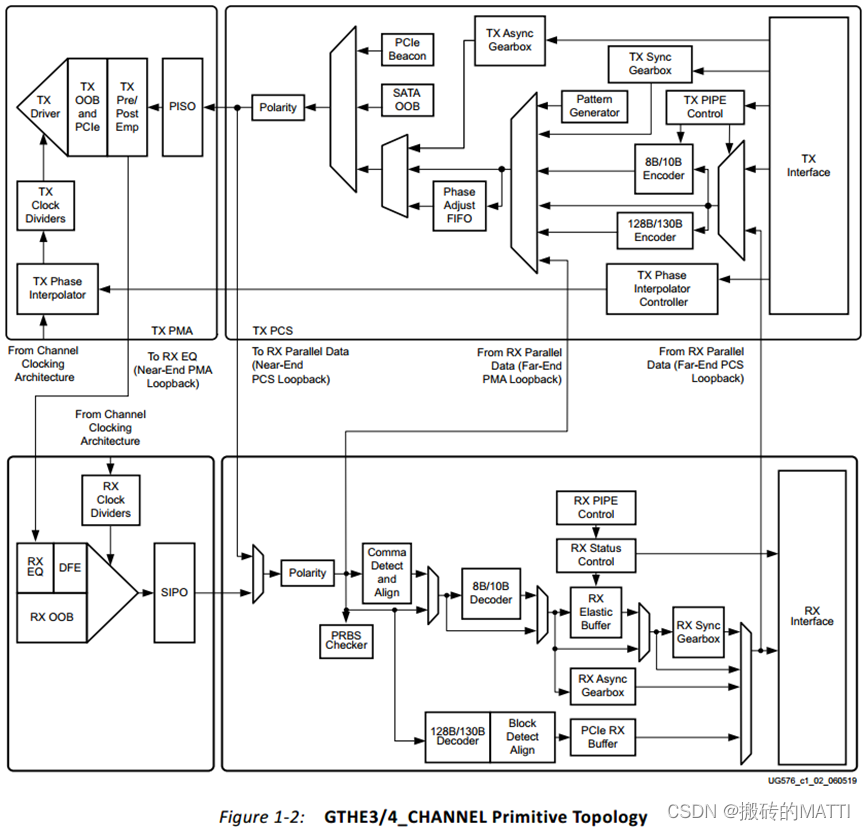

整个GT channel可以分为两层:

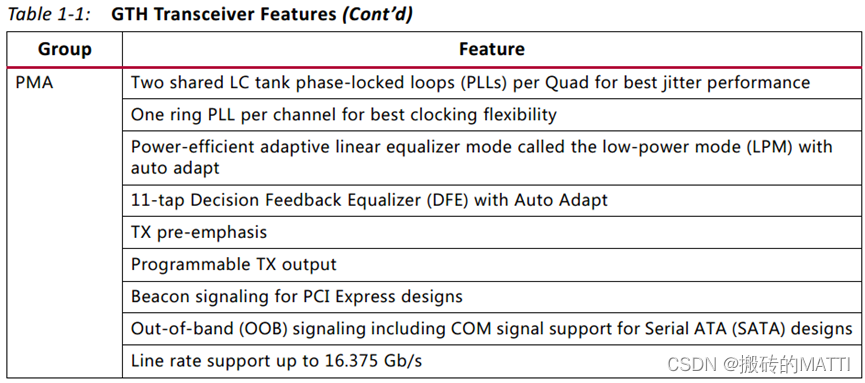

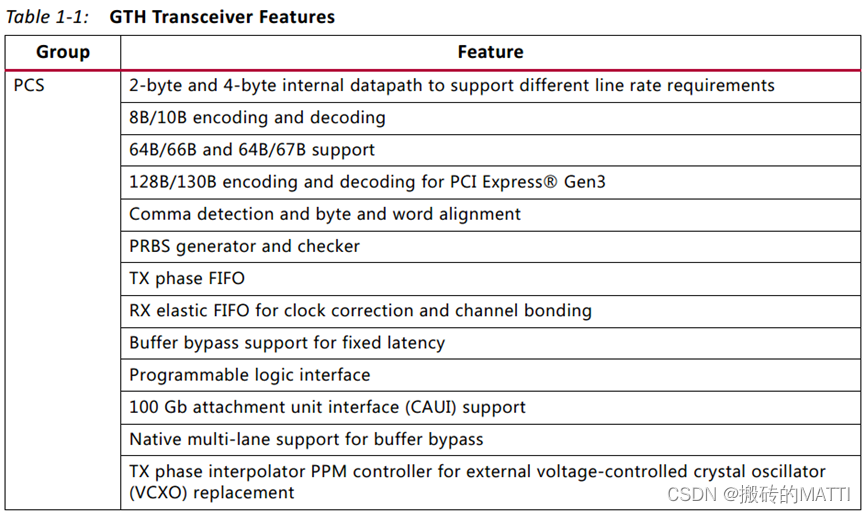

PMA:Physical Media Attachment,物理媒介附加层

PCS:Physical Coding Sublayer,物理编码子层

下面根据收发链路分别讲解:

3.1 Transmitter

3.1.1 TX Interface

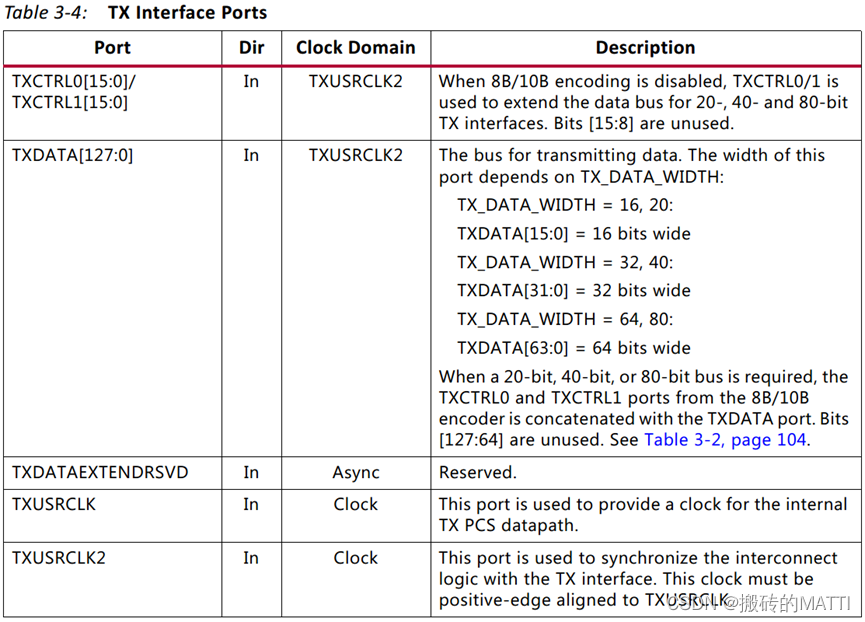

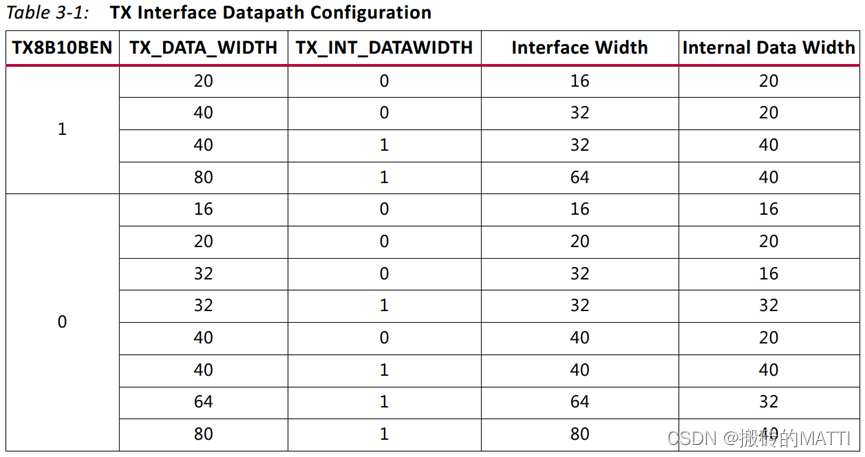

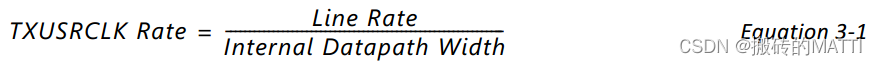

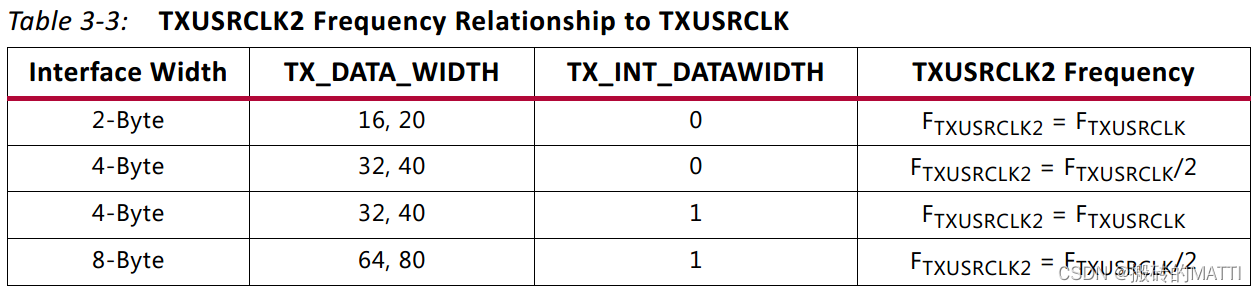

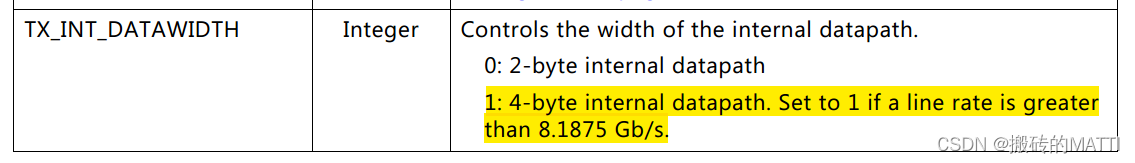

TX Interface分成内部数据位宽和FPGA接口位宽,其中内部数据归属于TXUSRCLK时钟域,FPGA接口数据归属于TXUSRCLK2时钟域,而内部数据位宽支持2byte/4byte,FPGA接口数据位宽支持2byte/4byte/8byte,因此,决定了TXUSRCLK和TXUSRCLK2有一定的时钟倍数关系,TXUSRCLK和TXUSRCLK2的时钟倍数关系如下表所示,其中TX_INT_DATAWIDTH属性设置为“0”,表示内部数据位宽为2byte,如果设置为“1”,则表示内部数据位宽为4byte

线速率大于8.1875Gb/s的时候TX_INT_DATAWIDTH应当置1

3.1.2 TX 8B/10B Encoder

8B/10B的编码理论参考blog:

8B/10B Encode/Decode详解![]() https://www.cnblogs.com/YINBin/p/11011232.html 8B/10B编码的目的1是保证数据有足够的切换提供给时钟恢复电路(CDR),2提供一种将数据对齐到字的方法,3.同时线路可以保持良好的直流平衡。为什么要做直流均衡,参考blog:Serdes高速收发器和CDR技术

https://www.cnblogs.com/YINBin/p/11011232.html 8B/10B编码的目的1是保证数据有足够的切换提供给时钟恢复电路(CDR),2提供一种将数据对齐到字的方法,3.同时线路可以保持良好的直流平衡。为什么要做直流均衡,参考blog:Serdes高速收发器和CDR技术![]() https://blog.csdn.net/qq_16423857/article/details/110135690

https://blog.csdn.net/qq_16423857/article/details/110135690

3.1.3 TX Gearbox(速率变换箱)

8B/10B编码使得带宽利用率80%。一些高速数据速率协议使用64B/66B编码来减少8B/10B编码的开销,同时保留编码方案的优点。TX Gearbox提供了对64B/66B和64B/67B编码支持(header和payload的combining)。TX Gearbox支持2字节、4字节和8字节接口定义,但是数据scrambing是在FPGA逻辑内实现的。

3.1.4 TX Buffer

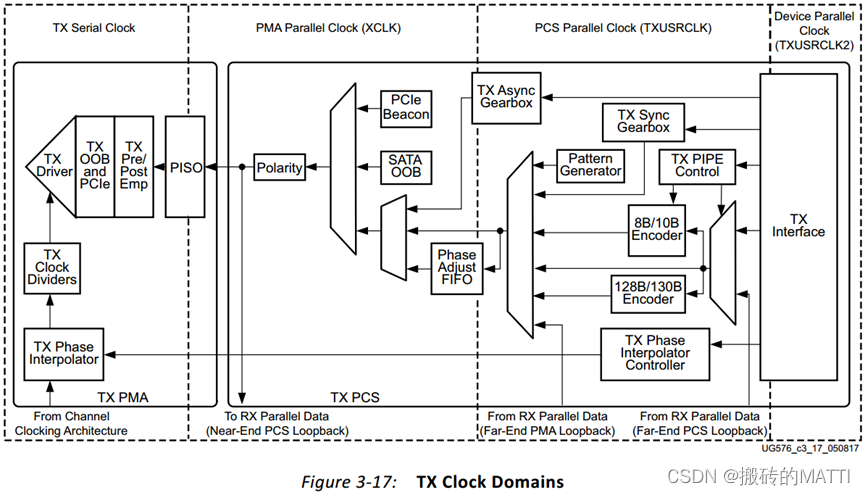

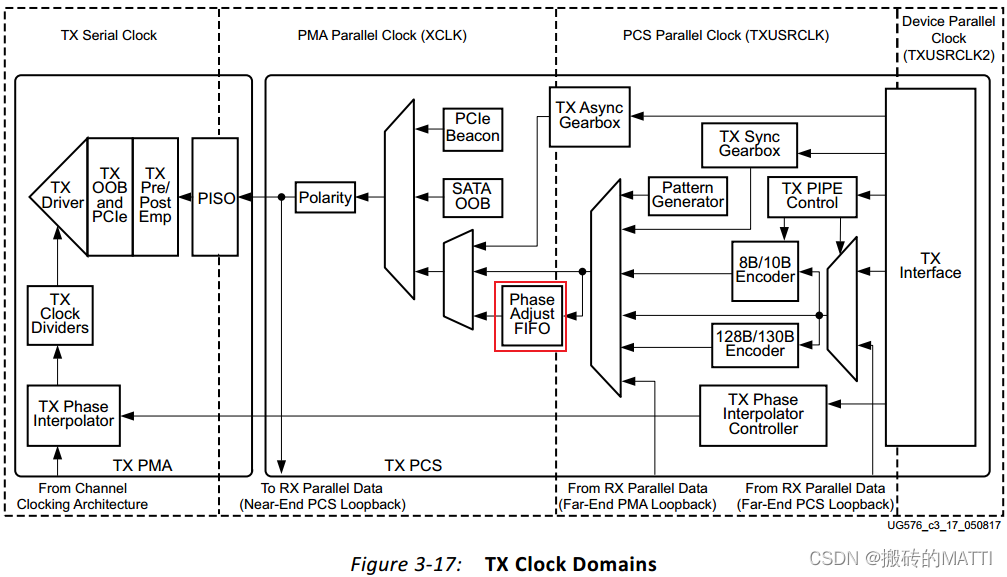

为了解发送的TXBuffer的作用,首先得搞清楚TX发送端的时钟域,TX发送端的时钟域如图所示。

图中红色方框就是TXBuffer, TX Buffer连接着两个不同的时钟域XCLK和TXUSRCLK,在发送端的PCS子层内部包含两个时钟域,XCLK(PMA并行时钟域)TXUSRCLK时钟域,为了数据发送的稳定,XCLK和TXUSRCLK必须是速率匹配,相位差可以消除的,TX Buffer主要用于匹配两时钟域的速率和消除两时钟域之间的相位差。

TX Buffer也可以被旁路,TX发送端提供了一个相位对齐电路,可以解决XCLK和TXUSRCLK时钟域之间的相位差,但是TX_XCLK_SEL需设置为“TXUSR”来保持XCLK时钟域和TXUSRCLK保持同频。

3.1.4 TX PMA

发送PMA包含并串转换(PISO)和模拟部分的控制(差分电压控制、发送器预加重、校准端接电阻,用于满足SI等)

3.2 Reciever

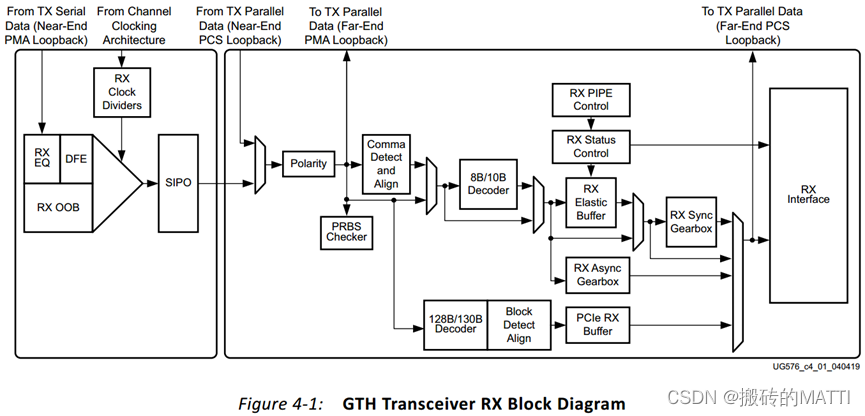

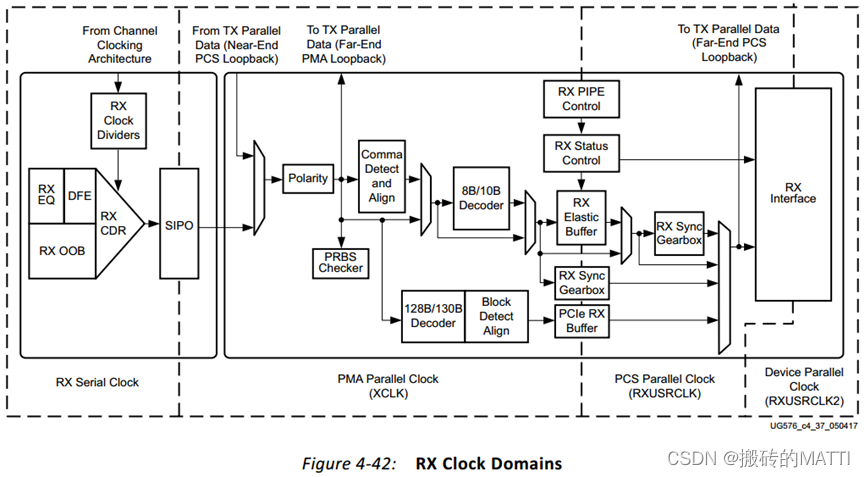

接收链路从PMA-->PCS

3.2.1 RX Equalizer (DFE and LPM)

传输介质和通道是带宽受限的,通过它的信号会衰减和失真。均衡器主要用于补偿由于频率不同而引起的阻抗或者衰减差异。

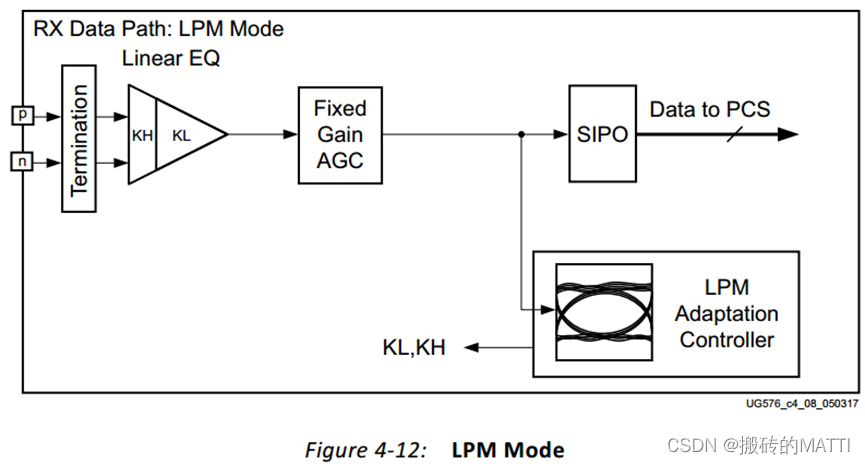

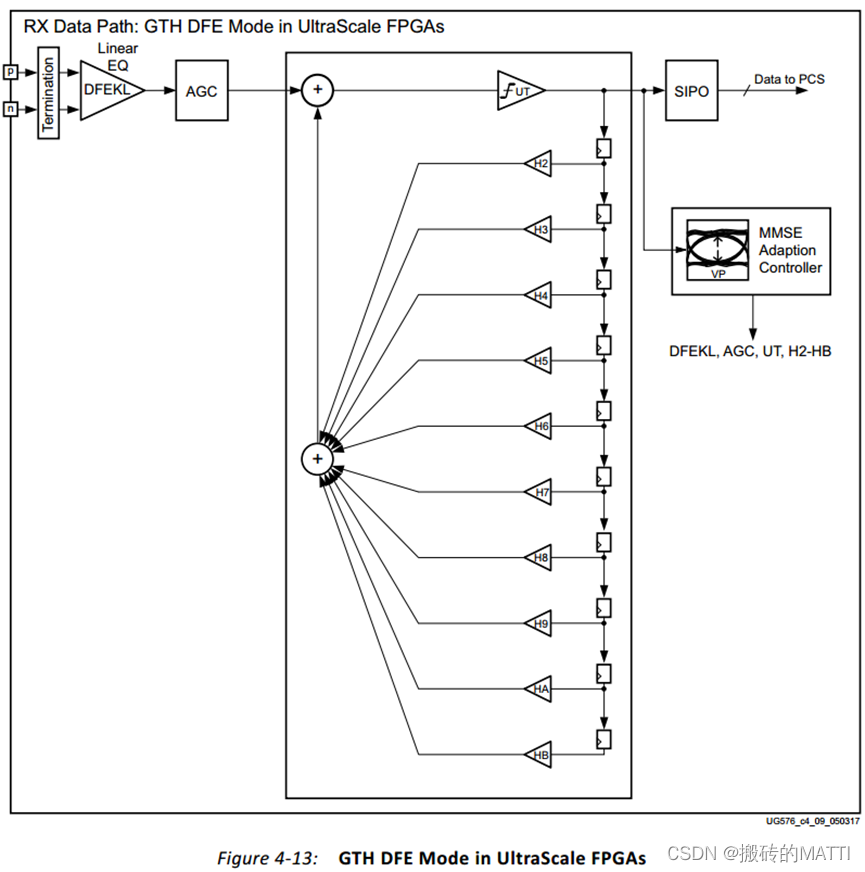

GTH收发器,基于系统级的功耗和性能的权衡,有两种类型的自适应滤波可用:

功耗优化和低通道损耗的低功耗模式(LPM):

均衡更低损耗通道的判决反馈均衡模式(DFE):

3.2.2 RX CDR

CDR:Clock Data Recovery

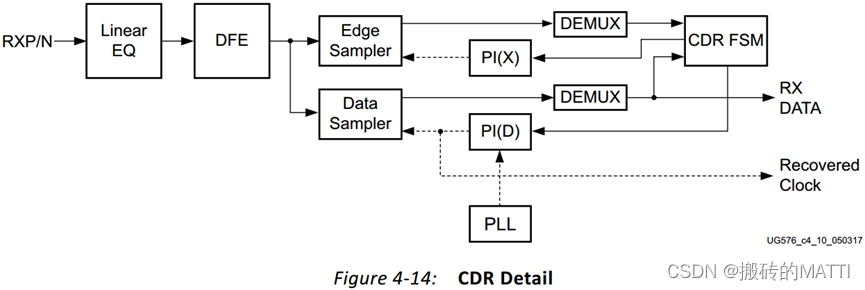

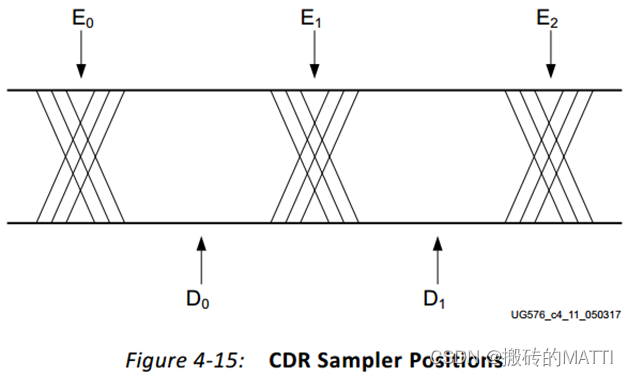

CDR FSM使用来自边缘和数据采样器的数据来确定传入数据流的相位并控制相位插值器(PIs)。边缘采样器的相位锁定在数据流的过渡区域,而数据采样器的相位则位于数据眼的中间。

CPLL或QPLL为相位内插器提供基准时钟。相位内插器依次产生精细的、均匀分布的采样相位,以允许CDR状态机具有精细的相位控制。CDR状态机可以跟踪传入的数据流,这些数据流可以与本地PLL参考时钟存在频率偏移。

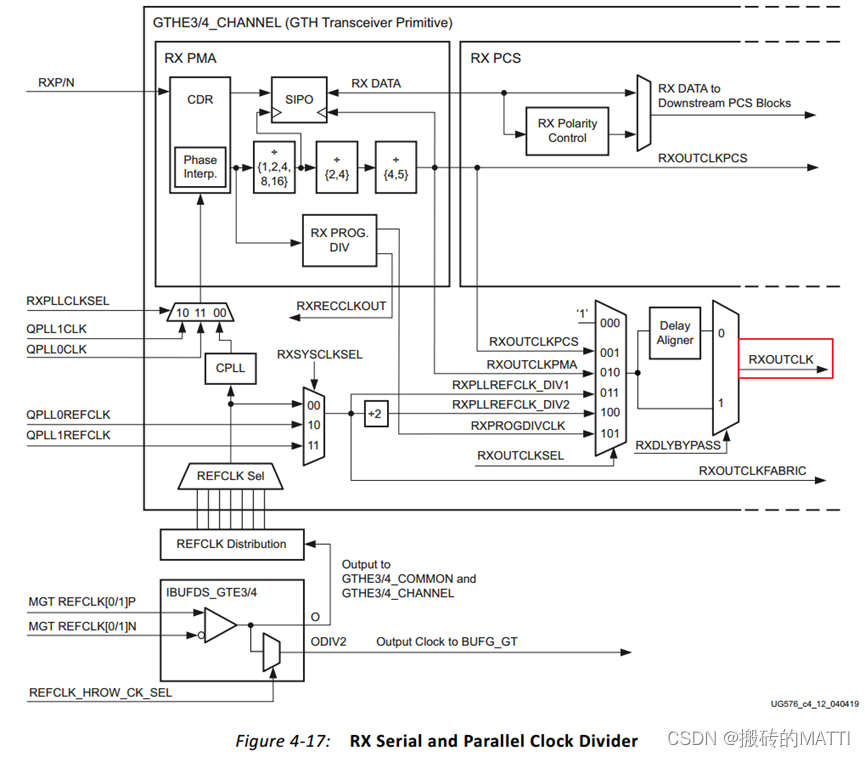

3.2.3 RX Fabric Clock Output Control

与发送一样,使用RXOUTCLK作为RXUSECLK的基准时钟

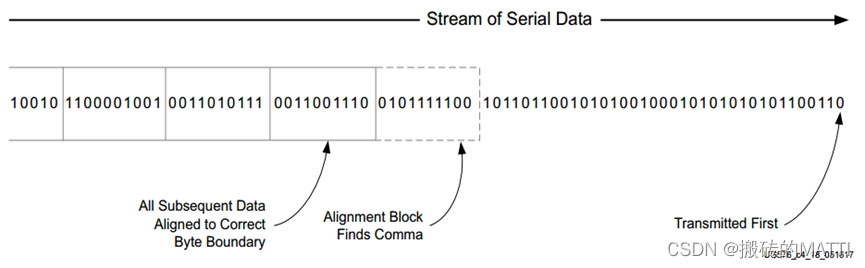

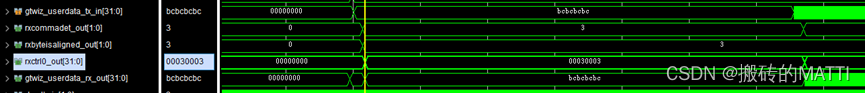

3.2.4 RX Byte and Word Alignment

输入到FPGA收发器的串行数据在解串(串并转换)之前必须进行符号边界对齐。为了保证数据对齐,发送器发送一个通常称为comma码(K码)的字符,接收器在输入的数据里查找comma码。当发下comma码后,则将comma移动到字符边界,这样使得接收到的并行数据匹配发送的并行数据。

3.2.5 RX Elastic Buffer

RX Elastic Buffer:GTH收发器内部包括两个内部并行时钟域:PMA并行时钟域XCLK和RXUSRCLK时钟域。为了正确接收数据,PMA并行速率必须匹配RXUSRCLK时钟速率,并且解决跨时钟域问题。

RX接收端弹性缓冲器是一个重要的功能,和TX接收端缓冲相比,RX多出了一个“弹性”属性,意味着和TX发送端相比,RX弹性缓冲器有更多的功能(RX时钟纠正和RX通道绑定)

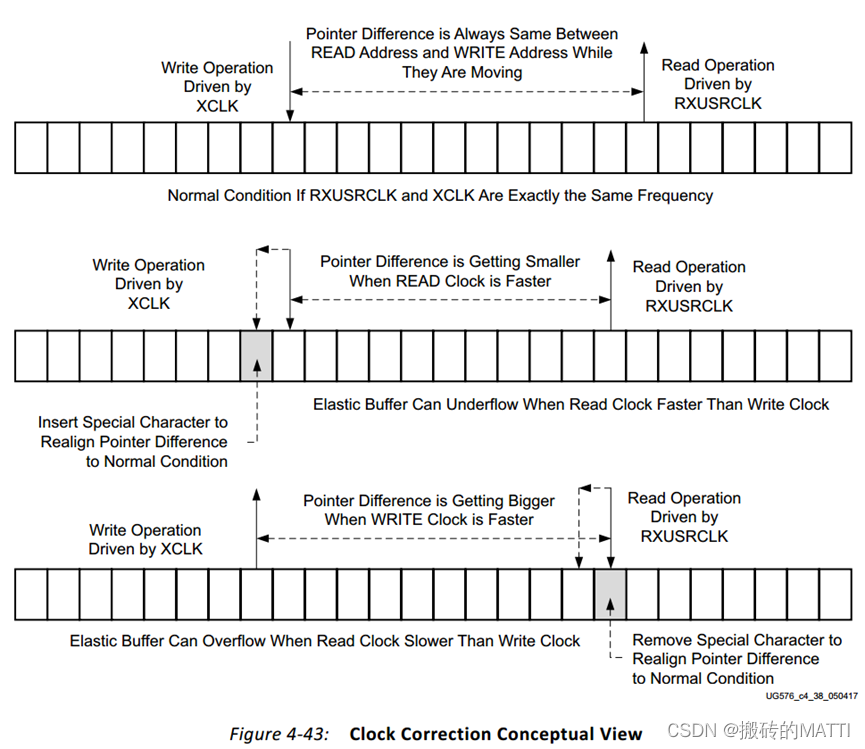

RX Clock Correction:RX弹性缓冲器的“弹性”反映在可以通过时钟纠正来调整XCLK和RXUSRCLK的频率差。对于RX接收端来说,即便XCLK和RXUSRCLK运行在同一个时钟频率,但往往存在一定的差异,这种差异很容易导致RX弹性缓冲器写满或者读空,时钟纠正功能应运而生。时钟纠正功能如图所示。

通俗的讲,在TX发送端的时候,我们会定期的发送K码用于保证接收端边界对齐,在RX弹性缓冲器里面数据不足的时候,接收到的K码数据将被复制写入RX弹性缓冲器,以保持RX弹性缓冲器处于半满。当RX弹性缓冲器数据过多的时候,接收到的K码数据将被舍弃不写入RX弹性缓冲器,以保持RX弹性缓冲器处于半满。

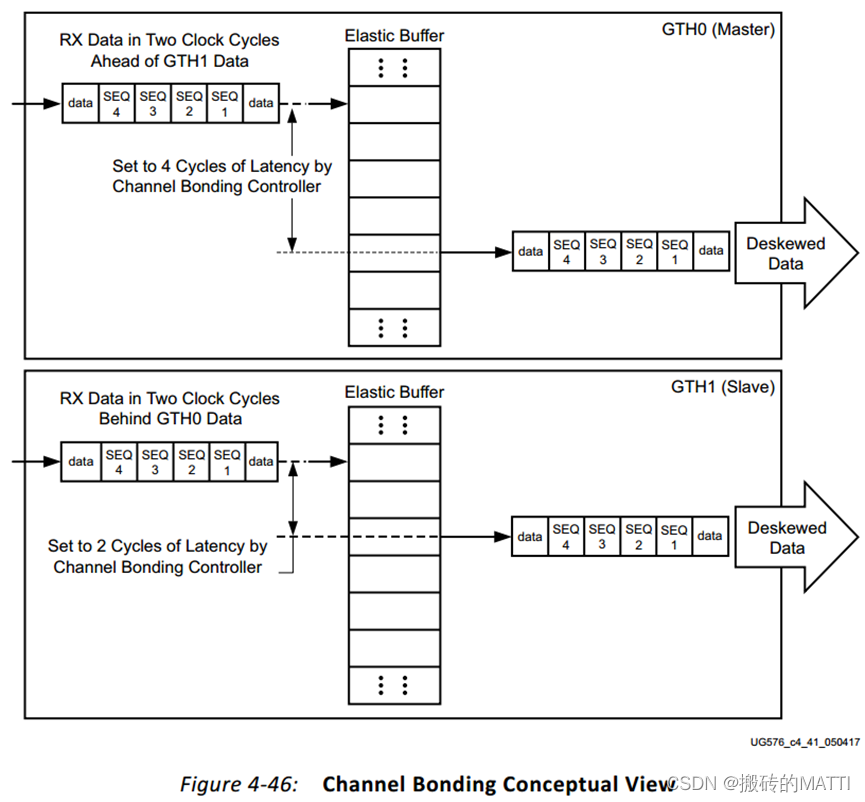

RX Channel Bonding:通道绑定功能同样体现RX弹性缓冲器的“弹性”之处,对于像PCIE和SRIO等协议,可以支持多lane传输来提高传输总带宽。因为传输信道的原因,TX发送端同一时刻发送的数据在RX接收端不能被所有的lane同一时刻接收,每一个lane接收存在时间差,那么在恢复数据的时候就要重新对齐,因此需要在RX接收端执行通道绑定功能。

为了实现这个功能,TX发送端在发送的数据流中加入一个同样的通道绑定序列,子RX接收端根据每一个lane检测到的通道绑定序列在各自的RX弹性缓冲器做相应的调整和延迟,最终使得各个lane的数据不存在偏移,在FPGA RX Interface的输出能和TX发送端发送的数据一样,功能如图所示,左边是未对齐数据,右边是对齐的数据。

RX channel bonding支持8B/10B编码,但是不支持64B/66B、64B/67B、128B/130B和扰码数据。

3.2.6 others

Rx 8B/10B Decoder、RX Interface等与TX端类似

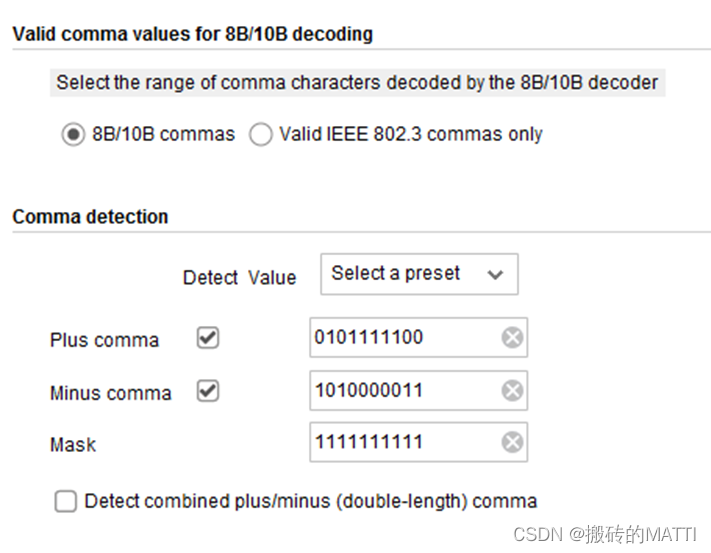

Rx 8B/10B Decoder预设K码

结束语

本文主要是对官方手册的学习笔记,对应GT的详细细节没有过多的深挖。GT作为FPGA内的一种资源,对于我们使用者来说更多的是对其有一个大致了解,其具体细节不用太过深挖,一个是GT资源随着升级其细节也有很多变化,但大体结构是换汤不换药;二是随着FPGA厂商IP的完善,针对不同的应用都有各种底层使用GT资源的更上层的IP core,比如Aurora、PCIe、以太网、interlaken等等,如果只是站在使用者的角度来说的话,可能很少会接触到GT底层。当然,通过对GT资源的理解也更加方便我们上层应用的开发和调试。如果涉及到太底层的问题可以在需要的时候再翻手册查询。

标签:发送,GT,FPGA,TX,RX,学习,Xilinx,时钟 From: https://www.cnblogs.com/amxiang/p/17028748.html