随着通信与网络技术、互联网的发展,工业管理数据化、网络化、智能化已成大势所趋,利用工业物联网完成工业控制是智慧工厂中必不可少的一部分。传统的控制与数据采集系统,主机一旦需要同时与多个数据采集设备保持高速通信,并要承担更复杂的数据处理、保持高清的多媒体显示等功能,传统的工业数据采集硬件系统就相形见绌了。而基于ARM和FPGA架构的嵌入式系统自带丰富外设接口,具备高清显示、高速传输等功能,还可以并行完成对于工业数据高速采集任务。是工业4.0硬件升级必备选择之一。

图片来自网络

图片来自网络

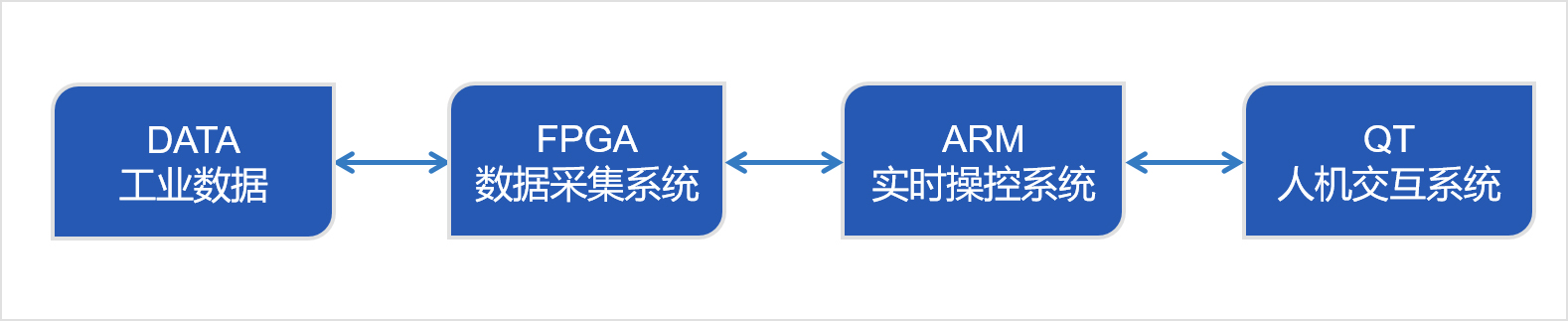

工业数据采集控制系统主要分两大结构。首先是数据采集系统,以FPGA处理器为主,主要用于工业协议数据的高速采集和获取;其次是嵌入式控制平台,以ARM处理器为主,作为主控中心进行各模块的协调管理和资源调度,同时接收FPGA端数据、结果可视化以及人机交互。利用通信模块将获取的数据传输到工业MES+ERP系统上,既降低人工数据录入的风险,又减少人力资源的浪费。

工业数据采集控制系统-框架图

工业数据采集控制系统-框架图

工业数据采集控制系统,主要可以分为高速数据采集系统和嵌入式人机交互系统,两大系统是构成工业自动化数据采集系统重要组成部分,是工业4.0升级必不可少的工业系统之一。

工业数据采集控制系统-流程图

工业数据采集控制系统-流程图

-

高速数据采集系统:FPGA芯片+工业信号采集系统,共同组成的高速数据采集系统是快速获取工业信息数据的重要途径。通过外部各种数据采集模块,例如摄像头,位移传感器,高精度ADC采样模块等,FPGA芯片把各模块的数据信号进行并行采样处理,存储。从而实现高速工业数据采集功能。

-

嵌入式人机交互系统:人机交互系统作为整个系统的核心,一方面通过SPI/PCIE发送采集指令信号给到信号控制系统FPGA进行数据采集,数据采集处理后通过SPI/PCIE上传到ARM芯片进行数据处理和分析。另一方面可以通过USB连接鼠标键盘,人工输入指令,进行脚本自动抓取数据,并通过触摸显示系统进行数据结果展示;还可以通过网络上传工业MES+ERP系统,对工业数据进行云存储。

基于MYC-JX8MMA7的工业数据采集控制系统图

基于MYC-JX8MMA7的工业数据采集控制系统图

基于米尔刚发布新品MYC-JX8MMA7核心板的工业数据采集控制系统解决方案,可以一板满足硬件系统的两大处理器需求。FPGA+ARM的异核架构核心板,可以极大降低客户硬件成本和硬件设计难度,并提供丰富的开发资源,可以加速产品开发进程。

-

满足高速数据采集需求

MYC-JX8MMA7核心板搭载的Xilinx Artix-7对标Zynq 7010的FPGA资源,满足【数据采集系统】的高速数据采集的需求。

-

优异的人机交互和实时操控功能

MYC-JX8MMA7核心板搭载的NXP i.MX8M Mini芯片具备4颗Cortex-A53内核和Cortex-M4内核能够提供出色的数据处理能力和人机交互界面,并且可以实时操控电机驱动模块,满足【实时操控系统】的数据处理、任务调度和人机交互要求。

-

高速通信能力

MYC-JX8MMA7核心板MPU与FPGA之间采用PCIE高速通信,高达200~300MB/S的通信能力,满足数据的快速传输需求。

为了方便开发者进行前期功能评估和软件调试,米尔同时开发了MYD-JX8MMA7开发板,助力产品开发。

ARM+FPGA架构、ARM+FPGA架构处理器、ARM+FPGA架构核心板、ARM+FPGA开发板、异核架构、异核核心板、异核开发板、MPU+FPGA、i.MX8M Mini+ARTIX-7、artix-7、artix-7核心板、artix-7开发板、i.MX8M Mini核心板、i.MX8M Mini开发板

标签:FPGA,JX8MMA7,系统,采集,工业,MYC,数据,ARM From: https://www.cnblogs.com/cbd7788/p/16944739.html