@

目录1 输入路径约束

由于STA不能检查不受约束路径上的时序约束,因此需要约束所有路径来进行时序分析

当然,如果存在一些输入控制信号,我们并不关心其信号时序,可能并不需要进行时序检查

如下图是一个待分析设计(DUA),UFF0是外部设计,其输出是UFF0的输入,并且UFF0在设计内部,二者的数据通过输入port INP1连接

UFF0和UFF1都是由时钟CLKA驱动的,了解过建立时间和保持时间的应该知道,在第一个时钟上升沿UFF0发送数据,UFF1在下一个时钟上升沿接收数据,因此CLKA的周期应该是数据从UFF0到UFF1的时间

接下来根据上面的图分析时间

对于外部设计,从UFF0到端口INP1时间的是UFF0需要的时间Tclk2q(CK端 -> Q端的时间)+ C1所需的时间Tc1

那么输入端口INP1上的延迟定义指定的是外部延迟的总和(Tclk2q + Tc1)

假设Tclk2q是0.9ns,Tc1是0.6ns,那么输入延迟约束为:

set Tclk2q 0.9

set Tc1 0.6

set_input_delay -clock CLKA -max [expr Tclk2q + Tc1] [get_ports INP1]

根据这个约束可以知道,输入端口INP1的外部延迟是1.5ns (Tclk2q + Tc1),如果时钟CLKA的周期是2ns,那么端口INP1只剩下500ps(2ns - 1.5ns)的时间可以在设计内部传播

也就是说,UFF1要想在下一个时钟上升沿捕获UFF0发送的稳定的数据,Tc2 + UFF1 setup时间必须小于500ps

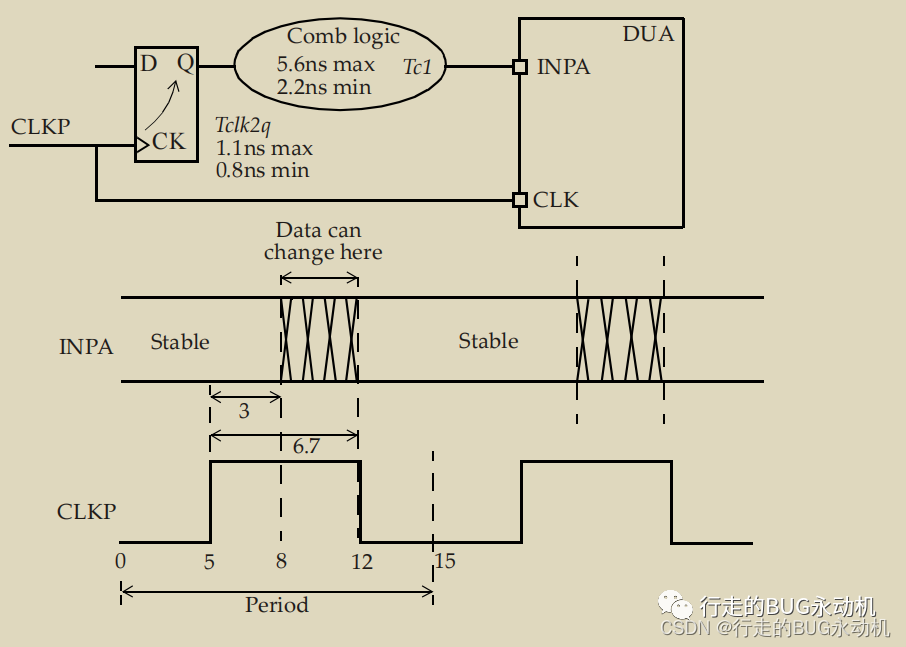

了解过setup time和hold time计算的应该留意过,电路中延迟都会给出最大时间和最小时间,用下图的例子加上最大时间和最小时间和分析

最大延迟对应的是最长路径的时间,最小时间对应的是最短路径的时间,通常我们把最大路径称为worst path,最短路径称为best path,在分析setup时,通常是分析worst path

对于这个例子,输入约束为:

created_clock -period 15 -waveform {5 12} [get_ports CLKP]

set_input_delay -clock CLKP -max 6.7 [get_ports INPA]

set_input_delay -clock CLKP -min 3.0 [get_ports INPA]

-max指定的是最大延迟-min指定的是最小延迟

如果没有指定,则认为最大延迟和最小延迟一致,比如下面这个约束

set_input_delay -clock clk_core 0.5 [get_ports bist_mode]

set_input_delay -clock clk_core 0.5 [get_pots sad_state]

由于没有 -max 和 -min,因此最大延迟和最小延迟均为0.5ns

2 输出路径约束

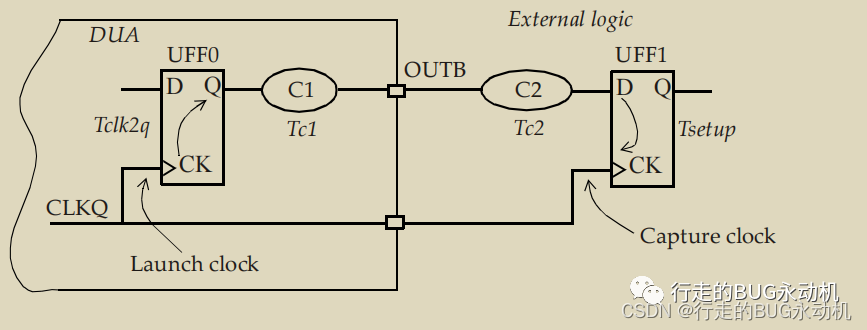

与输入路径约束中第一个例子相似,同样是UFF0发送数据,UFF1捕获数据,只不过此时UFF0是内部设计,UFF1是外部设计,如下图所示

此时端口OUTB到UFF1的传播时间(Tc2 + UFF1的setup time)是输出路径的约束

假设Tc2的时间是3.9ns,UFF1的setup time是1.1ns,那么输出约束可定义为:

set Tc2 3.9

set Tsetup 1.1

set_output_delay -clock CLKQ -max [expr Tc2 + Tsetup] [get_ports OUTB]

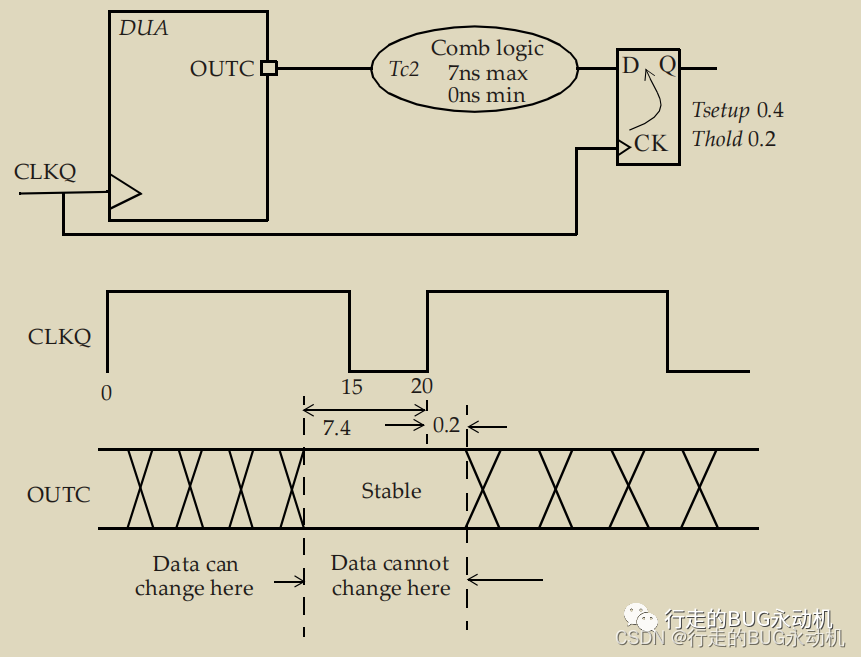

再来看下个例子

最大延迟路径为7.4ns(Tc2的最大值 + Tsetup),最小延迟路径为 -0.2ns(Tc2的最小值 - Thold),因此约束为:

creat_clock -period 20 -waveform {0 15} [get_ports CLKQ]

set_output_delay -clock CLKQ -max 7.4 [get_ports OUTC]

set_output_delay -clock CLKQ -min -0.2 [get_ports OUTC]

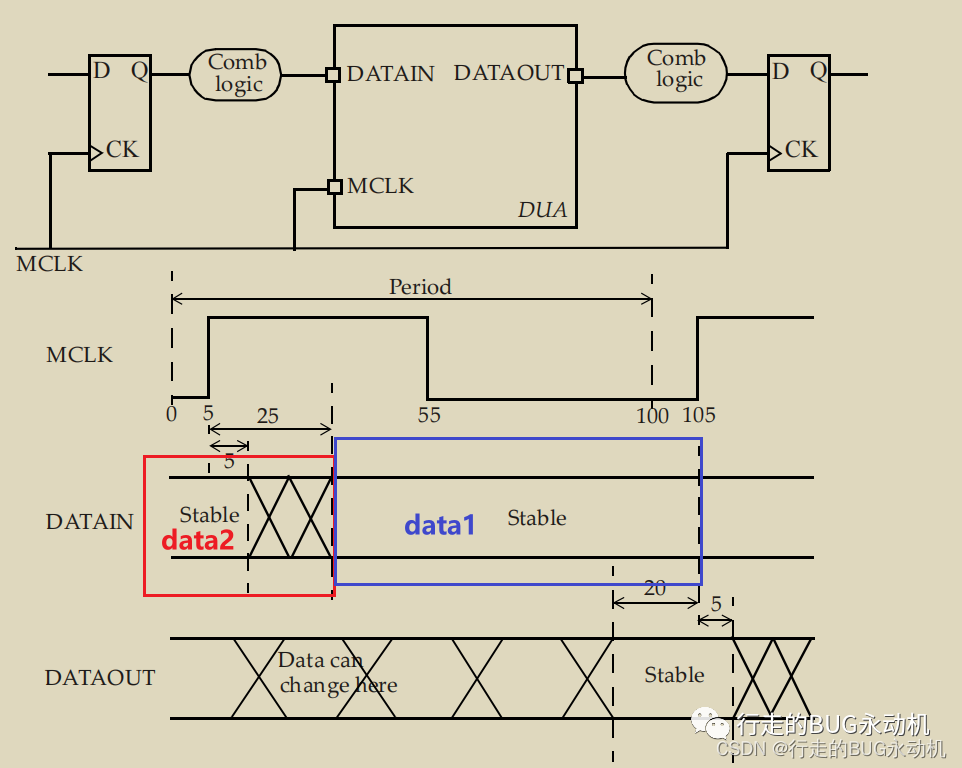

下看一个同时具有输入约束和输出约束的例子

在这个例子中,DUA具有两个输入端口DATAIN和MCLK,以及一个输出端口DATAOUT

从图中可以看到,时钟周期是100ns

对于DATAIN的波形,红的方框框住的是当前的数据,而蓝色方框框住的是前一次的数据,因此,data2保持稳定的时间最大是25ns,最小是5ns

对于DATAOUT的波形,数据保持稳定的时间最小是 -5ns,最大是20ns,那么约束可定义如下:

creat_clock -period 100 waveform {5 55} [get_ports MCLK]

set_input_delay 25 -clock MCLK -max [get_ports MCLK]

set_input_delay 5 -clock MCLK -min [get_ports MCLK]

set_output_delay 20 -clock MCLK -max [get_ports MCLK]

set_input_delay -5 -clock MCLK -max [get_ports MCLK]

参考

Static Timing Analysis for Nanometer Designs: A Practical Approach

标签:set,STA,clock,输入输出,路径,delay,UFF0,get,ports From: https://www.cnblogs.com/ICcode/p/16901190.html