https://zhuanlan.zhihu.com/p/150534875

https://blog.csdn.net/qq_39507748/article/details/114746186

https://blog.csdn.net/zyn1347806/article/details/108649518

Input delay & Output Delay in STA

Flavin

芯路励成

Flavin

芯路励成

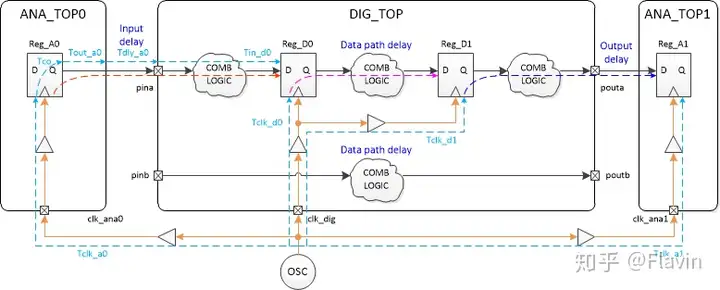

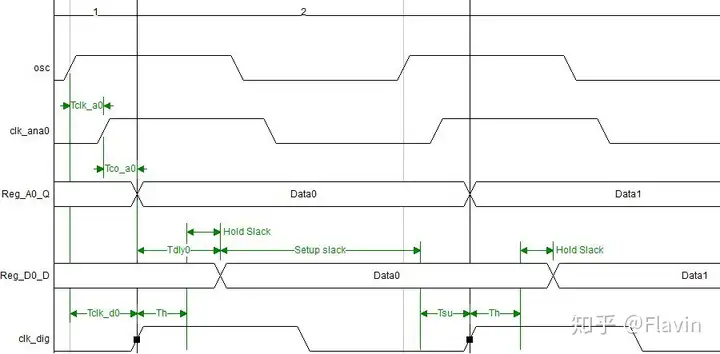

Note: Tdly0=Touta0+Tdly_a0+Tin_d0

1. input delay

'set_input_delay' constrains the time range that input signal arrives its module' port after its launch clock edge.

(1) input delay max:

Setup Slack=Tclk+Tclk_d0(min)−(Tclk_a0(max)+Tco_a0(max)+Tdly0(max)+Tsu)≥0

Therefore:

Tco_a0(max)+Tdly0(max)+(Tclk_a0(max)−Tclk_d0(min))≤Tclk−Tsu

Input delay max=Tco_a0(max)+Tdly0(max)−(Tclk_d0(min)−(Tclk_a0(max))=Tco_a0(max)+Tdly0(max)−Tskew(min)

(2) input delay min:

Hold Slack=(Tclk_a0(min)+Tco_a0(min)+Tdly0(min))−(Th+Tclk_d0(max))≥0

Therefore

Tclk_a0(min)+Tco_a0(min)+Tdly0(min)−Tclk_d0(max)≥Th

Input delay min=Tco_a0(min)+Tdly0(min)−(Tclk_d0(max)−Tclk_a0(min))=Tco_a0(min)+Tdly0(min)−Tskew(max)

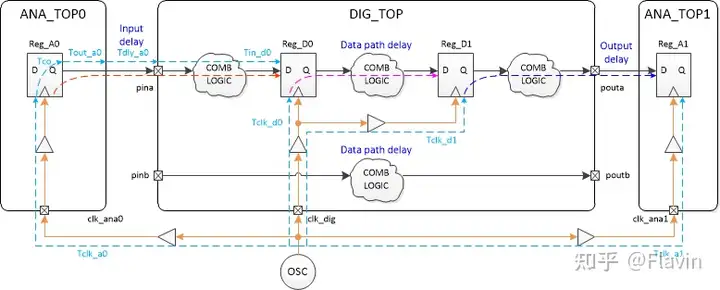

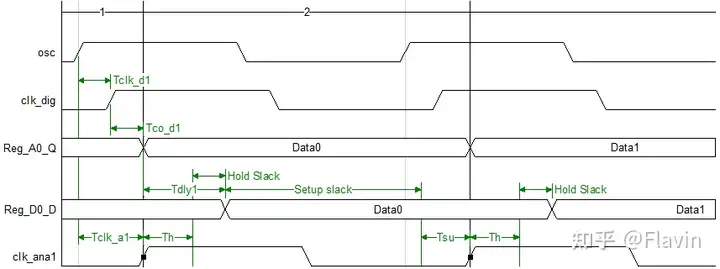

2. output delay

'set_output_delay' constrains the time range that output signal should be ready before its capture clock edge.

(1) output delay max:

Setup Slack=Tclk+Tclk_a1(min)−(Tclk_d1(max)+Tco_d1(max)+Tdly1(max)+Tsu)≥0

Therefore:

Tco_d1(max)+Tdly1(max)+(Tclk_d1(max)−Tclk_a1(min))≤Tclk−Tsu

Output delay max=Tco_d1(max)+Tdly1(max)−(Tclk_a1(min)−(Tclk_d1(max))=Tco_d1(max)+Tdly1(max)−Tskew(min)

(2) output delay min:

Hold Slack=(Tclk_d1(min)+Tco_d1(min)+Tdly1(min))−(Th+Tclk_a1(max))≥0

Therefore

Tclk_d1(min)+Tco_d1(min)+Tdly1(min)−Tclk_a1(max)≥Th

output delay min=Tco_d1(min)+Tdly1(min)−(Tclk_a1(max)−Tclk_d1(min))=Tco_d1(min)+Tdly1(min)−Tskew(max)

3. Reference

- https://blog.csdn.net/qq_39507748/article/details/114746186

- https://blog.csdn.net/zyn1347806/article/details/108649518

一、设置输入延时(Input Delay)

1、不同的路径需要使用不同的约束

2、输入延时的定义

由下图可以看出Input Delay是以上游芯片的时钟发送沿为参考,上游的输出数据到达FPGA的外部输入端口之间的延迟。

输入延迟(input delay)包括Tco和Trace Delay(板间延迟),其中Trace delay又叫Board delay。

3、完整的输入静态时序路径

4、输入静态时序路径分析报告

可以看出它主要把时序路径分为三部分,然后分别计算各部分的延时,最后计算出裕量slack,根据slack的值来判断时序是否正确。

关于时序报告中这几部分的延时为啥要这么算,可以参考这篇文章 传送门 最后的附录部分加以理解。

5、设置输入延时

需要注意的是,如果同时设置了max和min delay,那么max值是用在对Input Setup Timing的分析中的,而min值用在对Input hold Timing的分析中。如果只设置了一个值,那么同时供两者使用!!!

6、DDR输入延时举例

之所以要这么设置,是因为DDR在时钟下降沿采集前一个上升沿发送的数据,在下一个上升沿采集前一个下降沿发送的数据。因为默认设置都是针对上升沿的,因此我们还需要针对下降沿再设置一下参数。

7、静态时序路径

静态时序路径从时钟元件开始,在时钟元件结束

从内部触发器到内部触发器的路径受到时钟的约束

FPGA的输入和输出不是静态时序路径的起点/终点

默认情况下,主I/O和内部时钟元件之间的任何逻辑都不是完整静态时序路径的一部分

如果没有其他命令,就不会对与I/O相关的逻辑进行设置/保持检查

为了获取完整的静态时序路径,我们需要向Vivado静态时序引擎描述外部元素

输入端口:

外部设备使用的时钟

外部设备时钟与到达FPGA输入端口之间的延迟;包括外部设备的CLK->Q的时间和板延迟

输出端口:

FPGA的输出端口与外部设备时钟之间的延迟;包括外部设备需求时间和板延迟

二、设置输出延时(Output Delay)

1、不同的路径需要使用不同的约束

2、输出延时

输出延时指的是从FPGA输出数据后到达外部器件时钟沿的延时时间,其中PCB板上的走线延时以及外部器件的数据建立和保持时间。也可以理解为在捕获沿到来时,数据已经存在的时间,如上图所示!!!

3、外部建立和输出时间要求

因为是以下游芯片的捕获沿为参考点,所以建立时间为正,保持时间为负。

4、完整的输出静态时序路径

输出静态时序路径的分段略有不同:

数据路径延迟在FPGA的输出端口结束

目的时钟路径通过下游设备返回到FPGA的输出端口

5、输出静态时序分析报告

关于时序报告中这几部分的延时为啥要这么算,可以参考这篇文章 传送门 最后的附录部分加以理解。

6、DDR输出延时举例

7、输出延时摘要

这说明在所需的稳定区域开始之前,数据必须在输出端口准备就绪,并且必须保持稳定,直到稳定区域结束;

这映射成了逻辑到FPGA内部输出端口的时序要求;

三、设置最大延时(max_delay)

1、异步输入到输出的延时

2、设置最大延时举例

3、最大延时时序报告

最后总结一下,在阅读时序报告时可以发现,时序路径中的三部分在计算延时的时候,基本公式都是:

T(source clock path) + T(data path) = 实际的数据到达时间;

T(destination clock path) - Ts(或者+Th) = 数据需求时间;

但是:

如果设置了input delay,那input delay应该加到data path delay中;

如果设置了output delay,那应该用output delay替换数据需求时间中的Ts或者Th;

并且,如果input delay和output delay设置了max和min,那么:

如果是对建立时间进行时序分析,则使用max;并且在T(destination clock path) - Ts中,destination clock path的初始时间是一个clock周期;

如果对保持时间进行时序分析,则使用min;并且在T(destination clock path) +Th中,destination clock path的初始时间为0。

————————————————

版权声明:本文为CSDN博主「耐心的小黑」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/qq_39507748/article/details/114746186

set_input_delay/set_output_delay

进击的芯片

于 2020-09-17 20:05:10 发布

17156

收藏 217

分类专栏: flow 综合 文章标签: sdc 芯片

版权

flow

同时被 2 个专栏收录

6 篇文章6 订阅

订阅专栏

综合

7 篇文章5 订阅

订阅专栏

input delay和output delay是在SDC中经常会遇到的问题,看似简单其实还有很多模棱两可的问题的。特别是为什要设置input delay和output delay?常用的30%和70%的原因以及input delay和output delay有些情况下回设置负值。针对这些问题,我通过研究,把自己的一些总结进行记录,如有问题欢迎留言交流。

目录

为什么需要设置input delay和output delay

如何设置设置input delay和output delay

命令介绍

常用70%设置

output delay值为负值

input delay值为负值

对于一个芯片设计来说,芯片的外部都会有一些器件和芯片进行数据的交换,简单的示意图如下所示。DUA是我们的设计芯片,外部的器件从STA的角度被简化为两个寄存器和一些组合逻辑。

如上图所示,如果在design设计上没有对DATAIN DATAOUT的数据进行约束,那么STA工具并不能够得到有外部寄存器经过组合逻辑到达DATAIN的时间,同时也不知道DATAIN信号和输入的MCLK是什么关系(如果有多个时钟,到底和哪个时钟是有关的??)和内部采样reg的关系。input delay和output delay就是告诉STA工具芯片外部的信号的delay信息。如果知道芯片外部器件的data sheet,那么input delay和output delay要严格按照data sheet的要求去设置,如果没有就需要和designer确认具体的时序图,根据design的要求合理设置。

为什么需要设置input delay和output delay

如果不设置input delay和output delay,那么工具并不知道上述信息,也就是说工具并不会分析这条path。由于大多数信号进入芯片内部都是需要和芯片内部进行数据传递的,所以必须通过设计input delay和output delay的方式告诉工具此处的timing信息,这样才能保证输入的信号能够被芯片内部正确的采样,从而保证芯片工作正常。

反之,如果某些信号是一些在芯片正常工作之前就稳定的常值信号(bist en 等),那么实际上是没有必要对这些信号进行timing 分析的,所以这些信号可以不用设计input delay来简化约束。

如何设置设置input delay和output delay

对于input delay和output delay关键是理解下面两句话的含义

set_input_delay是说该输入信号是在时钟沿后多长时间到达模块的port上的 。

set_output_delay是说该输出信号在后级模块中需要在时钟沿之前提前多长时间准备好。

命令介绍

这里以input delay为例,output delay设置大同小异。set_input_delay命令语法如下

SYNTAX

status set_input_delay

delay_value

[-reference_pin pin_port_name]

[-clock clock_name]

[-clock_fall]

[-level_sensitive]

[-network_latency_included]

[-source_latency_included]

[-rise]

[-fall]

[-max]

[-min]

[-add_delay]

port_pin_list

Data Types

delay_value float

clock_name collection of 1 object

port_pin_list collection

这里讲解几个主要的参数

port_pin_list 指定设置input delay的port是哪些

-clock 指定设置input delay的port是相对于哪个时钟设置的,即由port进入的signal信号是有哪个clock采样的,例如 组APB总线的信号,进入芯片内部采样时钟应该是APB clk。

-max/min 指定input delay的最大值和最小值,分别用于STA的setup check和hold check计算。

-clock_fall 如果外部时钟是下降沿发送数据,需要指定该参数,让工具进行下降沿check。默认都是进行上升沿check的。

常用70%设置

input delay最常用的设置是对一组信号设置为采样时钟的70%.例如APB总线的输入时钟是apb_clk,对于apb的pwdata pradata port的input delay和output delay约束为

set_input_delay -max [expr 0.7 * apb_clk] -clock apb_clk [get_ports apb_pwdata]

set_output_delay -max [expr 0.7 * apb_clk] -clock apb_clk [get_ports apb_prdata]

为什么要设置70%?因为input delay是约束芯片外部的delay 情况,也就是外部约束70%,内部剩余30%的余量,因为外部的情况并不太清楚,所以估计的悲观一些,output delay原因同理。如果估计的过于乐观,那么如果都是这么设置的有可能导致两个block接上之后timing设置都不能满足timing check要求

有时,我们还会看到一些对于input delay的特别设置,如

set_input_delay -min 2 -clock apb_clk [get_ports apb_pwdata]

这样设置一般出现在block的顶层模块和TOP交互的信号,由于这是从外部传进来的信号如果不设置input delay的min,那么往往接口处会出现大量的hold violation,但是由于顶层到block的path delay并不准确,所以这些hold往往在block时并不去处理,但是在auto fix hold时,如果不指定group,那么工具会在接口处插一些buffer,有可能这些buffer是不需要的,为了减少对顶层的影响,所以此处设置一个比较大的input delay min,不让工具报出这些violation,从而也就避免了去插buffer fix hold。

output delay值为负值

考虑如下的timing path

假定都是相对于时钟的上升沿采样数据,同时假定所有的net delay为0

对于input delay,可以看到数据在片外的reg上升沿25ns之后,数据才从Q端发出,即到达DATAIN port时外部的delay已经有25ns;同时上一个数据能够在MCLK上升沿之后保持5ns,即数据如果被芯片内部clk采样那么数据也会保持5ns,也就是说对于DUA的第一个寄存器来说天然就有5ns的hold margin。所以对应的input delay应该按照如下设置

set_input_delay 25 -max -clock MCLK [get_ports DATAIN]

set_input_delay 5 -min -clock MCLK [get_ports DATAIN]

对于output delay,可以看到外部的寄存器要求的setup time是20ns,hold time是5ns。由于output delay的含义是说数据在时钟沿前什么时候稳定。所以为了满足要求,output delay应该按照如下设置

set_output_delay 20 -max -clock MCLK [get_ports DATAOUT]

set_output_delay -5 -min -clock MCLK [get_ports DATAOUT]

input delay值为负值

考虑如下的timing path

即片外的CLKA在到达UFF1的clk path明显比data path的delay要长(由于CTS等原因导致)1ns,即在UFF1来看数据提前CLKA到达UFF1/D.假设

Tclk2q=2ns

Tc1=3ns

UFF1 Tsetup=1ns Thold=0.5ns

那么对于DUA的INP1来说应该如何设置input delay

set_input_delay 6 -max -clock CLKA [get_ports INP1]

set_input_delay -1 -min -clock CLKA [get_ports INP1]

————————————————

版权声明:本文为CSDN博主「进击的芯片」的原创文章,遵循CC 4.0 BY-SA版权协议,转载请附上原文出处链接及本声明。

原文链接:https://blog.csdn.net/zyn1347806/article/details/108649518