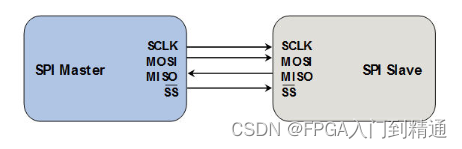

1、SPI总线进行通信的结构

SPI总线主要包括四根关键信号线:

(1)SCK (Serial Clock)

串行时钟线,由主设备产生,控制数据传输的速率和时机。

(2)MOSI (Master Out Slave In)

主设备数据输出线,数据由主设备发送给从设备。

(3)MISO (Master In Slave Out)

从设备数据输出线,数据由从设备发送回主设备。

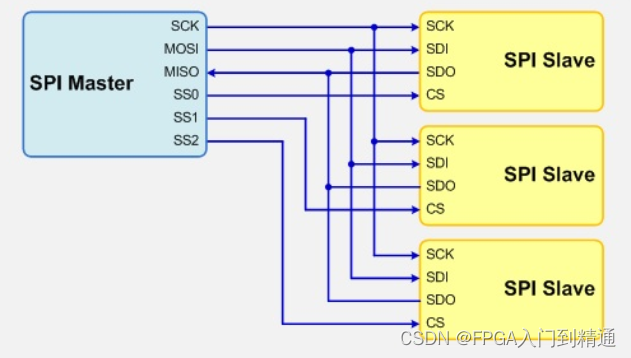

(4)CS/SS (Chip Select/Slave Select)

片选信号线,用于激活特定的从设备。

2、SPI总线传输的模式

由时钟极性(CPOL,Clock Polarity)和时钟相位(CPHA,Clock Phase)来定义。

模式0:CPOL= 0,CPHA=0。SCK空闲时为低电平,数据在SCK时钟的上升沿被采样,数据在SCK时钟的下降沿更新。

模式1:CPOL= 0,CPHA=1。SCK空闲时为低电平,数据在SCK时钟的下降沿被采样,数据在SCK时钟的上升沿切换

模式2:CPOL= 1,CPHA=0。SCK空闲时为高电平,数据在SCK时钟的下降沿被采样,数据在SCK时钟的上升沿更新。

模式3:CPOL= 1,CPHA=1。SCK空闲时为高电平,数据在SCK时钟的上升沿被采样,数据在SCK时钟的下降沿更新。

3、SPI主从模式

SPI采用主从模式工作,有一个主设备(Master)控制一个或多个从设备(Slave),主设备负责生成时钟信号并发起数据传输。

源码下载链接:

https://pan.quark.cn/s/1c7b9834d753

标签:CPOL,FPGA,SCK,SPI,CPHA,时钟,spi,源代码,设备 From: https://blog.csdn.net/mengzaishenqiu/article/details/141704521