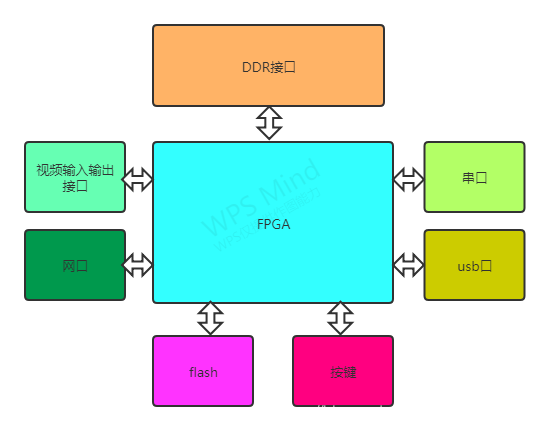

一、项目架构设计

FPGA设计是采用自顶向下,模块化设计的方式,这样便于仿真调试。

注:特别是在整体架构的基础上,能把整体的数据流向和控制逻辑梳理清楚,这样实现起来就很容易。

注意:Verilog是硬件设计语言,跟软件设计有本质区别

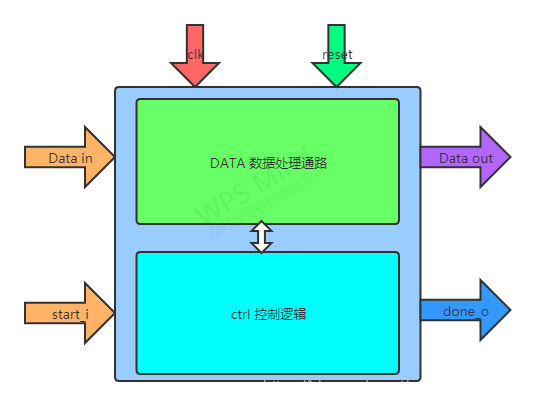

二、模块架构设计

基本原则:控制逻辑和数据逻辑分开处理

三、模块接口设计

1、模块定义

主要包括5个部分:端口定义、参数定义(可选)、输入输出接口、内部信号说明、功能定义。

module module\_name#(

parameter WIDTH = 10;

)(

input wire clk,

input wire reset,

input wire start\_i,

input wire valid\_i,

input wire \[WIDTH - 1:0\] data\_i,

output reg done\_o,

output reg \[WIDTH - 1:0\] data\_o

);

........

enmodule

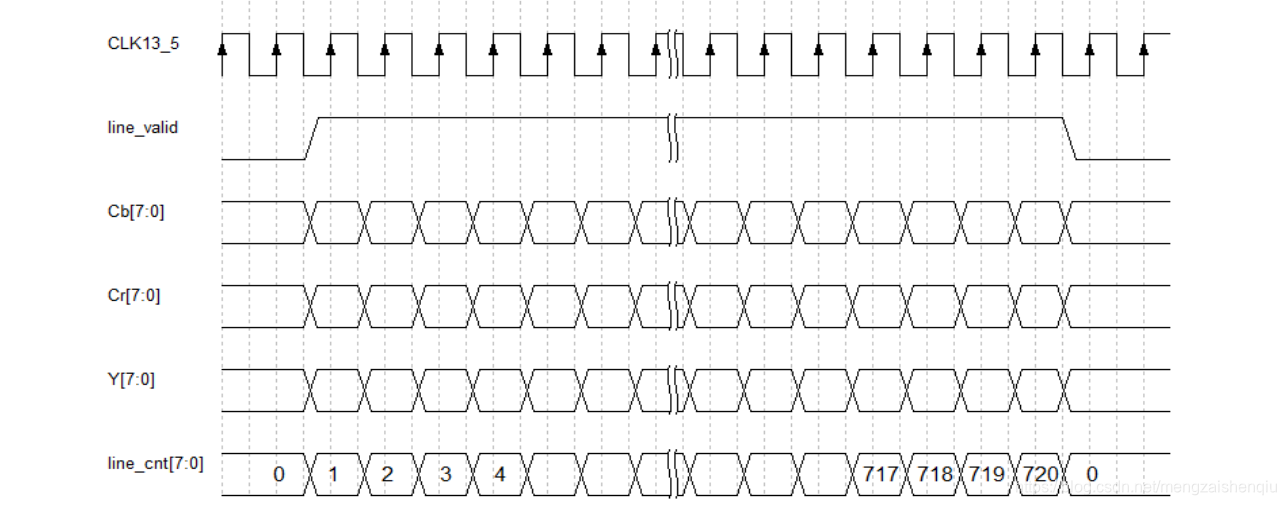

2、接口时序设计

模块与模块之间的通过接口通信的,所以接口时序规范非常重要。

3、模块输入输出接口规范

(1)考虑时序的要求,注意不允许组合电路输出,需要使用寄存器输出。

(2)接口命名规范

命名必须见名知义,采用英文单词命名,可以使用“[a-z、A-Z、_、0-9] 大小写字母、数字、下划线”表示,注意不能以数字开头。

信号类型 | 命名规范 |

模块端口输入 | [pin_name]_i |

模块端口输出 | [pin_name]_o |

模块内部寄存器 | [reg_name]_r |

模块内部连线 | [wire_name]_w |

时钟信号 | clk |

复位信号 | reset |

4、代码设计规范

(1)不使用初始化语句;

(2)不使用延时语句;

(3)不使用循环次数不确定的语句,如:forever,while等;

(4)尽量采用同步方式设计电路;

(5)尽量采用行为语句完成设计;

(6)always过程块描述组合逻辑,应在敏感信号表中列出所有的输入信号;

(7)所有的内部寄存器都应该可以被复位;

(8)用户自定义原件(UDP元件)是不能被综合的。

5、命名规范

(1)顶层文件名命名:对象+功能+top,如video_oneline_top

(2)逻辑控制文件命名:对象+ctr,如:ddr_ctr.v

(3)参数文件命名:对象+para,如lcd_para.v

(4)程序注释说明:如“//”或者“/*...*/”

(5)时钟信号命名:对象+功能+特性,如phy_txclk

(6)计数器命名:对象+cnt+r,如line_cnt_r

(7)复位信号命名:高电平有效:reset,低电平有效:reset_n

标签:wire,name,代码,规范,接口,verilog,模块,命名,input From: https://www.cnblogs.com/L707/p/18075292