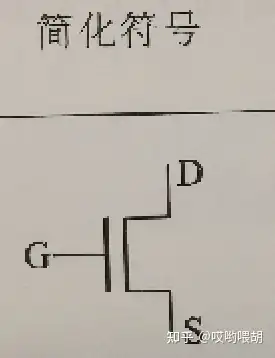

MOS管:mos管是个开关,栅极(G)是控制端,它控制着源极(S)和漏极(D)之间是否能导通,即是否可以通过电流。

转自知乎https://zhuanlan.zhihu.com/p/368263926

我看书中(第二版)84页的图认为读放大器没必要有,然后搜了一下,可能因为延迟和功耗吧,没学到后面。

当某一行被选中后(相当于选中了希望读出的数据),该行存储单元则会根据存储的数据将位线对的某一条位线下拉,该信号将被后续读出电路读出。如果把该行的存储单元当成数字电路中的一个门(gate),则可以算出该门的扇出在100的数量级,远远偏离电路延迟(latency)的最优解数十倍。由于该门显然处于关键路径(criticalpath)上,可以想象,如果依靠存储单元得到轨对轨输出,不光对存储器的读出延迟的影响是灾难性的,而且功耗也极大(E(peroperation)=VQ=CBLVDD2 )。有两个思路可以改善这个问题:1. 仍然使用大信号读出(large-signal sensing),通过减小扇出,即减少单对位线上的存储单元数量如使用多级(hierarchical BL)结构;2.使用小信号读出(small-signal sensing),即使用读出放大器将位线的信号放大,意味着不需要轨对轨的位线信号即可读出存储单元的数据。我们这里介绍第二个思路。因存储器阵列的相似结构,读出放大器不仅在SRAM中使用,在其他种类的存储器如动态随机存储器(DRAM),闪存(Flash Memory)中也得到广泛使用。从上面的简介我们可以得到推出读出放大器应该具有的特性:1.高速;2.面积小(SRAM可以有1000个以上的读出放大器);3.低功耗。然而,我们知道FET的参数如阈值电压在制造完成前可以看成随机变量,无法控制。而在数量庞大的读出放大器的客观条件下,我们无法对单个读出放大器的偏移电压(offset voltage)做校准(calibration),这一点与锁存型放大器在数据转换器和高速有线通信中的应用非常不同,因此我们必须使用结构简单的低偏移读出放大器。

上述斜体转自https://www.jiqizhixin.com/articles/2017-10-30-13

标签:MOS,读出,存储器,唐朔飞,存储单元,位线,放大器 From: https://www.cnblogs.com/Inn0cent/p/16786243.html