作者:EE野蛮人

链接:https://zhuanlan.zhihu.com/p/406168077

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

SI前4篇,我们深入理解了下反射系数以及阻抗这两个东西。他们是SI的地基。接下来就到两样工具S参数和TDR。这个学习理解的先后顺序也是在经过一段时间摸索之后,觉得最能切入SI重点的顺序。这次我们重点聊下S参数,S参数是频域研究高频信号的一个重要的工具,前几篇也提到了当高频信号通过传输线的时候,传输线上每个点的电压电流都会随位置的不同而变化,所以研究传输线的时候不再能用集总式端口电压或者端口电流的方式,而是要把某一点的电压分成入射电压,反射电压分布参数来考虑。而S参数就是因此而产生。

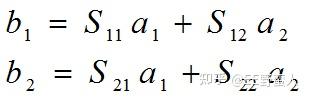

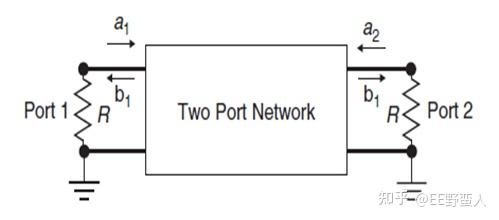

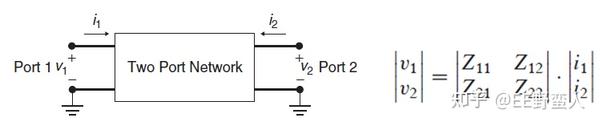

S参数里面听的最多的莫过于回损(RL)和插损(IL)。看一下S参数的定义,假设一个2端口网络:

首先注意这里的一竖线a2=0这么个表述,它在说什么呢?就是说端口2不能有额外进来的波,也可以理解为端口2没有反射(或者端口2阻抗匹配),不然端口1的S11就不是简单的b1/a1,因为有了个额外的a2会从端口1出来了啊。这个说法在SI第一篇,提SI的第一个问题的时候说在A点看过去没有反射的条件不单单是R=Zo,还必须要末端负载也等于Zo,可以回看一下“SI从一个问题开始”这篇。怎么样?是不是和这里的S参数定义倒是可以对应上了。其实S11=RL=-20log Γ\Gamma (反射系数),而反射系数经过前面几篇理解之后,我觉得应该也不会再狭隘认为是一个点两边的阻值或者特性阻抗简相减除以相加。还记得等效输入阻抗会周期变化嘛 ?

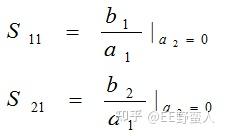

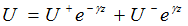

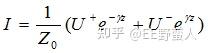

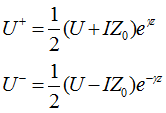

其次,那S参数里面的a和b究竟代表什么意思呢? 我们来说说,前几篇我们看到电压和电流在传输线上表现为下式:

如果把U+与U-当成变量反求:

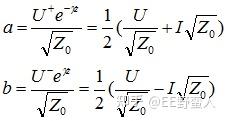

定义入射波a,散射波b:

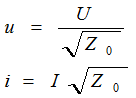

再定义一个“归一化”的电压波u,电流波i:

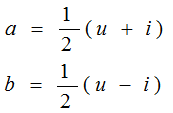

最后可以得到:

或者:

这是不是看出点东西了,入射波和散射波相加就是这点归一化的电压波,做减法就是归一化的电流波。

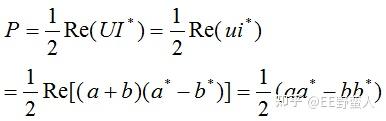

那么为什么要定义这么多归一化的东东,绕来绕去的,又有什么好处呢?看一下物理意义就了解了,信号的功率P:

Zo开根号正好可以约掉。最后发现信号功率正好可以简单的表示为入射波功率减去散射波功率。VNA仪器就是通过功率来测量S参数的,因为电压实在不好量。

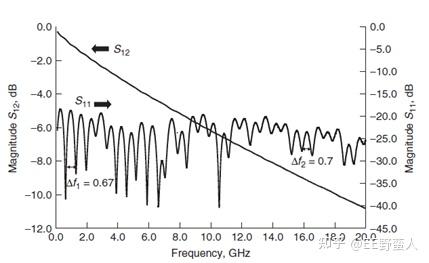

通常的S参数S11,S21是这样子的:S11负的越多表示回损约小,常规认为S11在-10dB以下是算还过得去的,当然能到-15dB以下就属于不错了。S21负的越少越好,表示更多的能量传了过去。

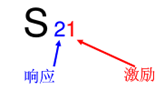

这个S下标的方向都是约定好的,特别强调一下,可不能搞错了,信号传输方向都是从后面那个数字的端口传入,从前面的数字的端口传出。

这次就先对S参数开个头,它里面可挖掘的内容还是很多的,后面再接着聊。

作者:EE野蛮人

链接:https://zhuanlan.zhihu.com/p/406911455

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。

- 前篇我们了解了回损可以描述一个端口上反射的情况。在实际应用中,我们有哪些措施可 以减小反射,落实在我们实际的PCB上呢?

a) 对于低速数字信号,可以使用始端串阻或者末端端接。这个在SI的第一篇就提到了。也是最常见的减小反射的措施,可以回看一下前面几篇。

b) 保证参考平面的完整,也就是信号回流的连续性。因为对于速率比较高的信号,它的回流电流都是从传输线下面最小环路电感的路径来进行回流的。

c) 优化走线拓扑。比较经典的比如I2C的菊花链拓扑,DDR地址线的菊花链拓扑等。貌似现在比较常用的还是菊花链,最后在链的末端可以添加RC端接,减小反射。具体波形可以用IBIS仿真。

d) 对于像如FPGA这样的器件,它的IO端口是可以调节设置驱动电流大小的。在遇到走线长度过长或者过短的时候,都可以适当调节驱动电流大小,比如4mA,8mA,12mA,16mA等,来优化信号质量。

e) 对于高速信号来说,比较常见的就是优化反焊盘(焊盘/换层过孔/连接器/),优化这些阻抗不连续点的反焊盘。Ansys HFSS用的很多。近几年又出来了一个HFSS 3D LAYOUT的新组件,可以直接导入PCB进行仿真,如果把HFSS比作C语言的话,那么3D LAYOUT就是C++。用起来更加快捷方便,但是HFSS操作最自由,但是没有那么快捷。

f) PCB背钻,之前PCB篇的时候就提过,这个工艺可以很好的减小信号过孔的STUB。当然背钻也无法使得stub=0。一般会有个2~8mil左右的精度的。

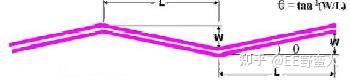

g) 蛇形走线

可能有时候会看到PCB上的一些高速线会这么不断的折返走线,这又是为什么呢?

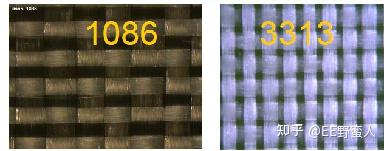

之前在PCB篇的时候,我们说过PCB叠层中间有介质层PP,它是一种玻纤布的东西做的,而这个东西放大了看是网状结构,如下图两种型号1086和3313的放大图,可以发现前面的网比较稀疏,后面的比较密,如果一根很长的走线直着走,那很有可能它的一半在玻纤布上,另一半一直在孔上面,这样就会导致阻抗和理论计算的值有较大偏差。当然这操作在速率不是特别高的时候也不用如此。有的PCB板厂也可以转动PP一定角度,这样线就不用这样子了。

2. 看了RL,那么IL插损如果在实际应用中尽量让插损小呢?

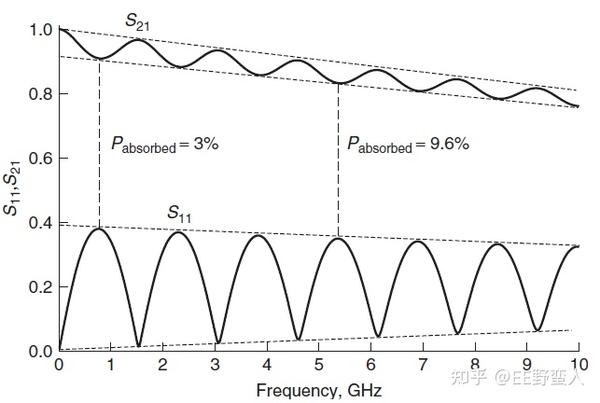

a) 其实RL和IL是 ,他们理论上相加等于1的,此削彼长。当然这个是系统自身没有损耗的时候,当然这只是理想状态。所以减小回损,自然插损也就会减小。

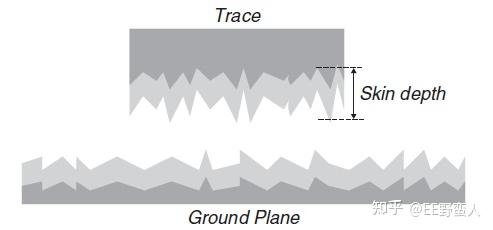

b) 由于趋附效应的存在,比如大家都是0.5OZ的铜厚,但是无奈信号速率一高,它的电流只存在下方特别粗糙的那一小段上。使用粗糙度比较低的铜箔,可以减小导体损耗。不同的PCB铜箔,它的粗糙度不同。高速PCB常用的像RTF,HVLP 粗糙度只有10um以下,普通的压延铜大约在20um左右。导体损耗上会比普通铜箔好很多。

c) 使用Dk Df低的高速板材,可以有效减少介质损耗。对于高速信号,介质损耗相对于导体损耗占主导地位。之前PCB篇里面提过的板材的一个图上面就把板材按照Df列了一个等级。越高速的板子,就需要选用Df越小的板材,这样才能保证链路在一定长度内损耗不至于达到接收端识别不到。可以回顾一下之前的文章。

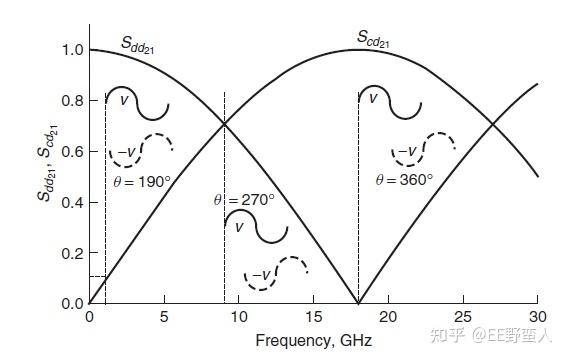

d) 抑制共模分量。在PCB走高速差分线的时候,保证差分PN之间等长是必要操作。那么如果不太等长的话,会出现什么情况呢? 这个会导致差模转共模,或者说共模转换的差分S参数分量变大,而差模差损会变差(差分S参数后面会提到)。

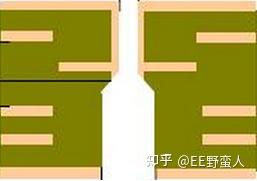

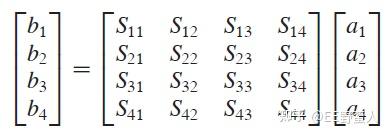

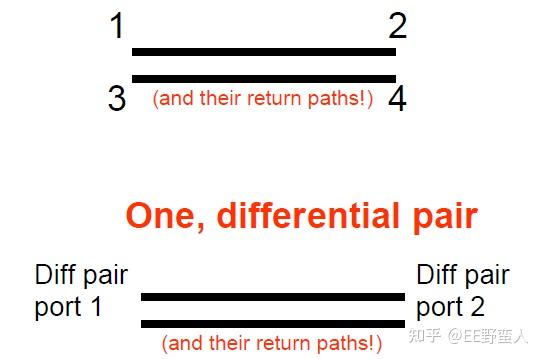

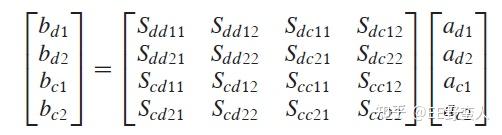

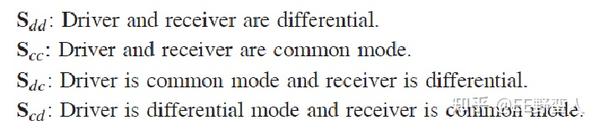

3. 混合模式S参数

把单线转换为差分S参数,如下面4端口S4p,经过转换之后,可以得到共模差模S参数。每对差分线变成两个端口,而不是4个端口。在高速差分信号中一般都会使用这种混合模式S参数而不是单端口S参数,因为在高速接口的电气协议里面也是按照差分S参数来规定Spec的。

这篇主要总结一下回损插损与PCB的在实际应用中的密切联系。

参考文献:

Advanced Signal Integrity For High-Speed Digital Designs STEPHEN H. HALL HOWARD L. HECK

紧接着上一篇,关于S-Parameter 可挖掘的内容还有很多。

4. 串扰

对于多条传输线,除了RL和IL之外,还会有线与线之间的耦合,也就是串扰,这个同样可以用S参数来表征。比如S31是近端串扰,S41是远端串扰。

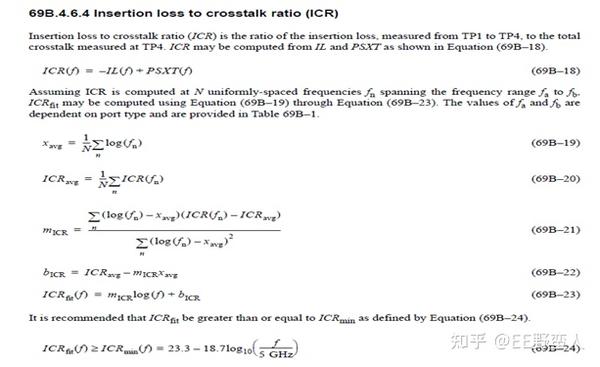

常见的使用场合:例如在仿真一组DDR的DQ线(并行总线)的串扰情况时,可以提取一组DQ线的S参数,然后用IBIS模型做源去仿真串扰。又或者有些高速接口Spec里有明确对串扰的指标要求,如下图是一个802.3网络协议中关于IL和Crosstalk比值有一个要求ICR。

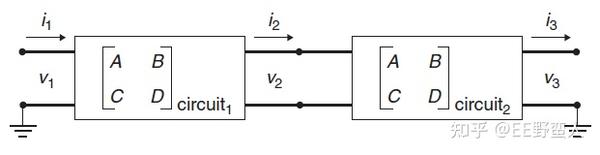

5. S参数的级联

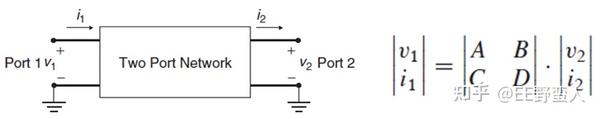

多段无源链路的S参数矩阵本身是无法直接级联的,因为看S参数的方向是对称的,而ABCD参数(以下简称A参数)以电压电流的方式表征网络端口,它是可以级联的。所以在S参数的级联需要通过A参数转换,级联之后再转换回S参数。

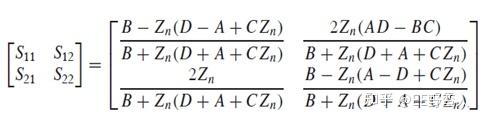

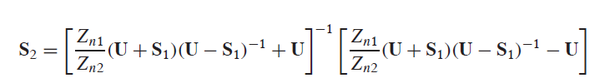

转换公式如下:注意级联S参数(一般使用仿真软件级联),最好归一化阻抗Zn保持一致。

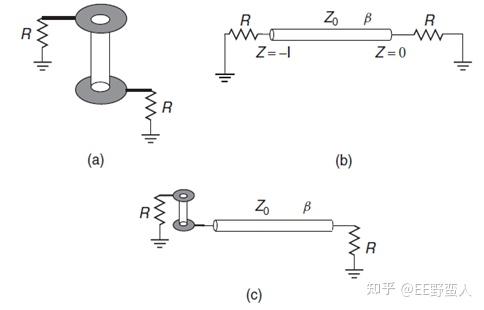

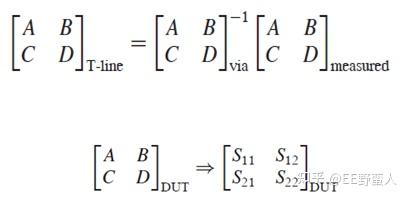

6. 去嵌(de-embed)

了解了S参数的级联之后,当我们做测试的时候,经常会听到“去嵌" 这个词。假设有一个过孔和一段传输线,我们测的了c图的S参数,但是我们只想得到b图(传输线本身)的S参数。那么我们如果有得到a图的S参数,就能把过孔从c中去嵌掉,得到真正的传输线的s参数。

去嵌其实就是一个乘以逆矩阵的操作,在c的总体的A参数左边乘以一个过孔的A参数的逆矩阵就可以得到真正的传输线的A参数,最后再转换回S参数。

7. S参数的参考阻抗变换

提到S参数,一定是基于某一个特定的参考阻抗才有意义。一般我们多是以50ohm,差分100ohm作为参考阻抗。不过它也可以根据需要转换成别的参考阻抗。

其中 S2是转换后的,S1是转换前的,U是单位矩阵,Zn1,Zn2分别是转换前和后的参考阻抗。

8. Z参数

前面提到一个A参数,但是其实常用的还有一个Z参数,S参数也可以转换成Z参数,特别是Z11,在电源完整性(PI)用的最多,主要是在PDN上使用。

Z和A参数的关系:

到此,一个简单的S矩阵,里面的内容如果深挖可以非常丰富,目前总结了8条。还有一条S参数转化到时域和TDR,后面单独做一个话题。

参考文献:

Advanced Signal Integrity For High-Speed Digital Designs STEPHEN H. HALL HOWARD L. HECK

在得到某一个无源链路的S参数之后,无论链路是一段传输线,还是一个连接器,还是一个过孔等等,或者是很多部分的组合。这时从S参数的角度关心整个链路的回损或者插损就足矣,把链路当成一个黑盒。但是如果S参数指标差的时候,比如我们经常最关心的S21,想着插损不行,第一反应也许就会去看看回损怎么样?毕竟反射如果大,插损会变不好。但是有时候,比如内部阻抗不连续点,距离s参数的端口比较远,也许反射回来的能量在途中已经消耗殆尽,都体现不到S11上面去,让人觉得S11还不错,误以为反射不大。这个时候就需要TDR来助力了解整个链路上的阻抗突变情况了。不管是仿真还是测试中TDR都是经常用来诊断无源链路的一个手段,毕竟往大了说SI问题约等于阻抗匹配问题。

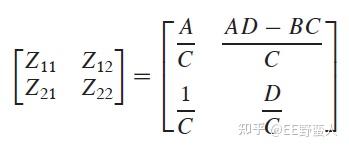

TDR可以通过时域的TDR设备去测试,也可以通过先测得S参数,然后通过S参数的傅里叶反变换得到。先说说直接由TDR时域去测得。

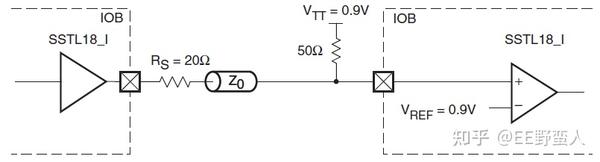

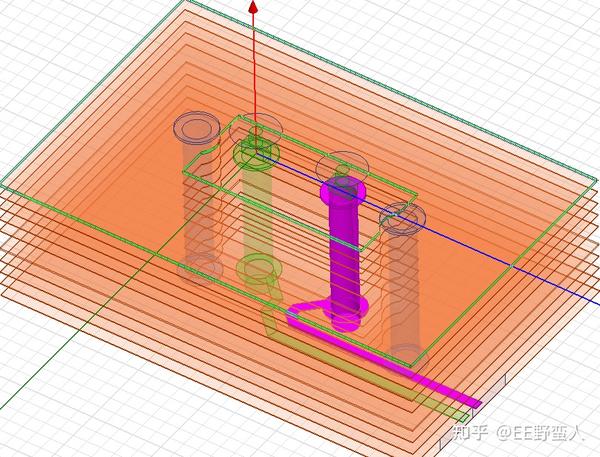

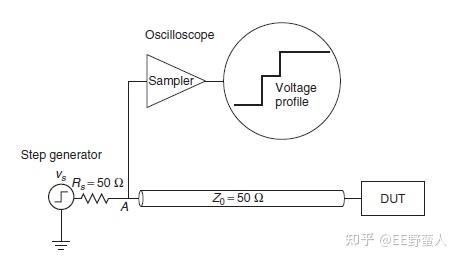

TDR设备简单的模型如下图,是由一个step信号的激励,通过cable,连接并注入到DUT上去。这里的源有源阻抗50ohm,cable的特性阻抗一般为50ohm。然后TDR内部采集A点的电压,最后得到DUT的TDR曲线。

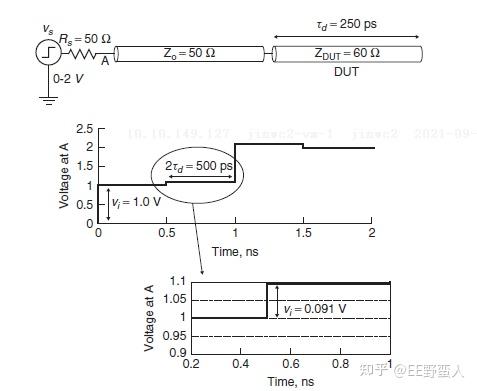

这里假设DUT是一段250ps延迟的60ohm特性阻抗的传输线。输出的源为2V的Step信号,在A点测量到的电压曲线图如下,凭借A点的电压波形就可以计算得出后面DUT的阻抗信息,怎么来的呢?

假设Zo和Zdut交界点的位置的入射电压和反射电压分别是Vi,Vr。则由反射系数的公式:

Vr/Vi=(Zdut-Zo)/(Zdut+Zo);则Zdut=Zo*(Vi+Vr)/(Vi-Vr)。由上图中我们可以看到Vr是等于0.091V。而Zdut=50*1-0.091/1+0.091=60。

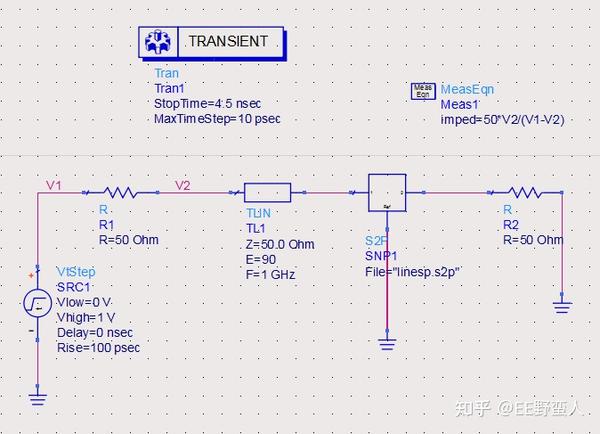

这个也可以在ADS中仿真,如下图,假设有一个待测物DUT用s参数表示,在前面有一个step信号源,内阻也是50,再接一小段50ohm特性阻抗的延迟线。最后的TDR可以用公式50*V2/(V1-V2)来获取。那怎么跟上面的Zdut=Zo*(Vi+Vr)/(Vi-Vr)保持一致的呢?具体推导一下:

Zdut=Zo*Vi+Vr/Vi-Vr

=Zo*(V1/2+Vr)/(V1/2-Vr)

=Zo*V2/(V1/2+V1/2-(V1/2+Vr))

=Zo*V2/(V1-V2)

在瞬态的时候,因为R1=Zo=50,所以Vi=V1/2。

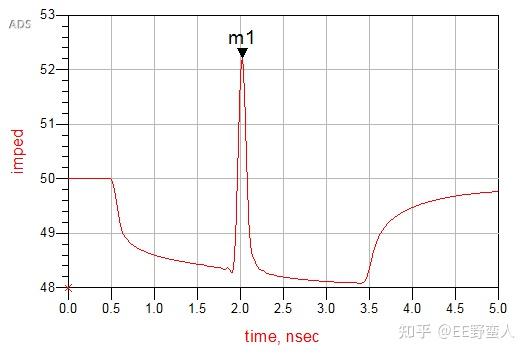

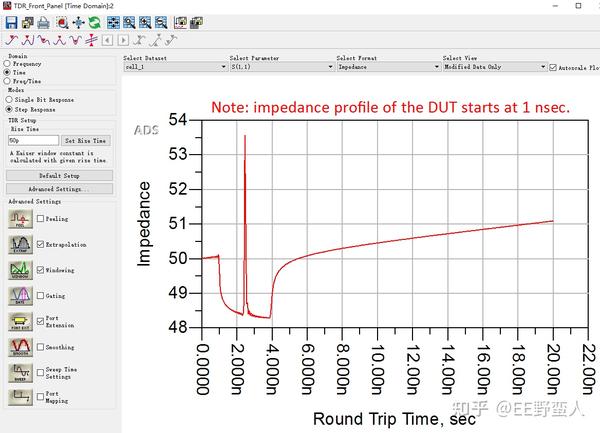

最后的仿真如下,这个DUT只是做实验用的一个两段5inch 48ohm传输线中间有一小段52ohm传输线。

另外从TDR图像里也可以估算出链路上不同阻抗的段的长度,比如上图,前段48ohm的线,5ich的线,按照6mil/ps的传播速度,然后波传播来回两倍的传输距离,能得到大约需要用1.66ns,跟图上的时间差不多可以吻合。

还有一个需要注意的是Step上升沿时间的设置,如果设置的太长,会影响TDR的分辨率,导致一些短的阻抗不连续点被淹没,一般认为这个上升时间内传播的距离就是TDR的分辨率,要求上升沿的信号带宽最好能有5倍的实际使用的信号最高频率。

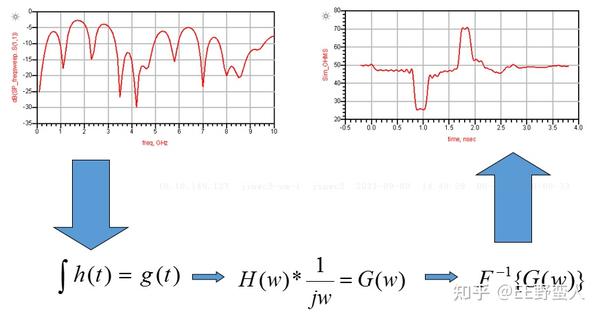

当然要得到TDR,除了从时域瞬态角度去得到,还可以从频域角度,直接从S参数得到。无论是S11,还是S21,这里都可以把被测无源链路当成是一个LTI系统。S11可以理解为从1端口输入入射波,从1端口输出反射波。而S21可以理解为从1端口输入入射波,从2端口输出透射波。这都是一个LTI系统的响应,而描述一个LTI系统一般都是用h(t)冲击响应来描述其特性,当冲击响应积分就得到阶跃响应。下图是S11获得TDR的示意过程,S11在频域做积分就是*1/jw。然后再做IFT,就能得到TDR。

在ADS中也有类似工具SP-TDR,或者函数提供调用,如下图是之前用过的S参数直接通过SP-TDR转换到时域的TDR曲线,结果与时域Step信号仿真放大得到的吻合。

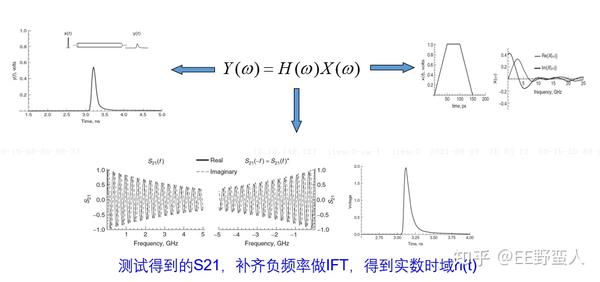

对于S21也可以做IFT,如下图,无源通道S21做IFT然后和输入信号,就如下面的一个梯形(类似于数字信号的的一个UI),两者频域相乘(时域卷积)得到最终输出的波形Y(t)。在IBIS-AMI仿真的时候就利用了这个原理生成static eye diagram。

回到TDR,当直接用S11去变换得到TDR的时候,它的TDR分辨率,由S参数的最高扫频频率决定。我们一般也是最好取最高扫频频率是5倍的实际信号最高频率,这样可以对不连续点看的更加清楚

标签:解释,Zo,传输线,端口,SI,参数,PCB,TDR From: https://www.cnblogs.com/FROMRPITO0/p/17762604.html