摘要

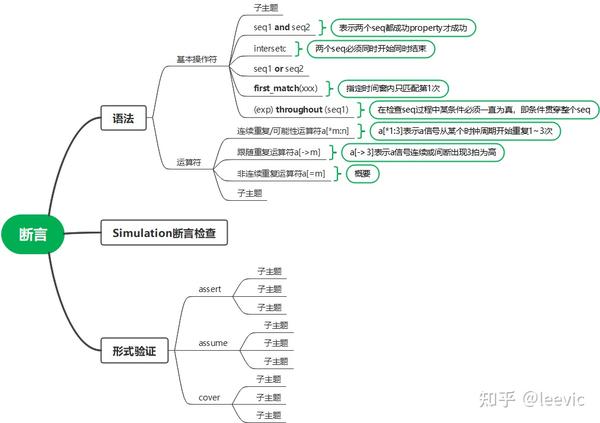

SystemVerilog断言(SVA)可以直接添加到RTL代码中,也可以通过bindfiles间接添加。实践表明,最好使用bindfiles添加大多数断言。 这篇论文将解释为什么将断言直接添加到RTL代码会带来问题,以及为什么bindfiles解决了很多问题解决了什么问题。 本文还解释了如何有效地使用bindfiles,以及为什么工程师通常应该使用并发断言同时避免使用立即断言。 论文还将提供断言编码的指南和示例,来帮助减少断言编码工作量和断言编码错误,并鼓励设计人员更加主动的针对设计添加断言。

4 Bindfiles

准则#2:绑定文件——使用它们!

准则#3:内联 SVA 代码 - 避免它!

本节将描述绑定文件的使用,并解释为什么我不鼓励放置断言直接在 RTL 代码中。

有许多来源建议将断言直接嵌入到 RTL 代码中,但是 再次,我相信有更好的方法。 哈里·福斯特(Harry Foster),第一本基于断言的作者 设计书籍,曾经推荐将断言直接放入 RTL 代码中,但现在他 建议不要将断言放在 RTL 代码中,并且 Harry 和我一致认为 断言应该放在单独的绑定文件中。 哈利和我给出了基于断言的 2010 年在北美和欧洲的验证研讨会,我们分享了 SVA 最佳编码 练习技巧,包括正确使用绑定文件。

4.1 How bindfiles work

一般来说,使用bindfiles其实就是在做间接实例化。 工程师将绑定(间接实例化)使用 bind 关键字在另一个模块内的一个模块。 IEEE Std 1800-2012 标准经常将绑定文件称为“bind_instantiation”。[8]

待更新。。。

标签:bindfiles,断言,RTL,代码,绑定,使用,SystemVerilog From: https://www.cnblogs.com/amxiang/p/16749296.html