1)https://zhuanlan.zhihu.com/p/163300131

2)https://www.xilinx.com/support/documentation-navigation/design-hubs/dh0070-zynq-mpsoc-design-overview-hub.html

尤其ug1085

ZYNQ UltraScale+ MPSoc FPGA初学笔记

IEEE1364

人在江湖身不由己

IEEE1364

人在江湖身不由己

前言

最近要做新的设计用到Xilinx ZYNQ UltraScale+ MPSoc系列的芯片。文档看到吐,阅读间隙和妹子聊天,还被吐槽太闲。人生不易,我决定把近几日所学,整理成一篇文章,让大家少走点弯路,少被妹子吐槽。

一、ZYNQ UltraScale+ MPSoc的EG系列

Xilin的FPGA芯片主要分为两大类FPGA和SOC系列,FPGA产品就是我们以前比较熟悉的Spartan、Artix、Kintex和Vertex系列的产品,是纯逻辑产品,有不同的逻辑规模、速度等级和制程。SOC就是将FPGA和处理器单元以及常见处理器外设封装在一起,试图以单芯片解决整个控制部分的设计,Xilinx冠之以ZYNQ的名字。比较常见的ZYNQ-7000系列,便宜、够用,灵活性大,很多工业场合都会使用。

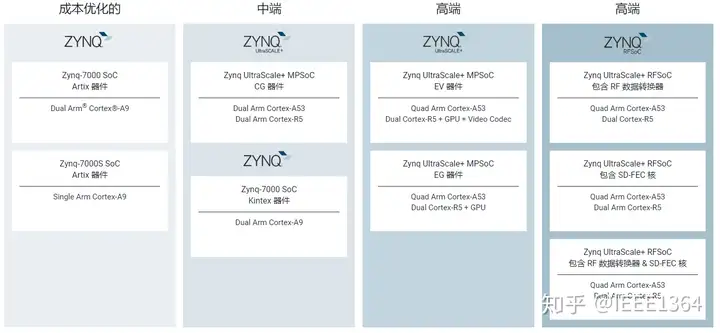

下图就是ZYNQ系列的图谱。他们的主要区别在于处理的数量和逻辑规模的大小,越高端的系列集成了数量越多等级的越高的ARM核,高端的里面还有一个RFSoc系列,集成了射频的数据转换器,可能是针对雷达和通信系统的。

高端系列里面的UltraScale+ MPSoc有EV和EG两个系列,EV系列比EG系列多一个Video Codec,可以用来进行更高效的视屏处理,我们今天为例学习的XCZU19EG属于EG系列,它有四核Arm Cortex-A53和双核Cortex-R5。

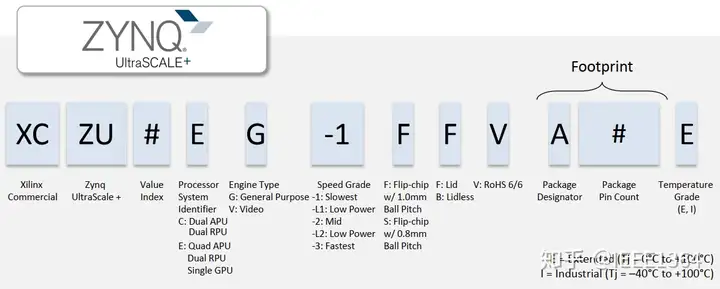

MPSOC系列芯片名字太长了,刚上来根本他喵的记不住啊,首先我们看一下这个系列的命名规则,简单记忆之后我们大概能根据芯片的名字得出芯片的基本信息,包括封装、速度等级、工作温度等。

二、UltraScale+ MPSoc EG系列概要

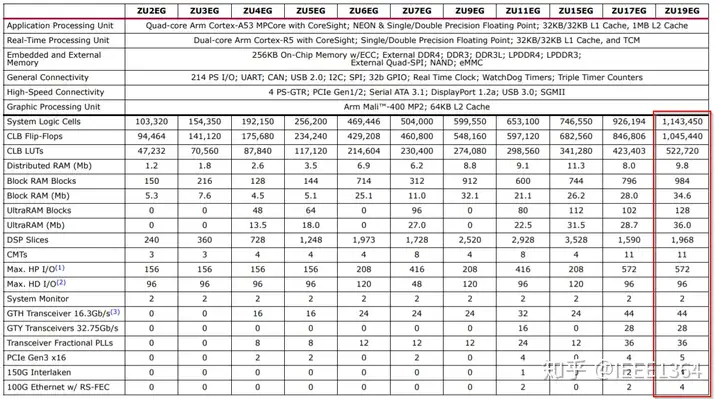

首先,来我们看一下我们选择的这块芯片的内部资源。

Huck,是不是很惊喜,根本不知道这些都特么是啥啊,我该怎么用啊。没事,我也是从一团雾水,慢慢搞清楚的。

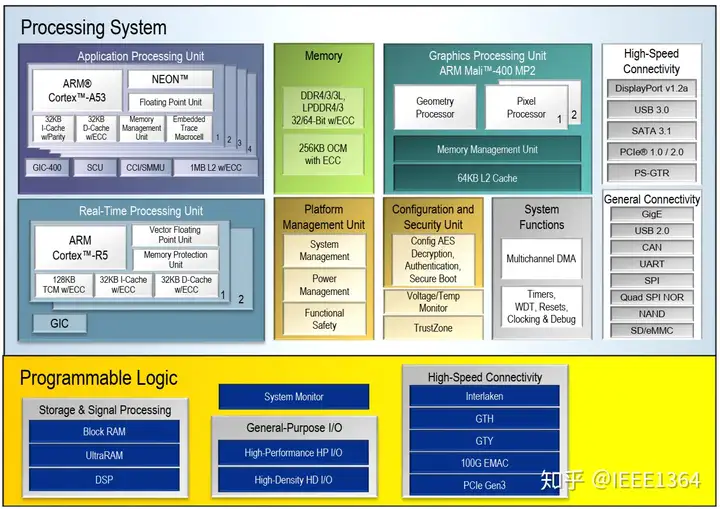

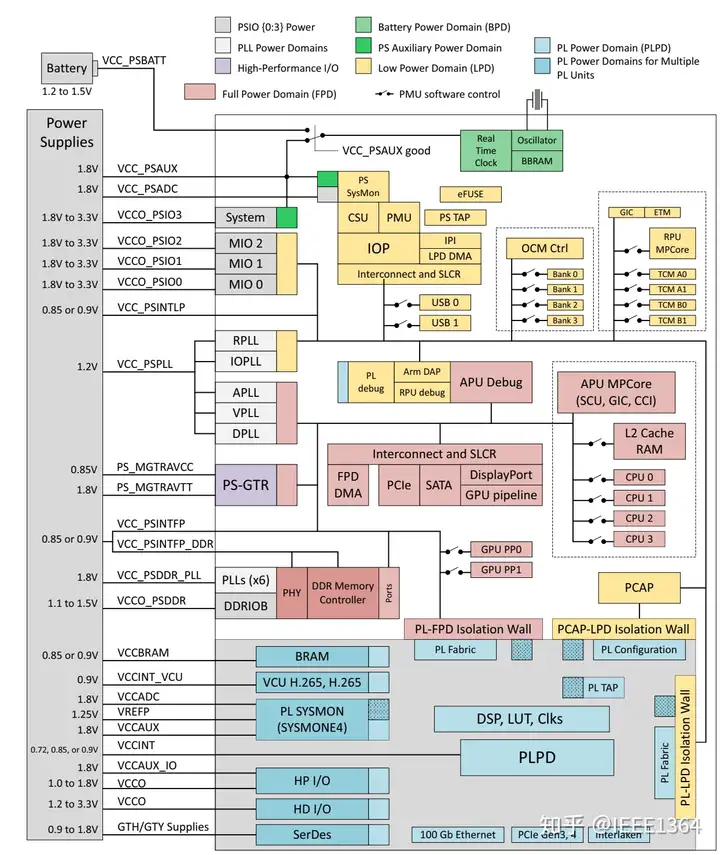

我们先看一下系统内部资源模块图。<DS890>

这样一看是不是清晰很多,这个芯片分为PS(Processing System)和PL(Programmable Logic),就是处理器部分和逻辑部分。处理器部分比较复杂,除了各种Arm核之外,还有GPU、DDR控制器,当然也集成了我们常见的外设DMA、Watch Dog和各种各种常见的高速接口。PL部分就相对简单,主要是处理计算、高速连接和IO。PS和PL部分各自集成了一个10bit的ADC来进行系统监测,称之为System Monitor。

从硬件工程师的角度,我将分IO、电源、时钟与复位和外设四个部分来介绍EG系列的芯片,其中时钟与复位和外设部分会放到另外一篇或者几篇文章进行讲述。

三、IO

MPSoc系列的芯片都很复杂,比如XCZUxxxx-2FFVC1760E有1760个管脚,刚上来的时候看到原理图我差点哭出声,但是我忍住了,不能弄脏我新配的眼镜。

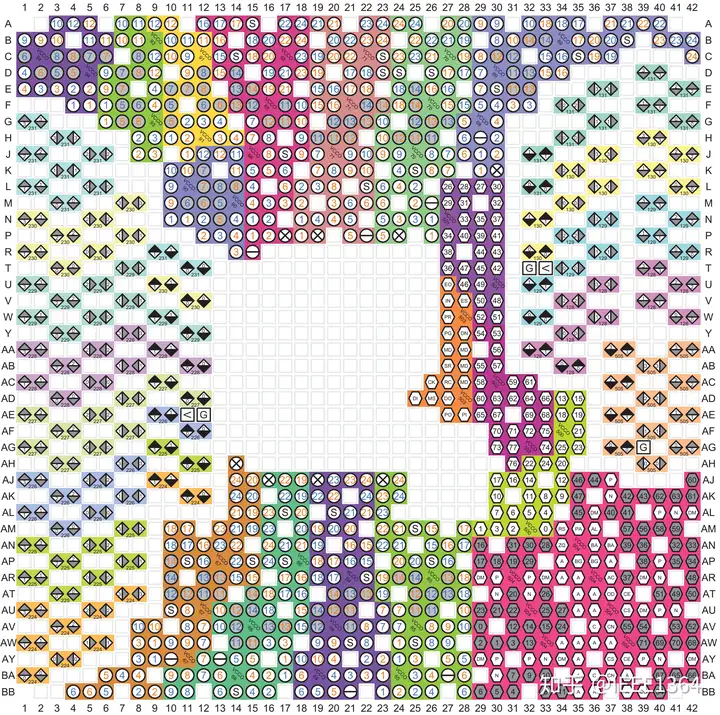

<UG1075>

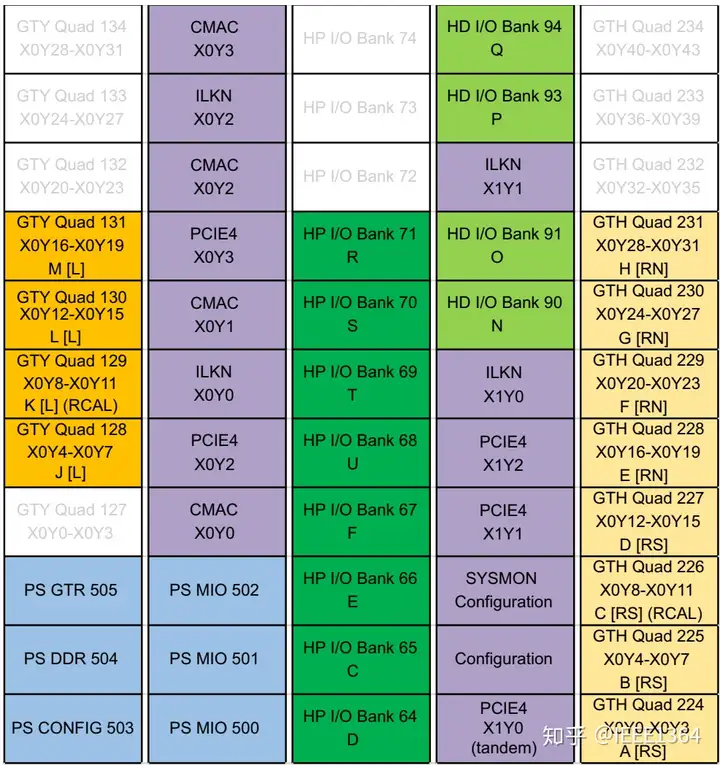

官方文档给出了一个分类图,花花绿绿的一顿操作,然鹅,我们并不知道它有哪些东西。

<UG1075>

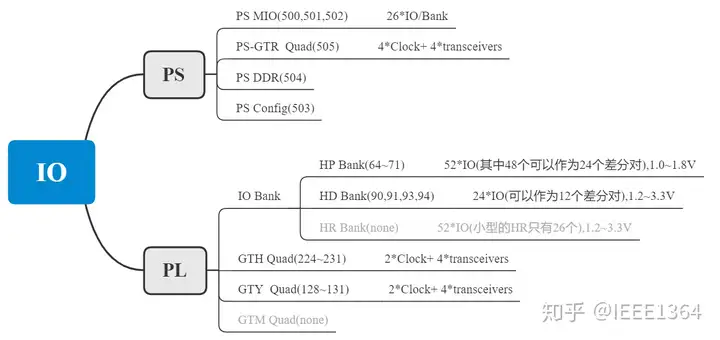

经过一番努力,我做出了下面这张脑图,原创,建议打赏然后收藏。

说明:为了便于记忆每个IO Bank后面括号里的数字代表XCZU19EG所拥有的Bank号,方便你看到bank好的时候知道这个bank所在的分类。

3.1 IO分类

IO由一个个Bank组成,首先要分成PS和PL两部分。PS的部分可以分为以下四个部分:

1.PS MIO,即Multi-function IO。每个bank有26个IO,一共三组,这些IO就是支撑了常见的外设如串口、I2C、SPI等,也可以支持SD卡、NAND和eMMC的接口。

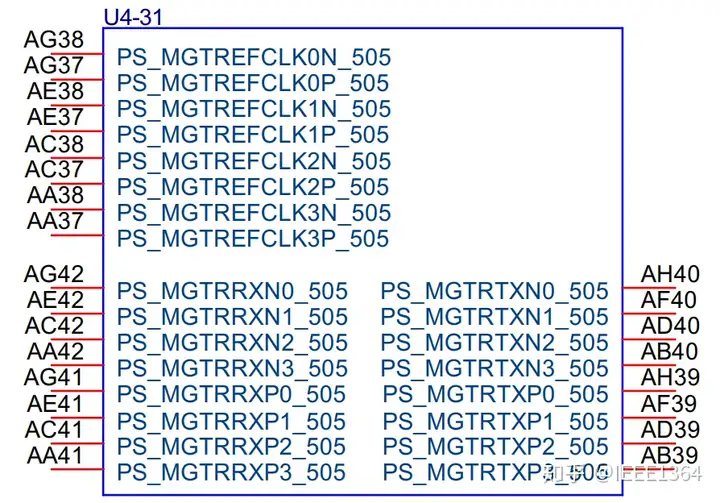

2.PS-GTR。这是PS的高速收发器bank,有四对高速收发器和四对时钟,可以支持我们常见的各种高速接口,PCIE、DP、USB、SATA等,需要用到高速收发器的接口。

3.PS DDR。这是DDR controller的接口,支持ECC功能,不在此详述。

4.PS config。配置端口,JTAG就是在这里,模式设置、参考时钟、复位和错误指示等接口都在这里。

PL分为两大类,IO Bank和高速收发器。

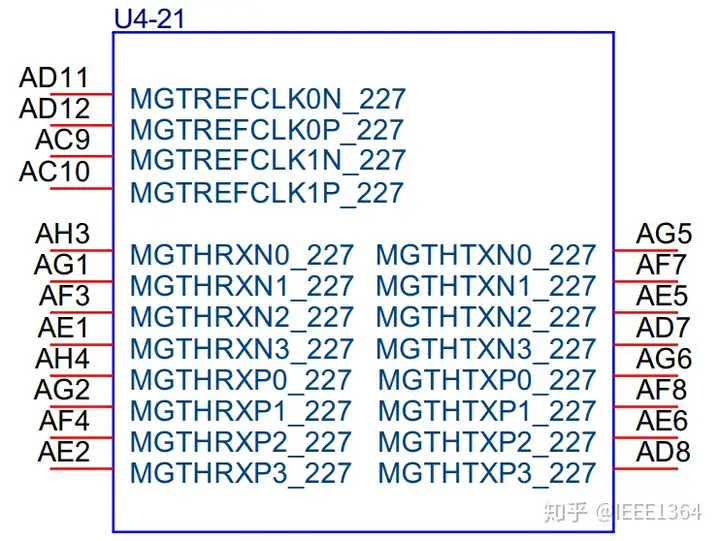

高速收发器分为GTH、GTY和GTM,他们的主要区别是传输速度,每组我们成为一个Quad,一个Quad有四个收发器差分对和两个时钟差分对。我们所选的芯片没有GTM收发器。

IO Bank分为HP、HD和HR三类。

1. HP,High-performance,旨在满足高速存储器和其它芯片对芯片接口,工作中电压1.0V到1.8V每组52个IO,其中48个可以作为24个差分对进行配置。

2. HR,High-range,旨在支持更广泛的 I/O 标准,工作中电压1.2V到3.3V,每个Bank有52个IO,有些小型的bank只有26个。我们所选的19EG没有该接口。

3. HD,High-density,旨在支持低速接口,工作中电压1.2V到3.3V,每组24个IO。

3.2 IO的供电电压

PS MIO、HP和GD的IO Bank有多个电压,以适应各种不同的逻辑电平和应用场合。

3.2.1 VCCO

VCCO 电源是 I/O 电路的主电源。特定 HP I/O bank 的所有 VCCO 管脚必须连接到开发板上相同的外部供电电压,因此,该 I/O bank 内的所有 I/O 的 VCCO电平必须相同。 VCCO 电压必须符合已分配给此 I/O bank 的 I/O 标准的要求。错误的 VCCO 电压可能会导致功能丧失或损坏器件。

3.2.2 VREF

带差分输入缓存的单端 I/O 标准需要输入参考电压 (VREF)。如果 I/O bank 中需要 VREF,可将专用 VREF 管脚作为 VREF 供电输入(外部),或者使用内部生成的 VREF (INTERNAL_VREF 或 VREF 扫描(仅限 HP I/O bank))。使用INTERNAL_VREF 约束即可启用内部生成的参考电压。

在 I/O 标准需输入参考电压并使用内部生成的 VREF 的 bank 中,使用500Ω 或 1K 电阻将 VREF 管脚连接至 GND。如果无需输入参考电压,可以用500Ω 或 1KΩ 电阻将VREF 管脚接地,也可以保持浮空。

HP I/O bank 中提供了内部 VREF 扫描功能,以适应工艺变化或系统考虑因素。

3.2.3 VCCAUX

全局辅助 (VCCAUX) 供电轨主要用于为器件内部各个块的互联逻辑供电。在 I/O bank 中, VCCAUX 还用于为某些 I/O 标准的输入缓存电路供电。其中包括部分不高于 1.8V 的单端 I/O 标准,以及部分 2.5V 标准 (仅限 HR I/O bank)。此外,VCCAUX 供电轨还为大多数差分 I/O 标准和 VREF I/O 标准中使用的差分输入缓存电路供电。

3.2.4 VCCAUX_IO

辅助 I/O (VCCAUX_IO) 供电电压轨用于为 I/O 电路供电。 VCCAUX_IO 只能按 1.8V 标准供电。

3.2.5 VCCINT_IO

这是 I/O bank 的内部电源。连接至 VCCINT 供电电压轨。

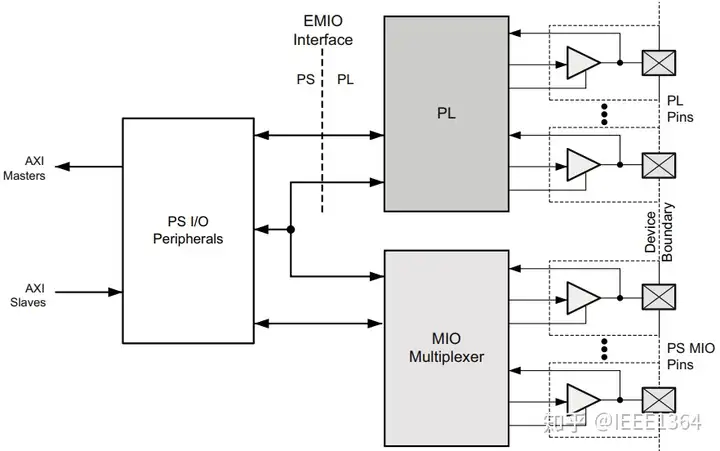

3.3 MIO and EMIO

PS端有三组MIO可供各种外设使用,当这些IO不够用的时候我们可以调用PL端的IO,这些IO叫 EMIO(extended multiplexed I/O )。PL端的EMIO可以通过PL逻辑连接到EMIO interface上,然后被PS端访问。所以PS端有6组I/O接口,3组MIO和3组EMIO。

3.4小结

SOC FPGA的IO相比MCU和普通SOC的IO要复杂很多,主要是因为要支持高速的、低速的各种逻辑电平的接口。但是只要分类清楚理解起来并不难,当然还有更多的细节需要自己去看数据手册。

四、电源

与IO一样复杂的还有电源系统。电源系统分为以下四个域:

1.Low-power domain (LPD).

2.Full-power domain (FPD).

3.PL power domain (PLPD).

3. Battery power domain (BPD).

每个电源域都可以单独隔离。工作在LPD域上的平台管理单元(PMU)管理着每个电源域。当相应电源域的电源之一意外掉电时,可以自动打开隔离。 由于每个电源域都可以单独隔离,因此可以实现功能隔离。

4.1电源结构

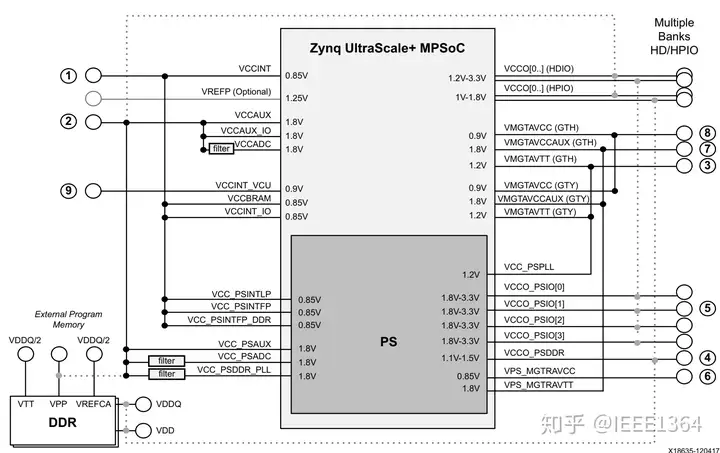

芯片电源结构如下图:

Power Domains and Islands (UG1085)

上图涉及了太多的电源轨,有着不同的电压和噪声要求。为了简化电源设计,我们可以使用下面的电源方案。

(UG583)

4.2 电源上电时序要求

PS 和 PL 电源为彼此完全独立的电源。所有 PS 电源均可在任意 PL 电源之前或之后上电。 PS 和 PL 电源区域已隔离以防止损坏。 (DS925)

4.2.1 PS 上电/断电电源时序

低功耗域 (LPD) 正常运作后, 全功耗域 (FPD) 方可正常运行。低功耗域和全功耗域可同时上电。按上电顺序运行期间, PS_POR_B 输入必须断言为 GND(请参阅表 37) 。使用 FPD 时, 它必须先上电, 然后才能释放PS_POR_B。

LPD推荐上电顺序:

1. VCC_PSINTLP

2. VCC_PSAUX、 VCC_PSADC 和 VCC_PSPLL, 按任意顺序或同时执行。

3. VCCO_PSIO

这样做可以实现最低电流汲取并确保上电时 I/O 处于三态状态。下电顺序反过来即可。

FPD)推荐上电顺序:

1. VCC_PSINTFP 和 VCC_PSINTFP_DDR 从相同供电电源驱动。

2. VPS_MGTRAVCC 和 VCC_PSDDR_PLL, 按任意顺序或同时执行。

3. VPS_MGTRAVTT 和 VCCO_PSDDR, 按任意顺序或同时执行。

旨在实现最低电流汲取并确保上电时 I/O 处于三态状态。下电顺序反过来即可。

4.2.2 PL 上电/断电电源排序

推荐上电顺序:

1. VCCINT

2.VCCINT_IO/VCCBRAM/VCCINT_VCU

3. VCCAUX/VCCAUX_IO 和 VCCO,

这样即可实现最低电流汲取并确保上电时 I/O 处于三态。下电顺序反过来即可。

如果 VCCINT 和 VCCINT_IO/VCCBRAM 的推荐电压电平相同,那么可使用相同电源为其供电并同步执行缓升。 VCCINT_IO 必须连接到 VCCBRAM。

如果 VCCAUX/VCCAUX_IO 和 VCCO 的推荐电压电平相同, 那么可使用相同电源为其供电并同步执行缓升。 VCCAUX 和 VCCAUX_IO 必须连接在一起。

VCCADC 和 VREF 可随时上电,无上电顺序要求。

为 GTH 或 GTY 收发器实现最小电流汲取的推荐上电顺序为

1.VCCINT

2. VMGTAVCC

3. VMGTAVTT 或 VMGTAVCC

4.VCCINT

5. VMGTAVTT

针对VMGTVCCAUX 不存在推荐的排序。

VMGTAVCC 和 VCCINT 均可同时执行电源缓升。

如果不满足这些推荐的顺序, 那么上电和断电期间从 VMGTAVTT 汲取的电流可能高于相应的规格。

4.3小结

电源的复杂度是随着系统的复杂同步上升的,后面在实际设计的时候应该还会遇到不少问题,到时我再补充文章进行说明。

五、参考文档:

DS890, UltraScale™ Architecture and Product Overview

DS891, Zynq® UltraScale+™ MPSoC Overview

DS925, Zynq UltraScale+ MPSoC Data Sheet: DC and AC Switching Characteristics

UG1075, Zynq UltraScale+ MPSoC Packaging and Pinouts

UG1085, Zynq UltraScale+ MPSoC Technical Reference Manual

UG571, UltraScale Architecture SelectIO™ Resources User Guide

UG574, UltraScale Architecture Configurable Logic Block User Guide

UG578, UltraScale Architecture GTY Transceivers User Guide

UG583, UltraScale Architecture PCB and Pin Planning User Guide

后记

未经整理的信息不足称为知识。我喜欢把看到乱七八糟的信息梳理成一篇有逻辑有体系的文章,节约大家学习的时间,让读者仅通过看一篇文章就对某块知识有个相对系统的了解,而这也是我深入学习的基石,我后续的学习只需要在此基础上丰富更多的细节,新学的任何知识都是有坐标体系的,不会混乱糊涂。

这依然属于自学笔记系列,属于我初涉领域,如有资深人士看到错讹之处,还请指教!

欢迎各位大佬打赏,将来聊上妹子了,也有点零花钱请人家吃个高档一点的餐厅。。。

标签:PS,soc,UltraScale,电源,zynq,IO,资料,VREF,bank From: https://www.cnblogs.com/e-shannon/p/17447111.html