时钟之间的关系在静态时序分析(STA)中起着至关重要的作用。由于

1)时钟数量增多

2)不同的时钟产生电路

3)时钟域交互之间的交互

当前ASIC设计具有高度复杂的时钟方案。高效率的时钟关系约束才能产生高效率的STA。

一个设计中可以存在许多时钟。但是,并非所有时钟都相互交互。必须向STA分析工具声明这些时钟之间的关系,以防止分析这些时钟之间的路径。因为默认情况下,所有时钟域都是同步的。

对于异步时钟,当我们书写SDC时,可以使用set_false_path语句来指定由于异步时钟导致的timing exceptions。

set_false_path-from [get_clocks CLKA] -to [get_clocks CLKB]].

只能指定单方向路径的timing exceptions。如果需要指定双向的timing exceptions,则需要

set_false_path -from [get_clocks CLKA]-to [get_clocks CLKB]]

set_false_path -from [get_clocks CLKB]-to [get_clocks CLKA]]

现在有一种更有效的方法来指定设计中的异步时钟关系。 set_clock_groups是一种在Synthesis、P&R和STA工具中指定设计中时钟关系更加有效的方法。

set_clock_groups -asynchronous -group CLKA-group CLKB

此命令有三个选项。

-asynchronous,

-logical_exclusive

-physically_exclusive。

-asynchronous

两个(或多个)时钟是异步时,这意味着它们之间没有相位关系。

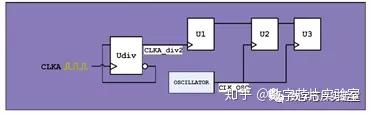

set_clock_groups –asynchronous –name my_ASYNC -group {CLKA CLKA_div2} -group {CLK_OSC}

工具不会分析CLKA 和CLK_OSC、CLKA_div2 和 CLK_OSC之间的时序,但是会分析他们之间的Crosstalk。

上述命令意为:

1. CLKA和CLKA_div2相互同步

2. CLKA&CLKA_div2和CLK_OSC相互异步

每个group里面的clocks相互同步,group之间的clocks相互异步

上述,命令等价为

set_false_path-from [get_clocks CLKA] -to [get_clocks CLK_OSC]

set_false_path -from [get_clocks CLKA_div2] -to [get_clocks CLK_OSC]

set_false_path-from [get_clocks CLK_OSC] -to [get_clocks CLKA]

set_false_path-from [get_clocks CLK_OSC] -to [get_clocks CLKA_div2]

-logical_exclusive

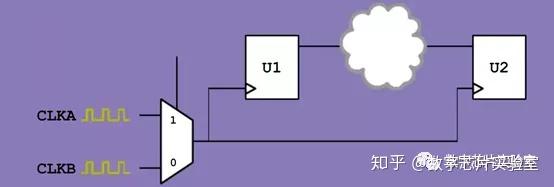

当设计中存在两个时钟,但它们之间没有任何路径时,可以说这两个时钟在逻辑上是互斥的( logically exclusive )。

例如下面的示例,通过一个MUX选择两个或多个时钟中的一个。这样的时钟之间将没有任何时序路径。

set_clock_groups – logically_exclusive –name my_MUXED -group {CLKA} -group {CLKB}

上述约束等价于:

#solution 1: set_case_analysis

# mode 1

set_case_analysis 1 [get_portsSEL]

# mode 2

set_case_analysis 0 [get_portsSEL]

#solution 2: use false path

set_false_path-from [get_clocks CLK1] -to [get_clocks CLK2]

set_false_path-from [get_clocks CLK2] -to [get_clocks CLK1]

工具会分析他们之间的Crosstalk

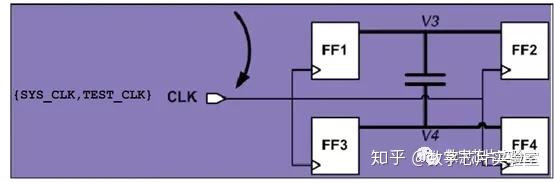

–physically_exclusive

如果时钟不在设计中同时存在。例如时钟在同一主端口上定义,但工作在两种不同的模式下。这些时钟之间将没有SI交互。

set_clock_groups –physically_exclusive -group {SYS_CLK} -group {TEST_CLK} # use physically exclusive

可以通过remove_clock_groups删除clock_groups声明

在大型设计中,可能有数百或数千个时钟。如果使用“set_fase_path”,则每个时钟对将需要2个约束,那么约束的语句将成倍增长!

使用“set_clock_groups”和“set_fase_path”在时序分析效果上一样,但是更干净,更易于维护。

标签:set,false,get,CLKA,clock,clocks,path,时钟 From: https://www.cnblogs.com/amxiang/p/16890855.html